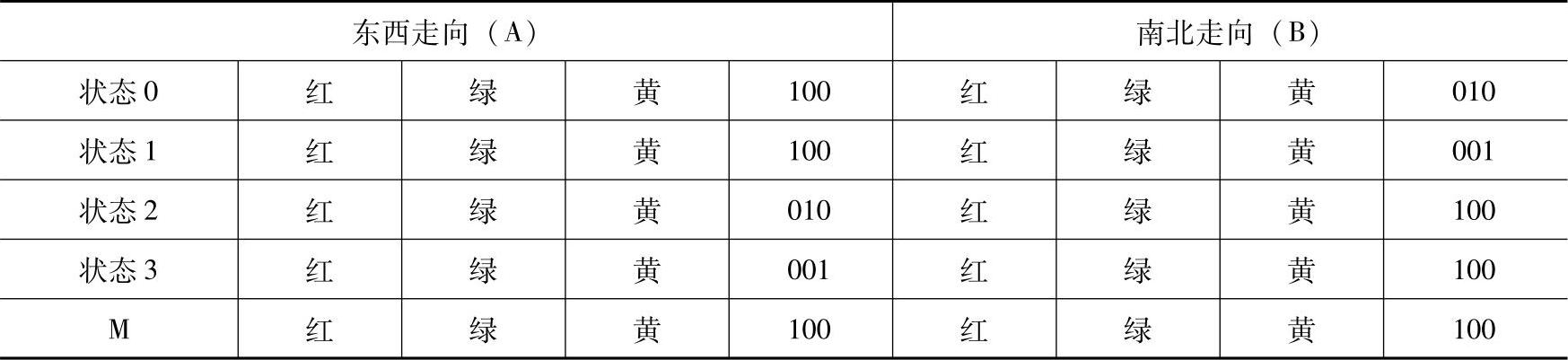

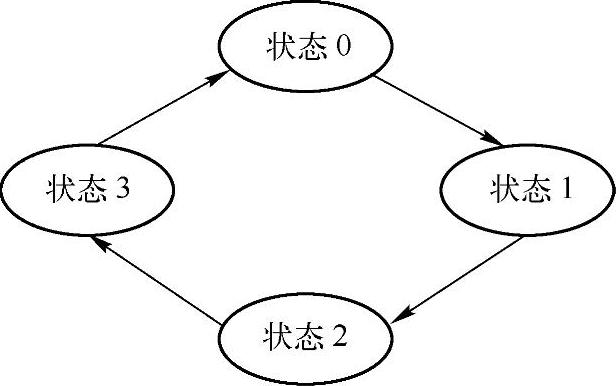

十字路口的交通灯控制系统,用实验平台上的发光二极管显示车辆通过的方向(东西(A)和南北(B)各一组),用数码管显示该方向的剩余时间。要求:工作顺序为东西方向红灯亮45s,前40s南北方向绿灯亮,后5s黄灯亮。然后南北方向红灯亮45s,前40s东西方向绿灯亮,后5s黄灯亮。依次重复。有紧急事件时两方向均为红灯,车辆禁行,比如十字路口恶性交通事故时,东西、南北两个方向均有两位数码管停止工作。表5-12中给出了交通灯控制器的4种状态和紧急情况M,当M=0时交通灯正常工作,正常工作时4种状态如图5-22所示。

表5-12 四种控制状态和紧急情况M

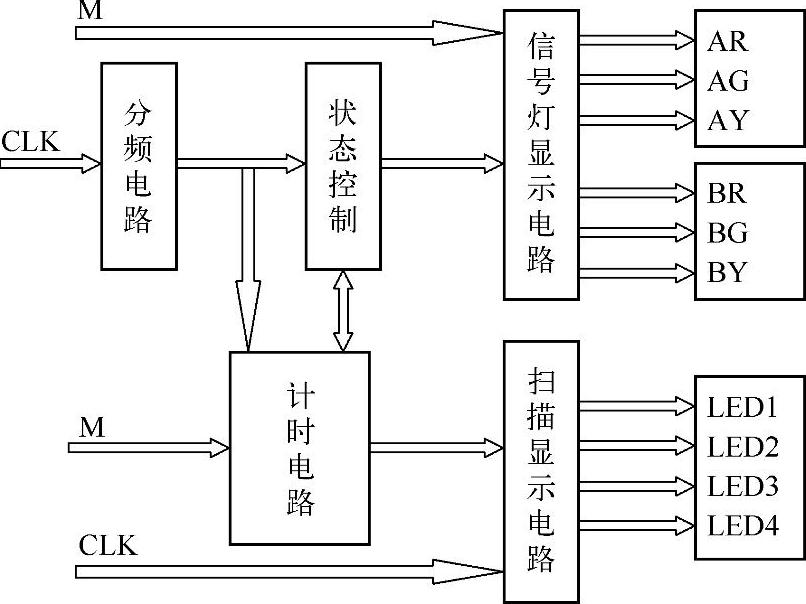

经分析该交通灯控制系统采用模块层次化设计,将此设计分为5个模块:分频模块、计时模块、状态控制模块、信号灯显示模块、数码扫描显示模块。将5个模块再分别用VHDL编写,做成原理图模块,用原理图输入法做整个设计的顶层文件。此方案设计方便、简单,方法易懂、易操作,也易于寻找程序中的错误。状态控制模块实现逻辑和时序控制,外部脉冲振荡器的频率选为100MHz的信号,分频得到的信号用于显示模块的扫描,1Hz信号用做倒计时模块的计数脉冲控制模块的时钟。M为紧急状态的控制端。系统总体框图如图5-23所示,其中,AR、AG、AY分别表示东西(A)方向的红、绿、黄灯;BR、BG、BY分别表示南北(B)方向的红、绿、黄灯;LED1、LED2、LED3、LED4分别代表东西和南北方向倒计时的数码管。

图5-22 正常工作时4种状态图

图5-23 系统总体方框图

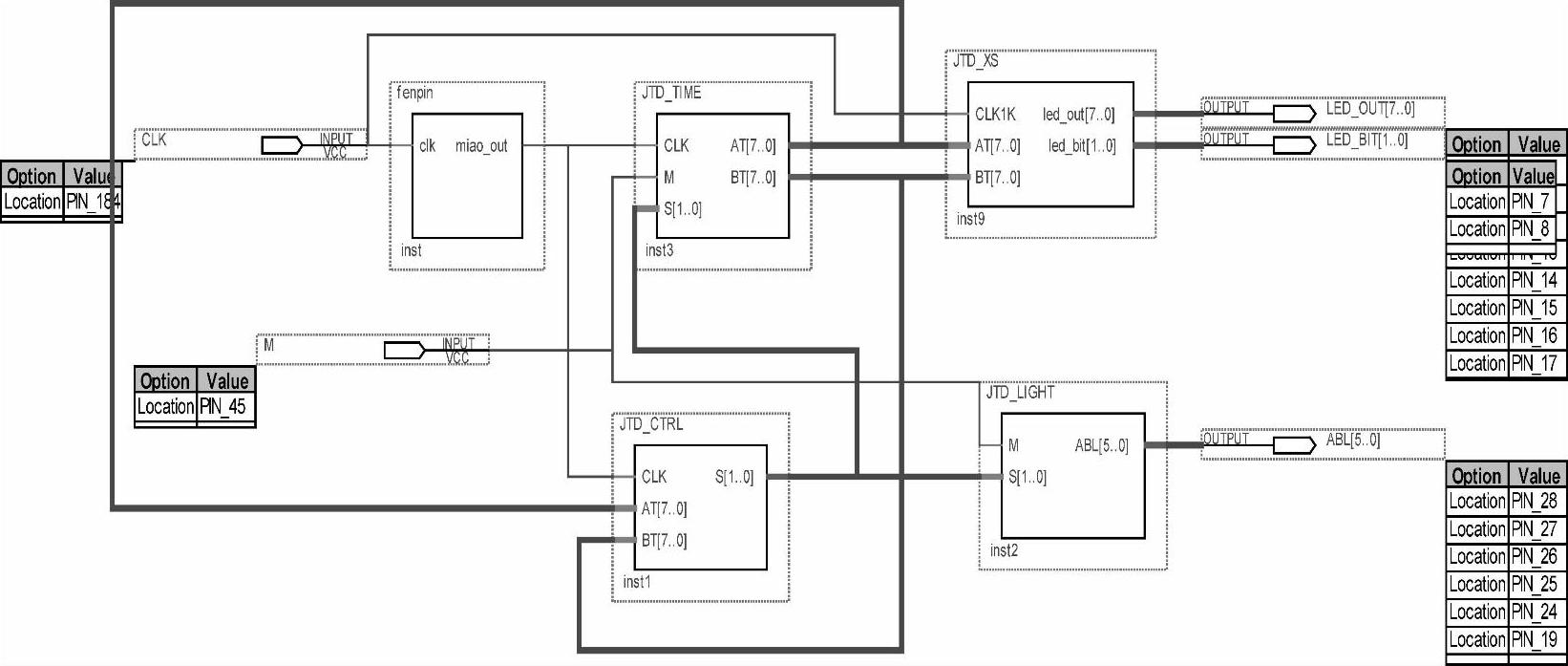

顶层原理图设计可以依据系统框图进行,由分频模块(fenpin)、反馈控制模块(JTD_CTRL)、倒计时模块(JTD_TIME)、数码管显示模块(JTD_XS)、信号灯显示模块(JTD_LIGHT)5部分组成。顶层原理图如图5-24所示。

图5-24 顶层原理图

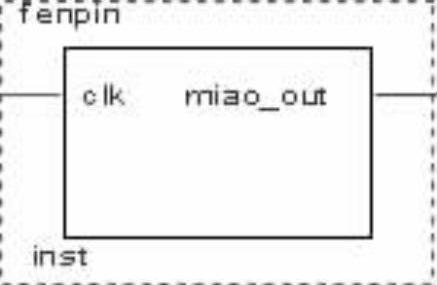

图5-25 分频模块硬件图

1.各个模块硬件电路设计与仿真波形

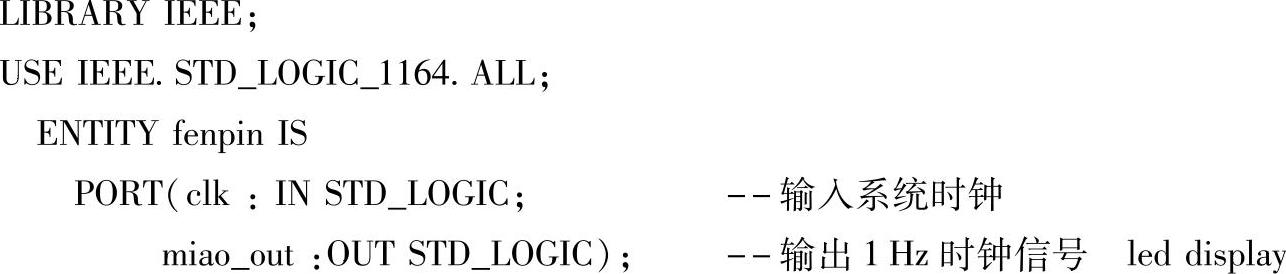

(1)分频模块

分频模块实现的是将高频时钟信号转换成低频时钟信号,clk作为经分频器的输入端,将100MHz时钟分频为1Hz的信号由miao_out输出提供给倒计时模块和状态控制模块共同使用。

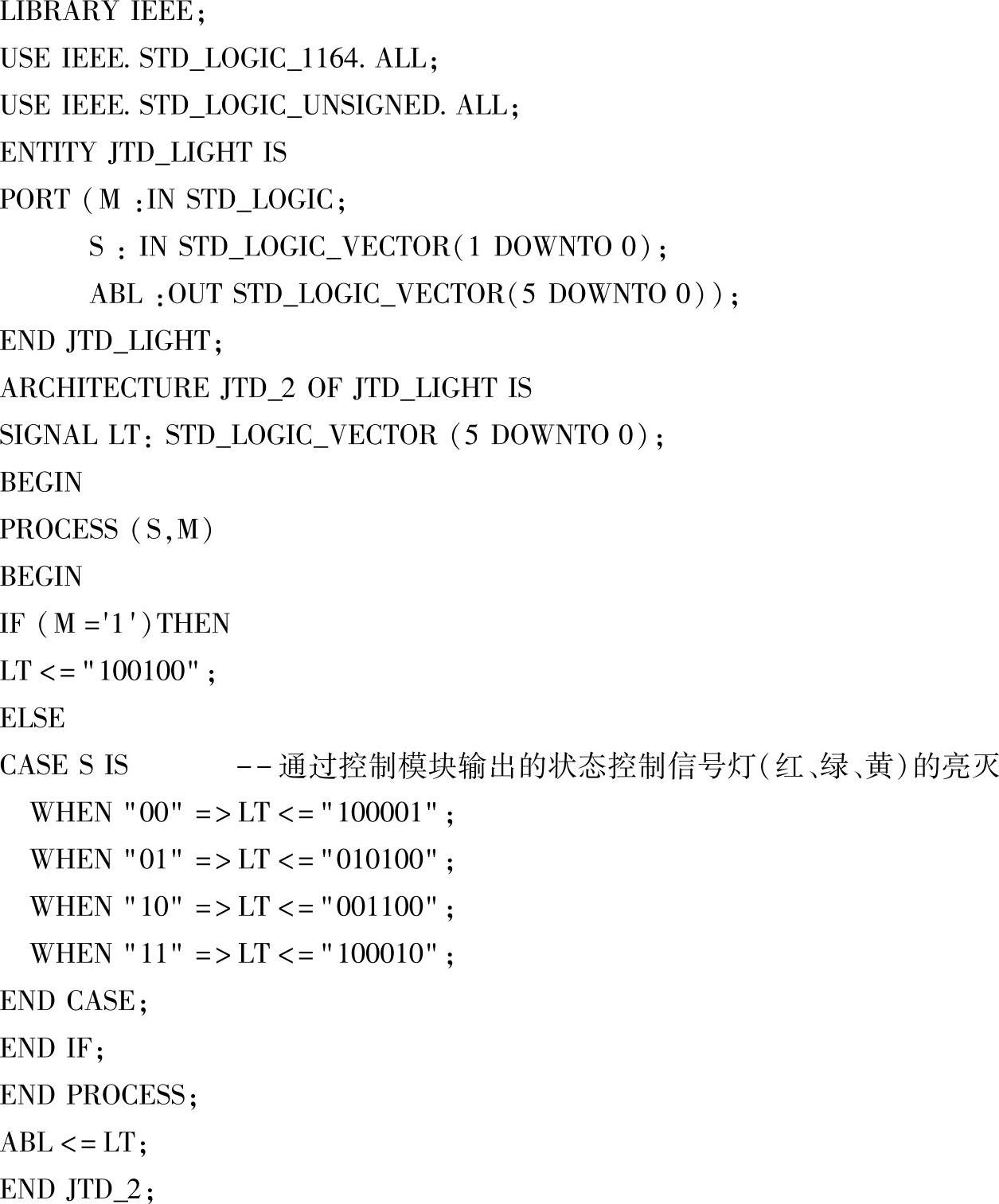

100MHz信号的周期为10ns,分频后的1Hz信号周期为1s,因此当clk信号出现50MHz个周期时,miao_out才变换一次状态。分频模块程序如下:

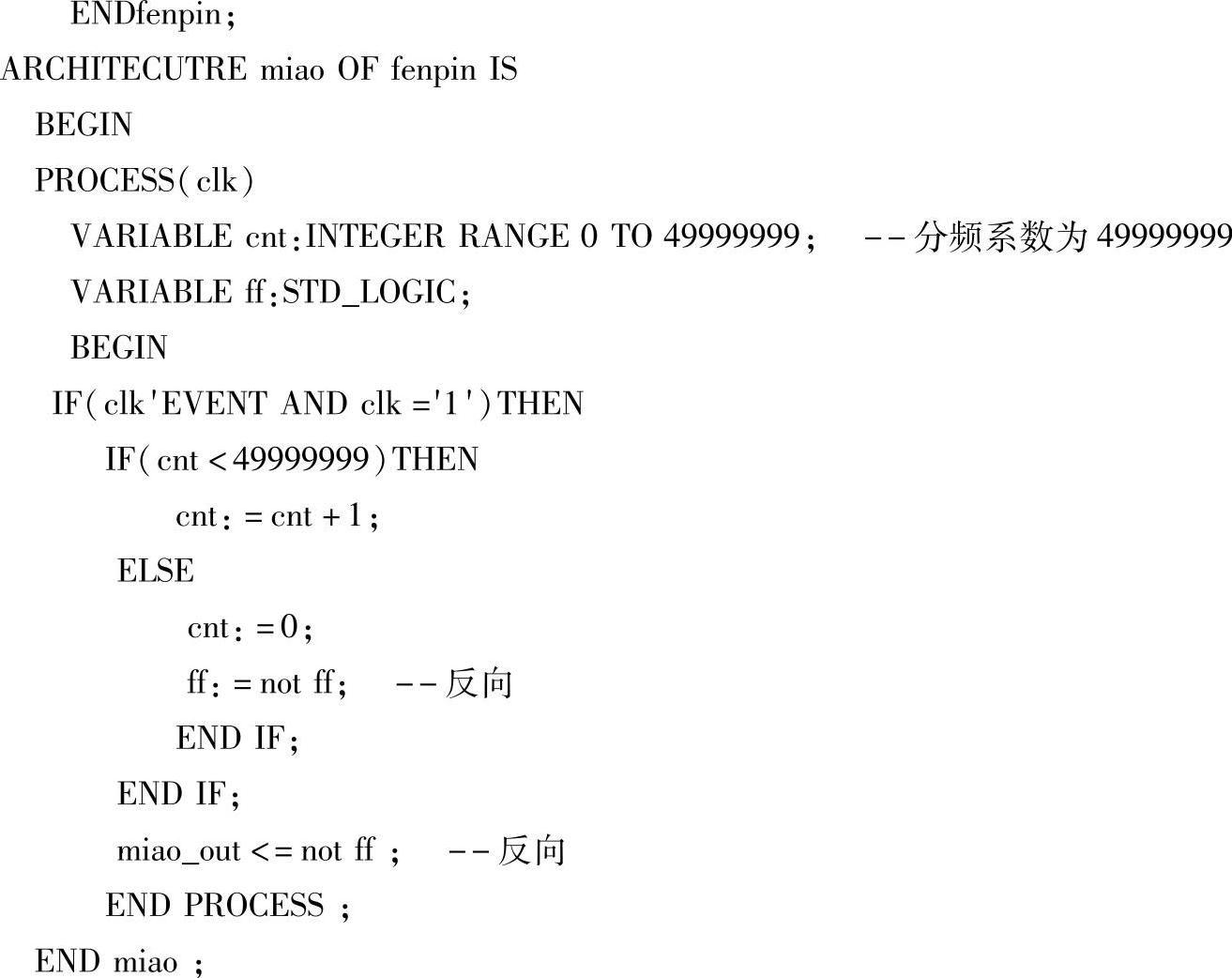

图5-26 状态控制模块硬件图

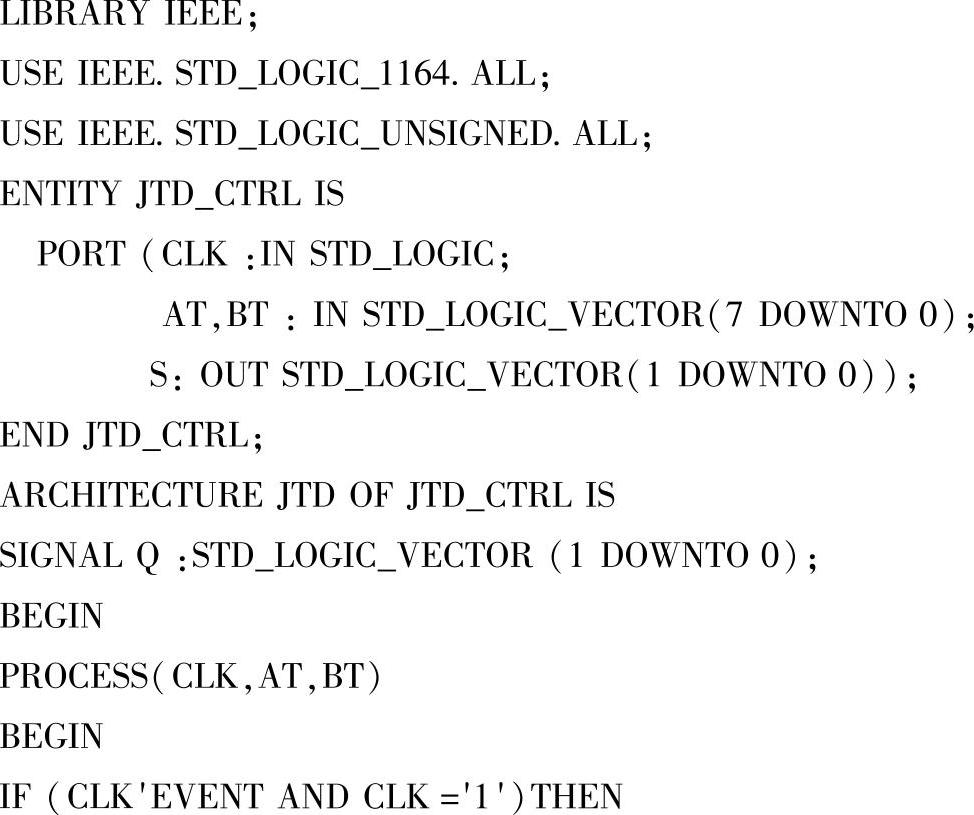

(2)状态控制模块

状态控制模块根据倒计时模块的输出信号和1Hz的时钟信号,产生系统的状态机,控制倒计时模块和信号灯显示模块的协调工作。其中,clk为1Hz信号输入端,AT[7..0]、BT[7..0]为倒计时模块的输出信号作为状态控制的输入信号进行反馈控制,S[1..0]为状态控制输出端。

状态控制模块是由倒计时模块的输出信号反馈控制的,当CLK出现一个上升沿时倒计时时间减少1s,由AT、BT的时间决定输出S的状态。状态控制模块程序如下:

图5-27 倒计时模块硬件图

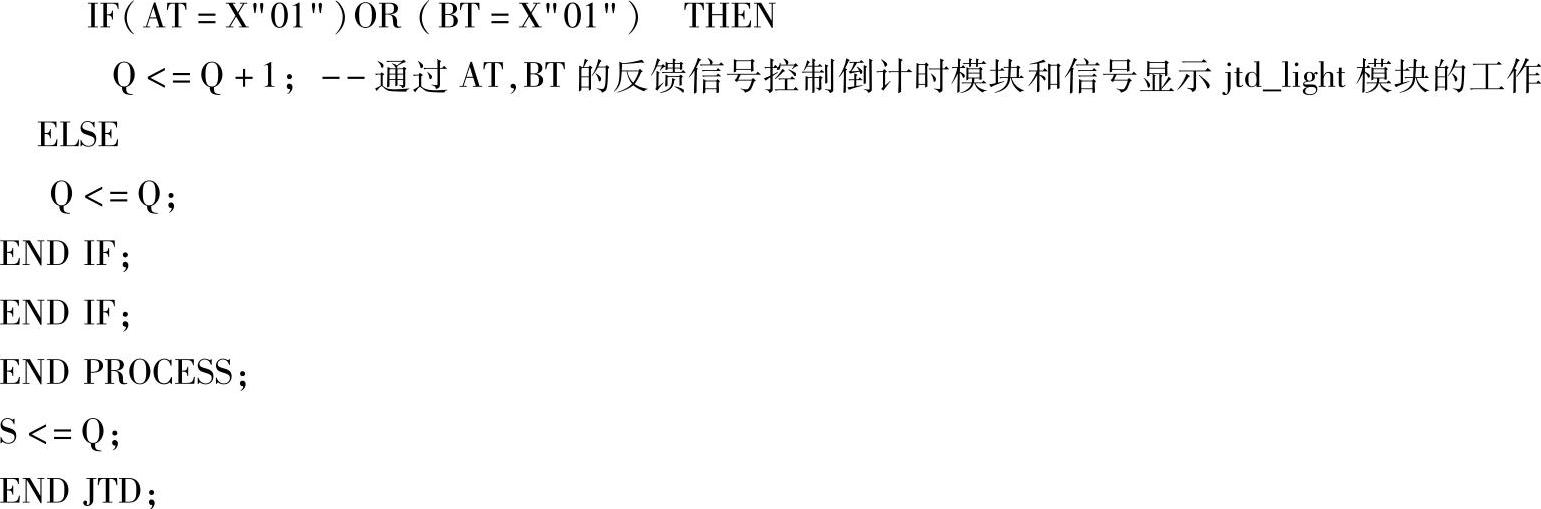

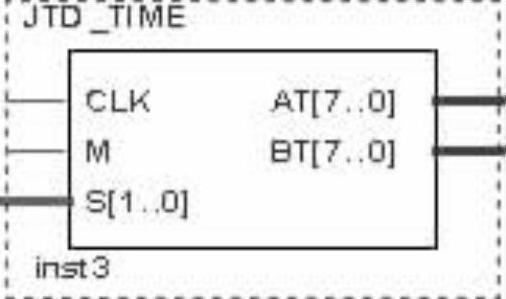

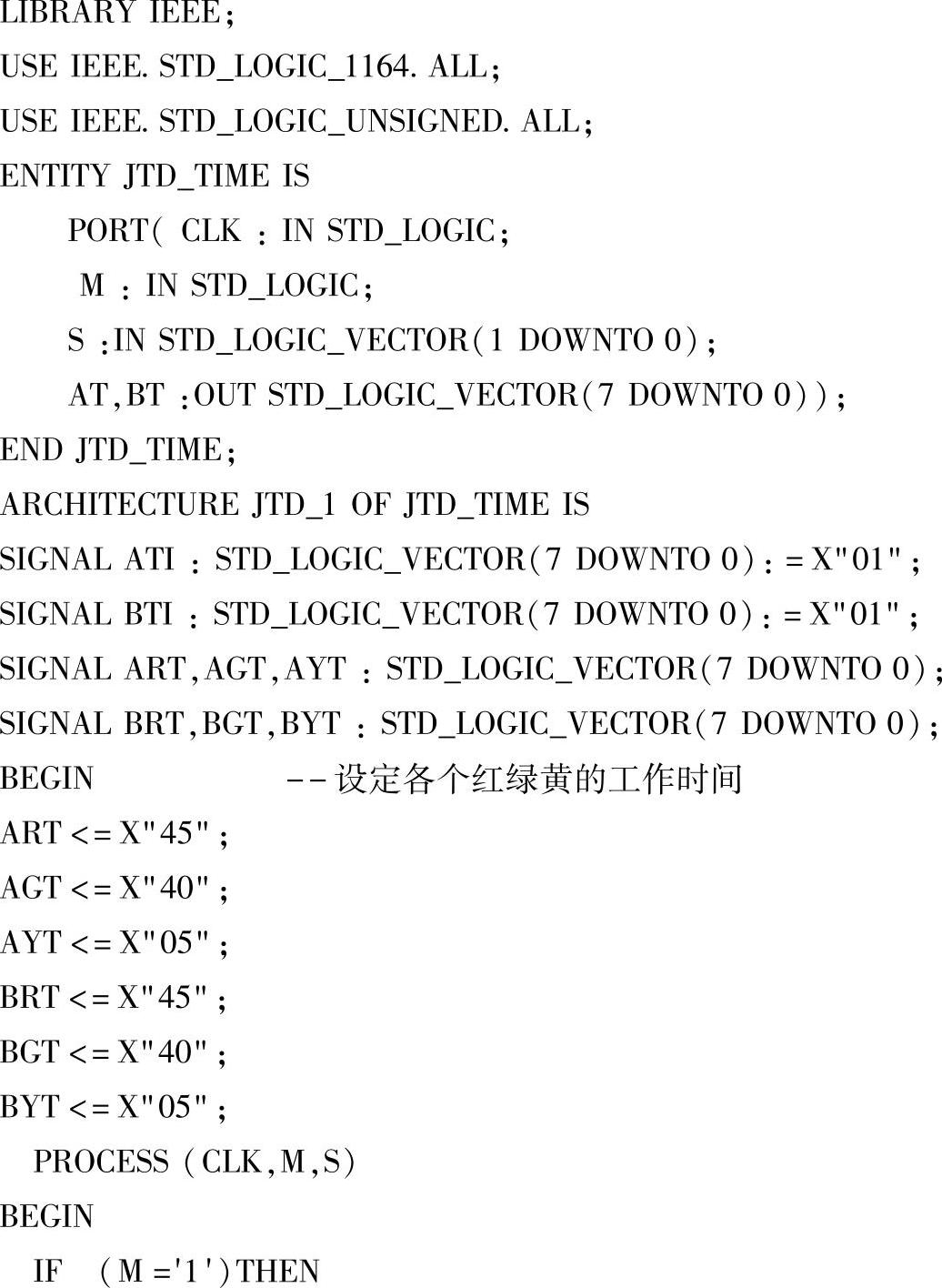

(3)倒计时模块的设计(https://www.xing528.com)

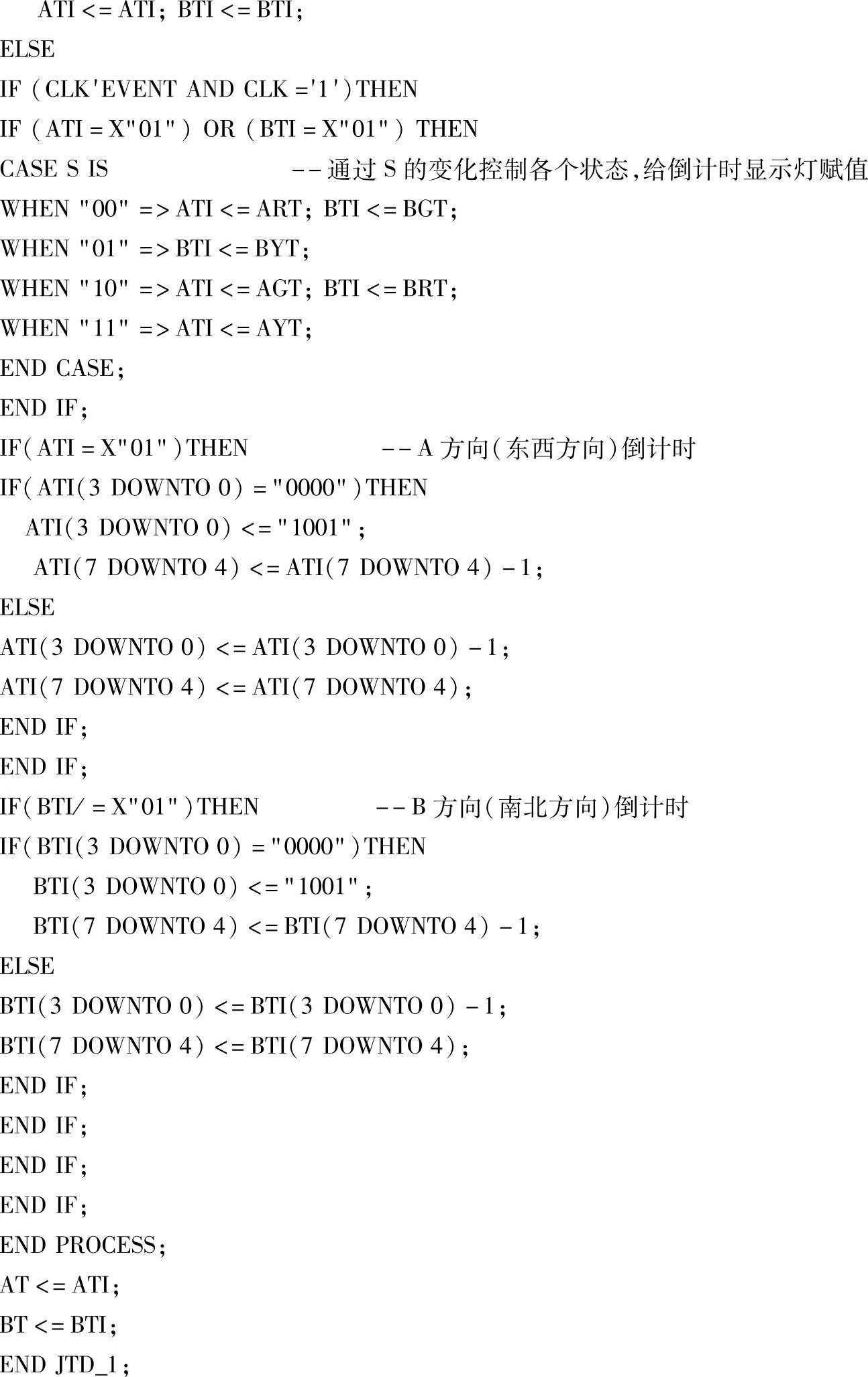

倒计时模块用来设定A和B两个方向计时器的初值,并为数码管显示模块提供倒计时时间。其中,M为紧急情况输入端(M=0时正常工作),CLK为1Hz信号时钟,S[1..0]为状态控制输入端,进行倒计时的控制,AT[7..0]、BT[7..0]为倒计时时间输出端。

当M=0时正常工作,AT、BT分别进行东西、南北方向的倒计时,M=1时停止倒计时。倒计时模块程序如下:

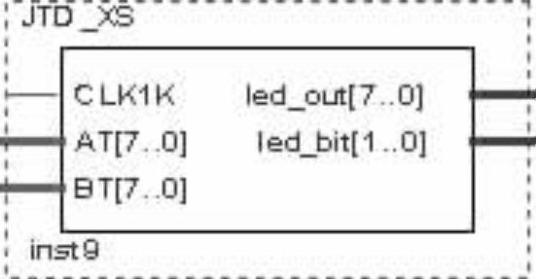

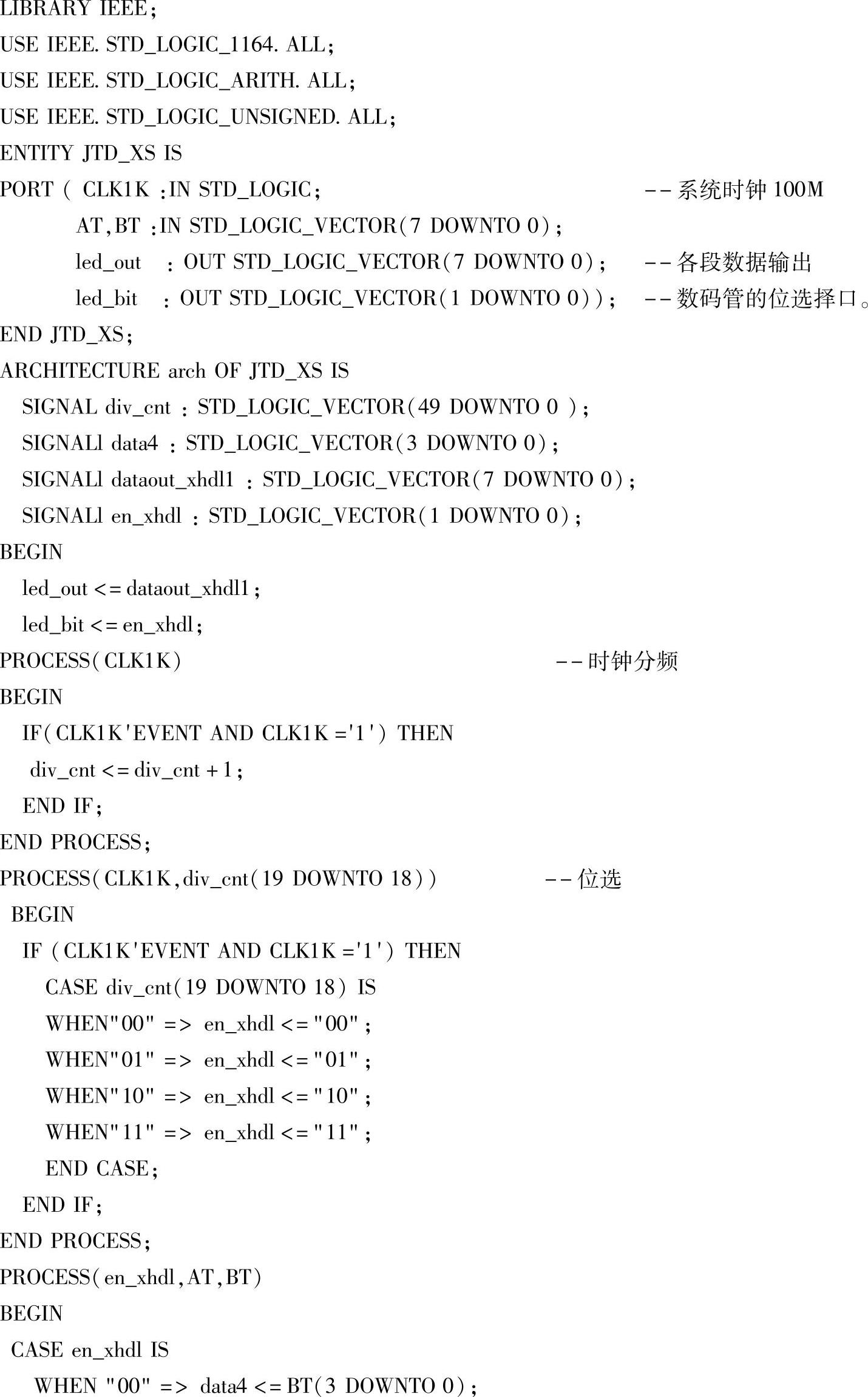

(4)数码管显示模块的设计

显示模块用来显示倒计时时间。采用动态扫描显示,通过分位程序,控制4个数码管的显示时间。其中,CLK1K为100MHz时钟输入端,经分频后进行数码管扫描,AT[7..0]、BT[7..0]输入端与倒计时模块输出端连接,输出端led_out[7..0]、led_bit[1..0]分别连接数码管的段选和位选。

图5-28 数码管显示模块硬件图

CLK1K分频后进行数码管扫描,分频后的时钟信号必须比1Hz的时钟信号大很多;输出端led_out、led_bit由AT、BT决定,进行数码管的段选和位选进行显示。数码管显示模块程序如下:

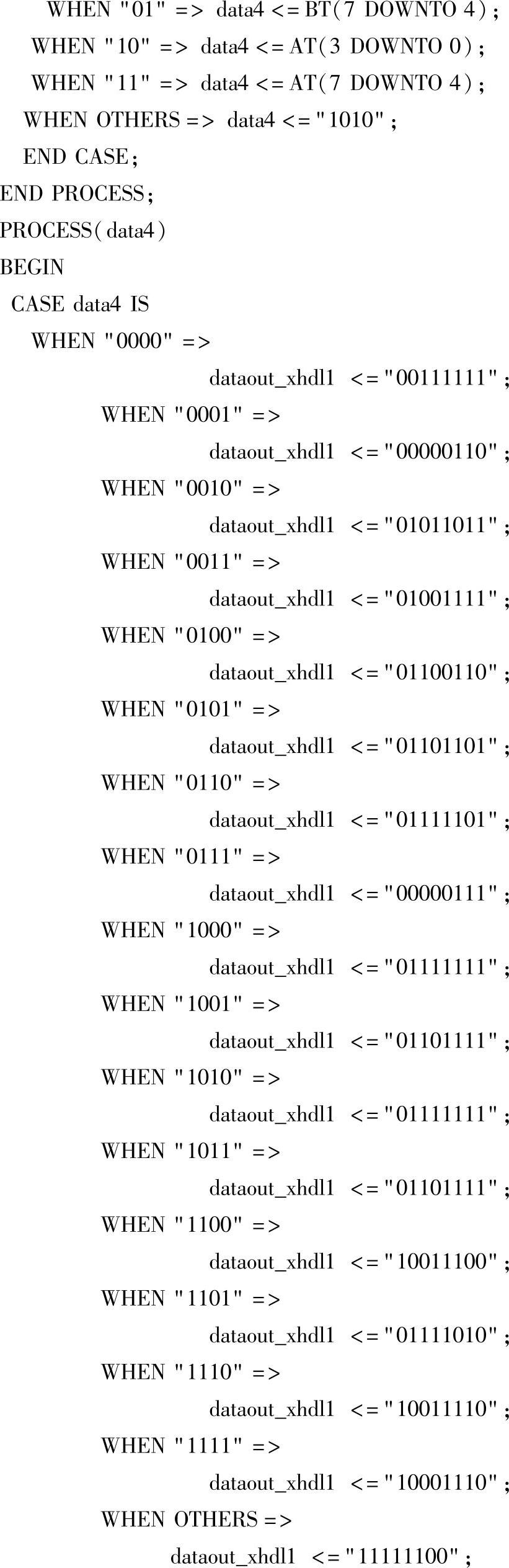

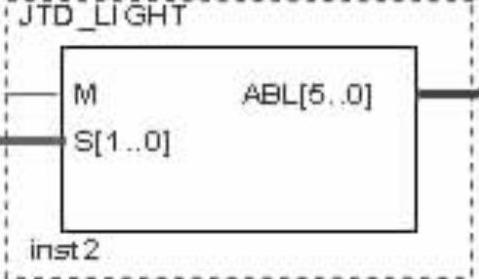

(5)信号灯显示模块的设计

通过控制模块的输出的状态控制信号,控制6个信号灯的亮灭。其中,M为紧急情况输入端,输入端S[1..0]连接状态控制模块的输出,对6个信号灯进行状态控制显示,输出端ABL[5..0]分别连接东西、南北方向的红、绿、黄信号灯。

图5-29 信号灯显示模块硬件图

交通灯工作的一个周期,当M=1时出现紧急情况,东西、南北方向(ABL[5]~ABL[0])显示红、绿、黄分别为100100。当M=0时出现4种状态,状态为00时,东西、南北方向(ABL[5]~ABL[0])显示红、绿、黄分别为100010;状态01时显示100001;状态10时显示010100;状态11时显示001100。

信号灯显示模块程序如下:

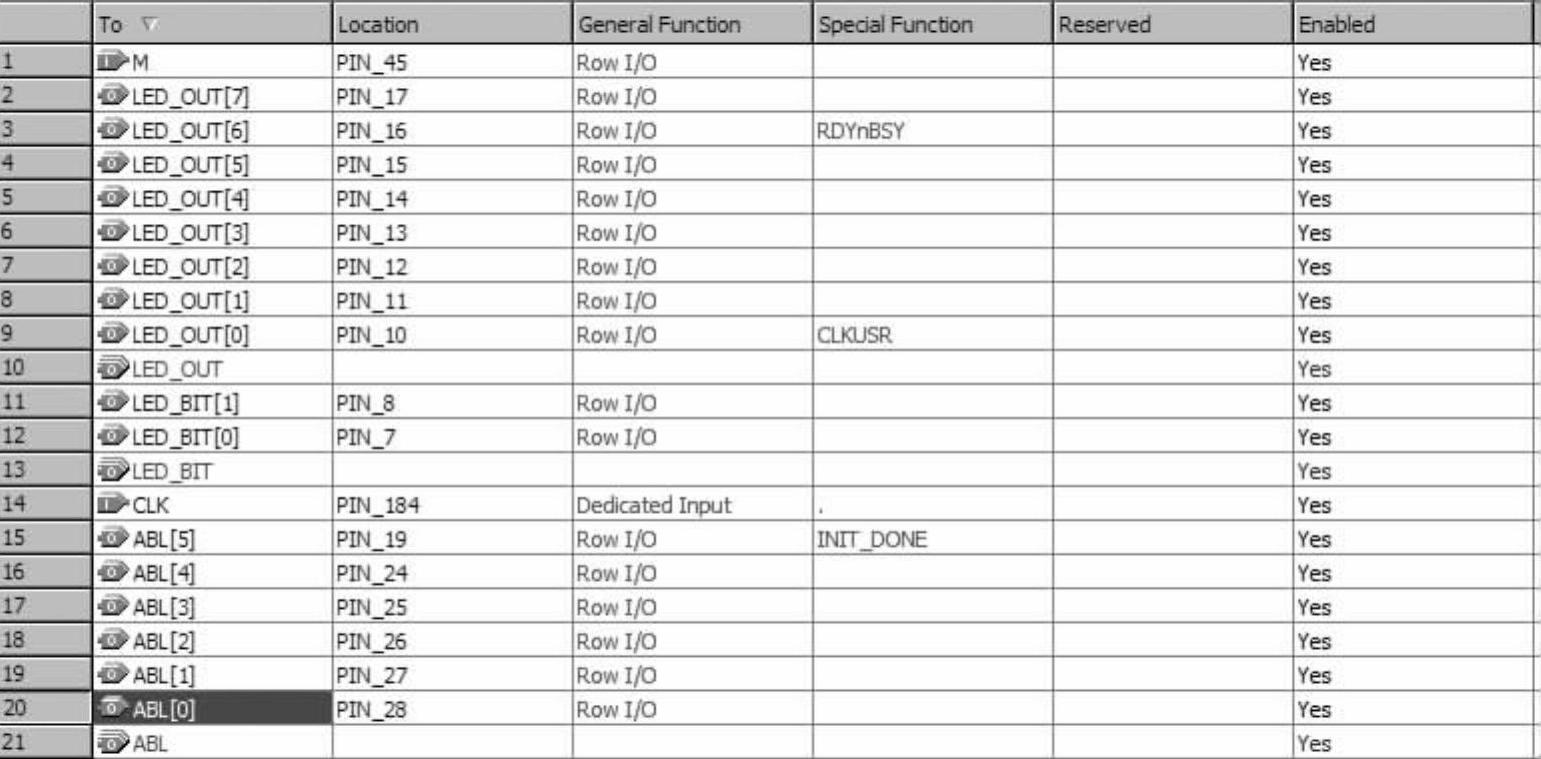

2.引脚定义

顶层原理图的引脚定义。输入clk接PIN_184提供100MHz的时钟,M接PIN_45实现紧急情况的模拟;输出led_out[7..0]接PIN_17~PIN_10进行数码管的段选控制显示数字,led_bit[1..0]接PIN_8、PIN_7输入3线-8线译码器的B,A脚进行数码管的位选控制。

引脚图定义如图5-30所示。

图5-30 引脚定义图

3.编译下载

本设计引用ACEX1K系列的EP1K30QC208-2芯片,选择clk为100MHz,外围电路包括6个流水灯代替交通灯,4个数码管分别显示东西方向和南北方向的剩余时间。引脚锁定后,下载FPGA芯片中。

6个信号灯依次为东西方向的红绿黄和南北方向的红绿黄。结果显示两个方向上的数码管显示的时间与信号灯显示的状态完全吻合,不断在4个状态中循环变化。键45为紧急状态控制端,按下键45时,两路信号灯都为红灯,时间暂停,再次按下键45,恢复原状态,继续计时。结果证实调试成功。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。