在数字系统中,计数器是应用最为广泛的时序逻辑电路。计数器的基本功能是记忆时钟脉冲的个数,它是用几个触发器的状态,按照一定的规律随时钟变化来记忆时钟的个数。常用的计数器包括二进制计数器、十进制计数器、加法计数器、减法计数器、同步计数器和异步计数器等。

1.4位二进制计数器的设计

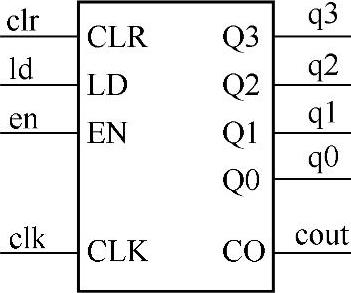

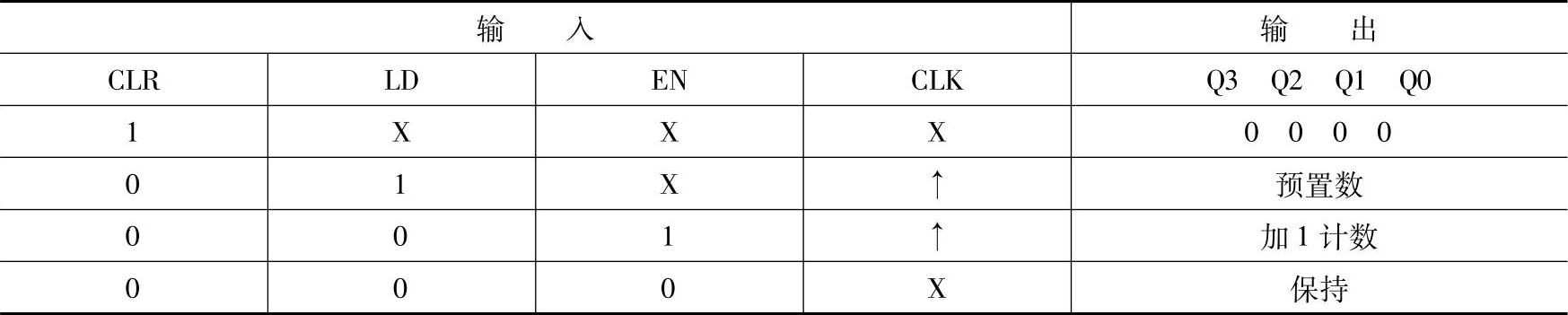

下面将以一个带有异步复位、同步预置数、同步使能和进位输出端的4位二进制计数器为例,介绍计数器的VHDL设计。该4位二进制计数器的逻辑符号如图5-18所示,功能表见表5-11。当4位二进制计数器计数值为“1111”时,进位输出端CO为‘1’,程序中设定同步预置数为“1010”。

图5-18 4位二进制计数器的逻辑符号

表5-11 4位二进制计数器的功能表

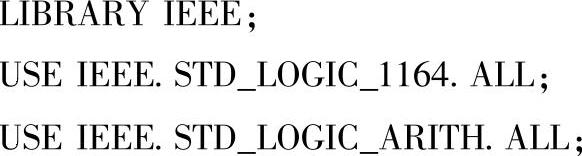

用VHDL描述的带使能端的4位二进制计数器的源程序如例5.17所示。

例5.17

(https://www.xing528.com)

(https://www.xing528.com)

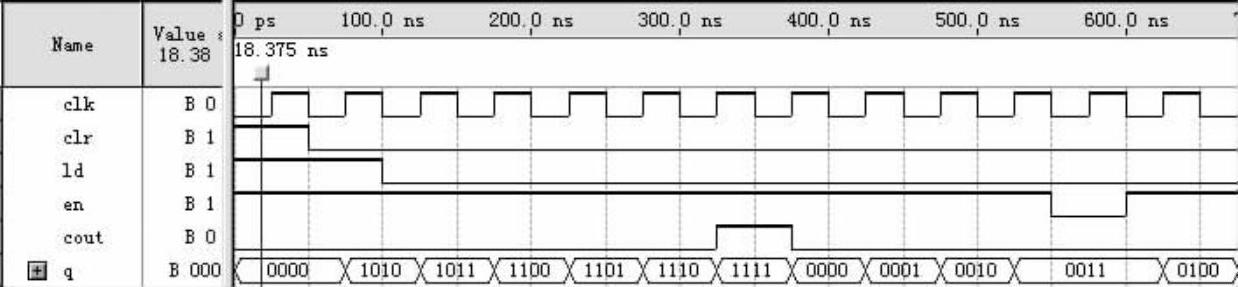

带使能端的4位二进制计数器的仿真波形如图5-19所示:从图中可以看出,当clr为‘1’时,计数器清0;当clr是‘0’且时钟信号clk上升沿到来时,如果加载信号有效,即ld=‘1’时,计数器置数q=“1010”;ld=‘0’时,当使能端en为‘1’时,计数器加1计数,否则计数值保持。以此类推,结果是正确的。

图5-19 带使能端的4位二进制计数器的仿真波形

2.数控分频器的设计

数控分频器的功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,数控分频器就是用计数值可并行预置的加法计数器设计完成的,方法是将计数溢出位与预置数加载输入信号相连即可。

例5.18

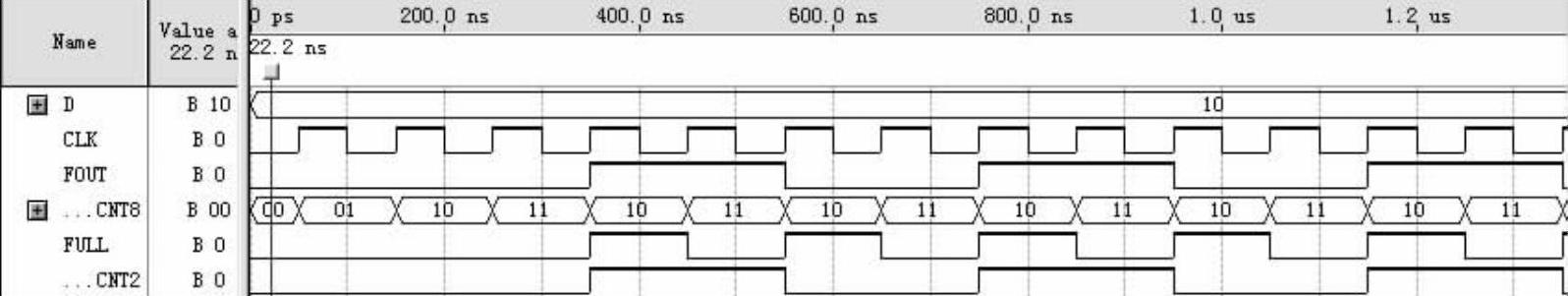

数控分频器的仿真波形如图5-20所示。从图中可以看出,当时钟信号clk上升沿到来时,如果输入端D=‘10’时,分频器的输出FOUT是时钟信号的4分频,FULL是时钟信号的2分频。当在输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,数控分频器就是用计数值可并行预置的加法计数器设计完成的。

图5-20 数控分频器的仿真波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。