1.寄存器的设计

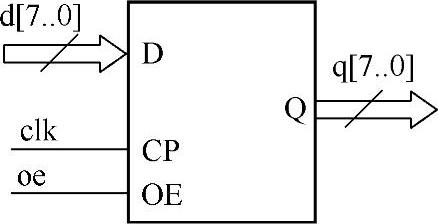

寄存器是数字系统中用来存储二进制数据的逻辑电路。1个触发器可存储1位二进制数据,存储n位二进制数据的寄存器需要用n个触发器组成。寄存器与锁存器具有类似的功能,两者的区别在于寄存器是同步时钟控制,而锁存器是电位信号控制。带使能端的8位寄存器的逻辑符号如图5-14所示,功能表见表5-10。

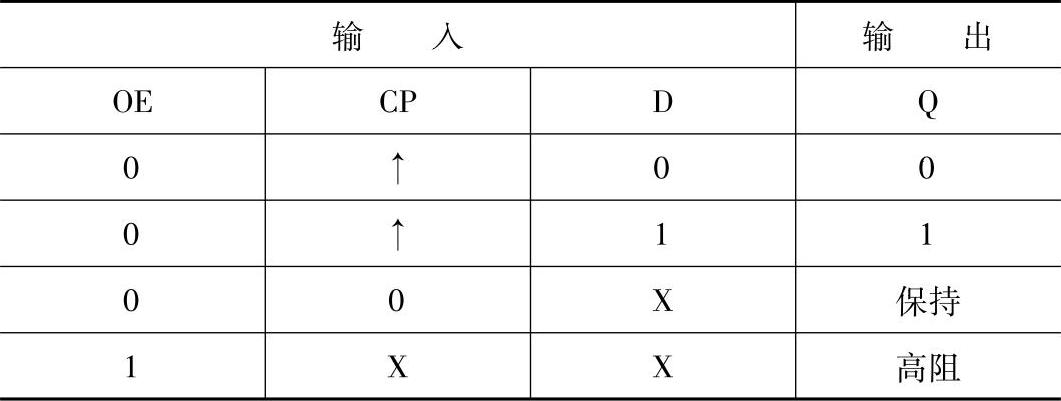

表5-10 带使能端的8位寄存器的功能表

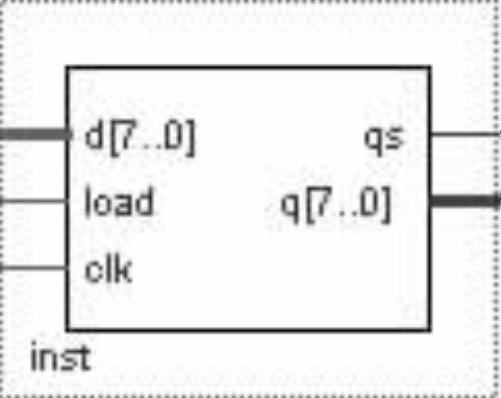

图5-14 带使能端的8位寄存器的逻辑符号

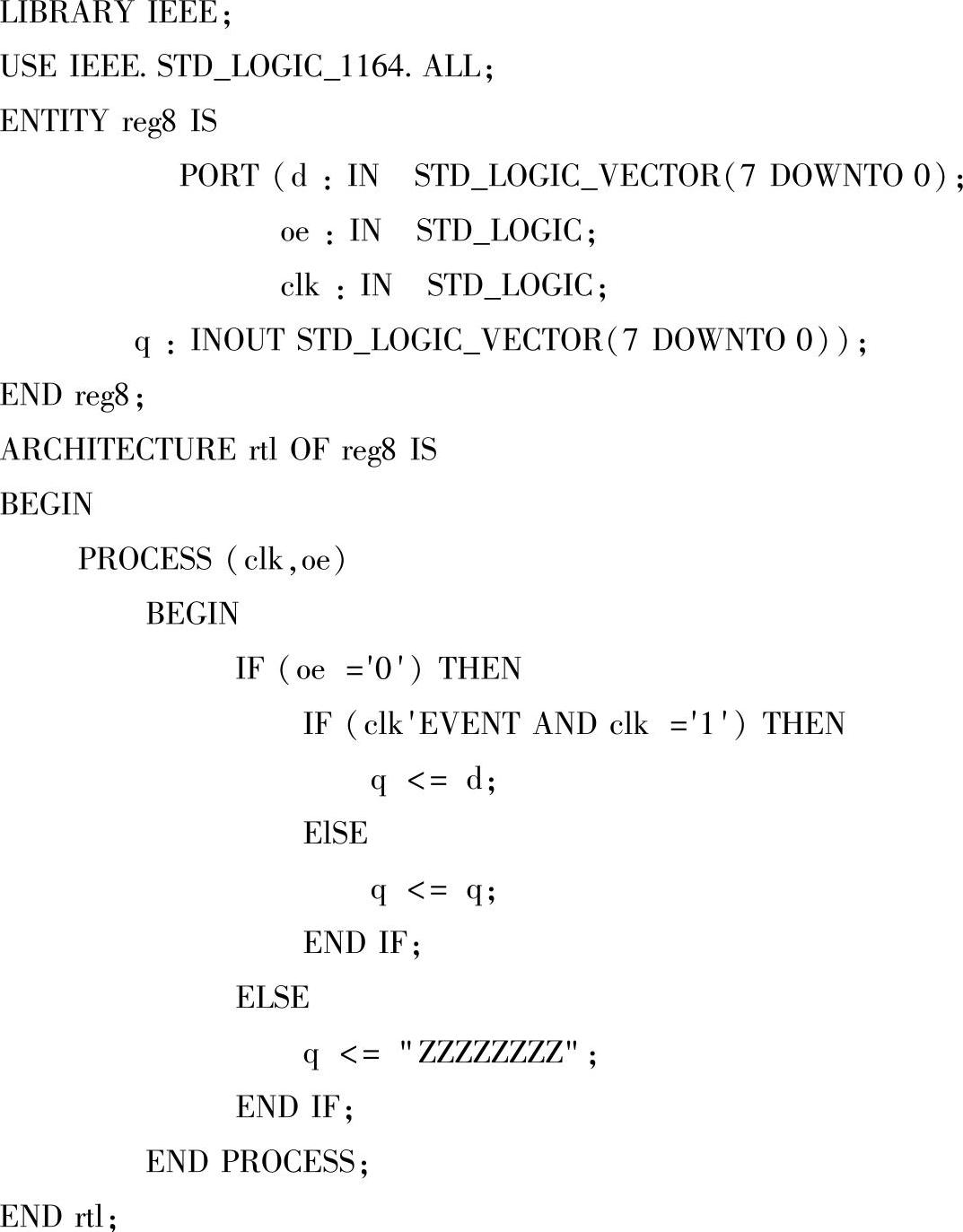

用VHDL描述的带使能端的8位寄存器的源程序如例5.15所示。

例5.15

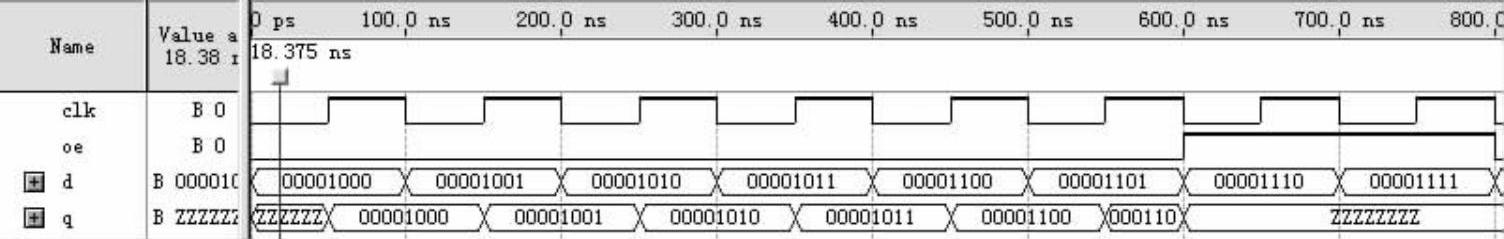

带使能端的8位寄存器的电路仿真波形如图5-15所示。当使能端oe=‘0’时并且时钟信号clk上升沿到来时,寄存器把输入端口的8位数据d送到输出端口q;当oe=‘1’寄存器的输出端口将处于高阻状态。

图5-15 带使能端的8位寄存器的电路仿真波形(https://www.xing528.com)

2.移位寄存器的设计

移位寄存器除了具有寄存数码的功能外,还具有移位功能,即在移位脉冲作用下,能够把寄存器中的数依次向右或向左移,它是一个同步时序逻辑电路。可预加载循环移位寄存器逻辑符号如图5-16所示。

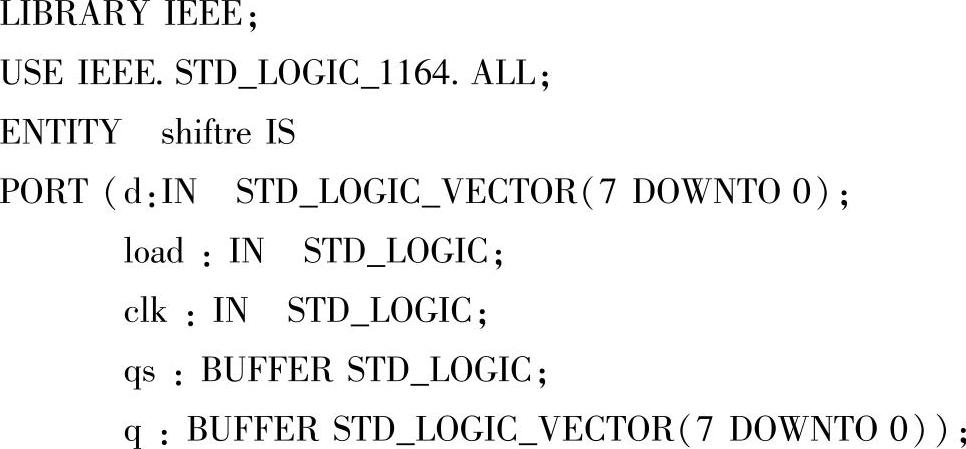

用VHDL描述可预加载循环移位寄存器的源程序如例5.16所示。

图5-16 可预加载循环移位寄存器的逻辑符号

例5.16

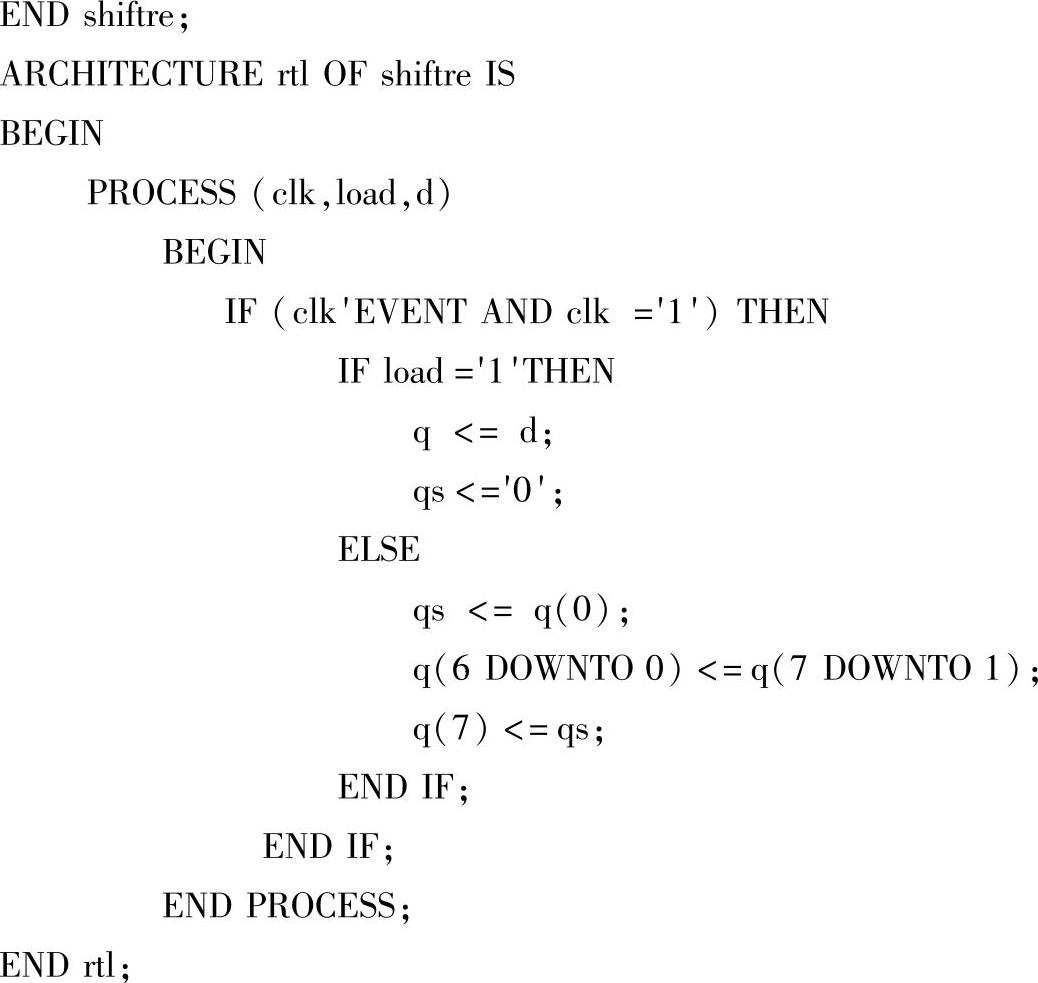

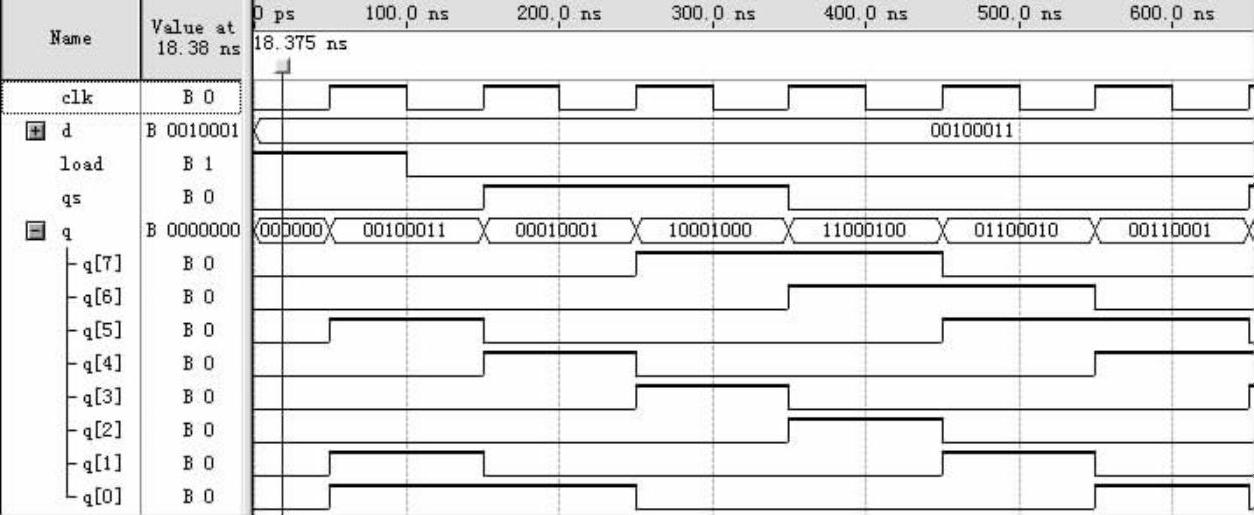

可预加载循环移位寄存器的波形如图5-17所示。从图中可以看出,当时钟信号clk的上升沿到来时,如果加载信号有效即load=‘1’时,寄存器把输入端口的8位数据d=“00100011”送到输出端口q;load=‘0’时,在时钟信号clk上升沿到来时,q高7位向右移一位,最高位q(7)等于q的前一次状态q(0),在移动脉冲的作用下,q的移动以此类推,结果正确。

图5-17 可预加载循环移位寄存器的仿真波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。