【摘要】:触发器是具有记忆功能的基本逻辑单元,能够存储1位信号的基本单元电路称为触发器。一个基本的上升沿触发的D触发器的逻辑功能表见表5-7。用VHDL描述的D触发器源程序如例5.12所示。图5-10 D触发器电路的仿真波形2.JK触发器的设计在数字电路中,JK触发器也是一种较为常用的基本时序电路。例5.13带异步置位/复位端的JK触发器电路仿真波形如图5-11所示。

触发器是具有记忆功能的基本逻辑单元,能够存储1位信号的基本单元电路称为触发器。根据电路结构形式和控制方式的不同,可以将触发器分为D触发器、JK触发器、T触发器和RS触发器等几种类型。

1.基本D触发器的设计

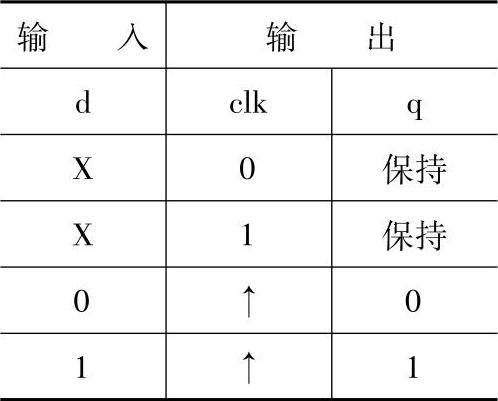

在数字电路中,D触发器是一种基本时序电路,它是构成数字电路系统的基础。一个基本的上升沿触发的D触发器的逻辑功能表见表5-7。

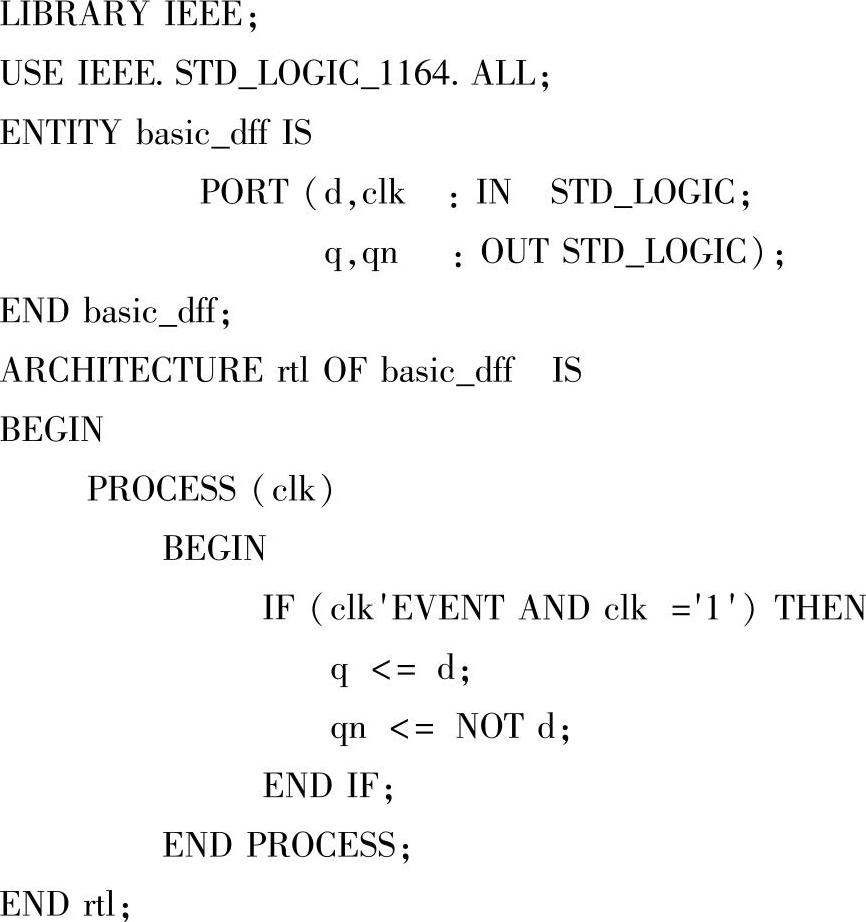

用VHDL描述的D触发器源程序如例5.12所示。

例5.12

表5-7D 触发器的逻辑功能表

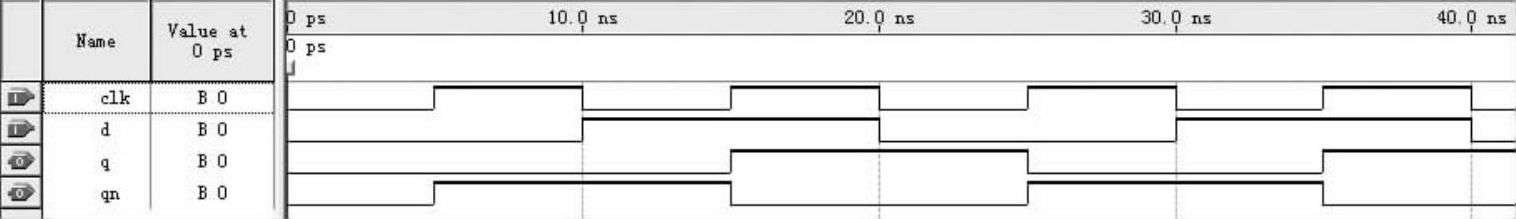

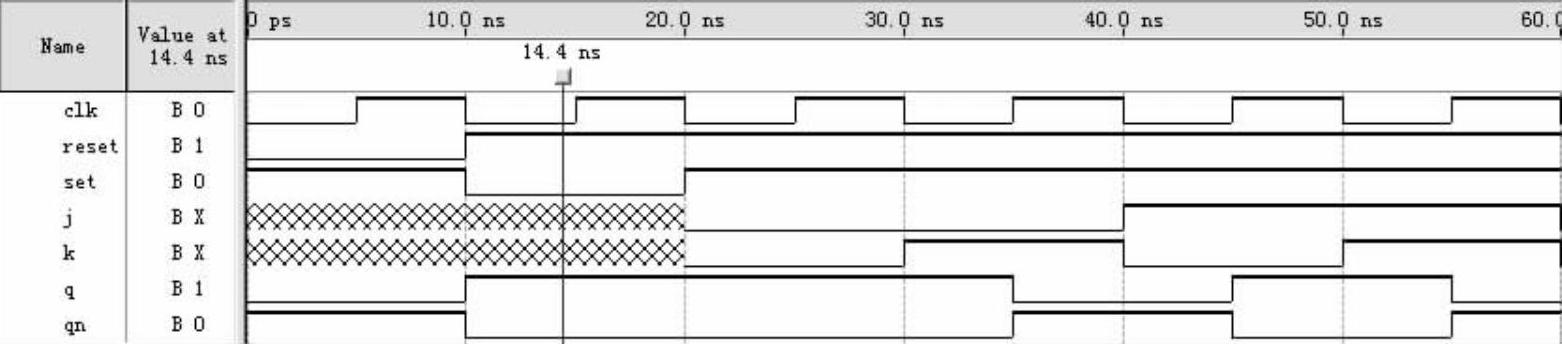

D触发器电路仿真波形如图5-10所示。从图中可以看出,当时钟信号clk上升沿到来时,结果q=d,qn与q相反,结果与理论值符合。

图5-10 D触发器电路的仿真波形

2.JK触发器的设计(https://www.xing528.com)

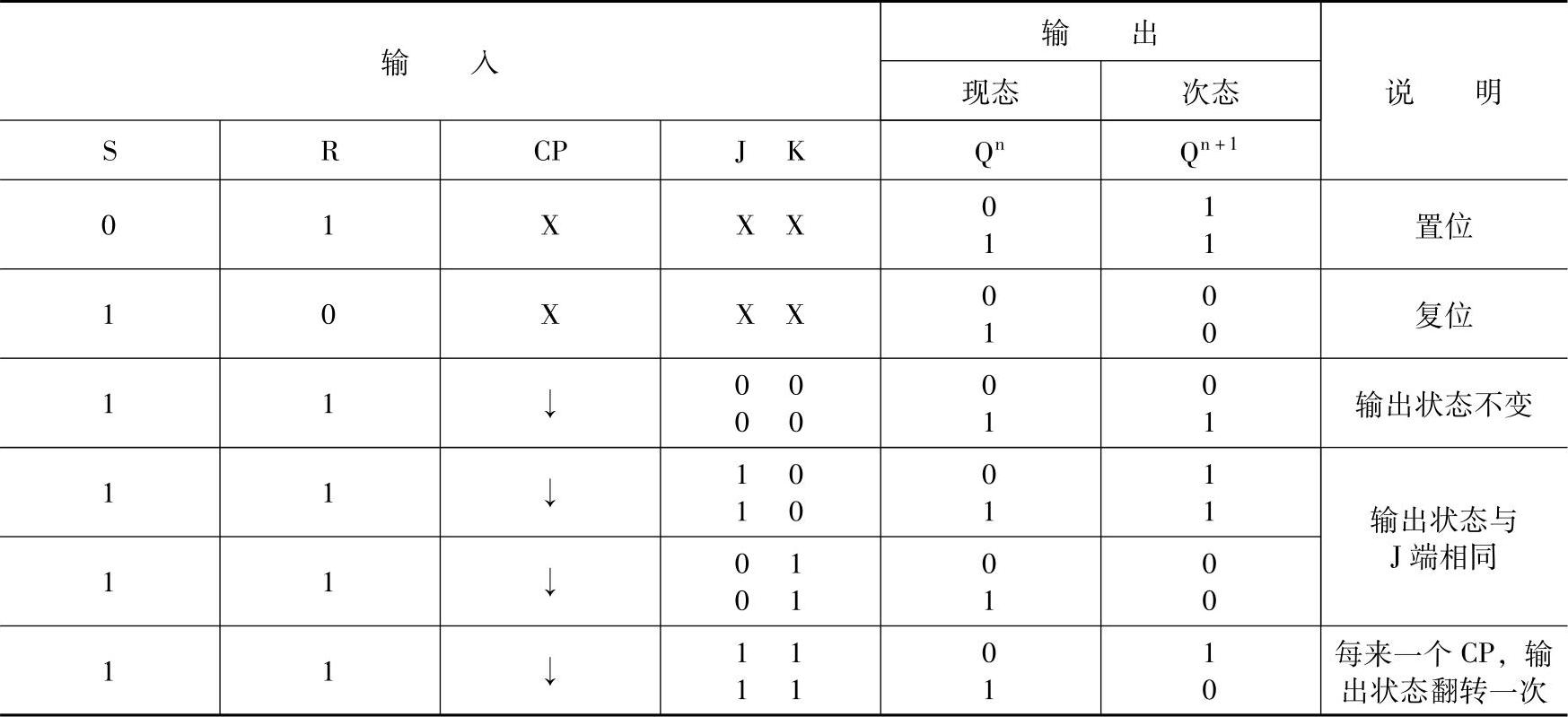

在数字电路中,JK触发器也是一种较为常用的基本时序电路。带异步置位/复位端的JK触发器的逻辑功能见表5-8。

表5-8 JK触发器逻辑功能表

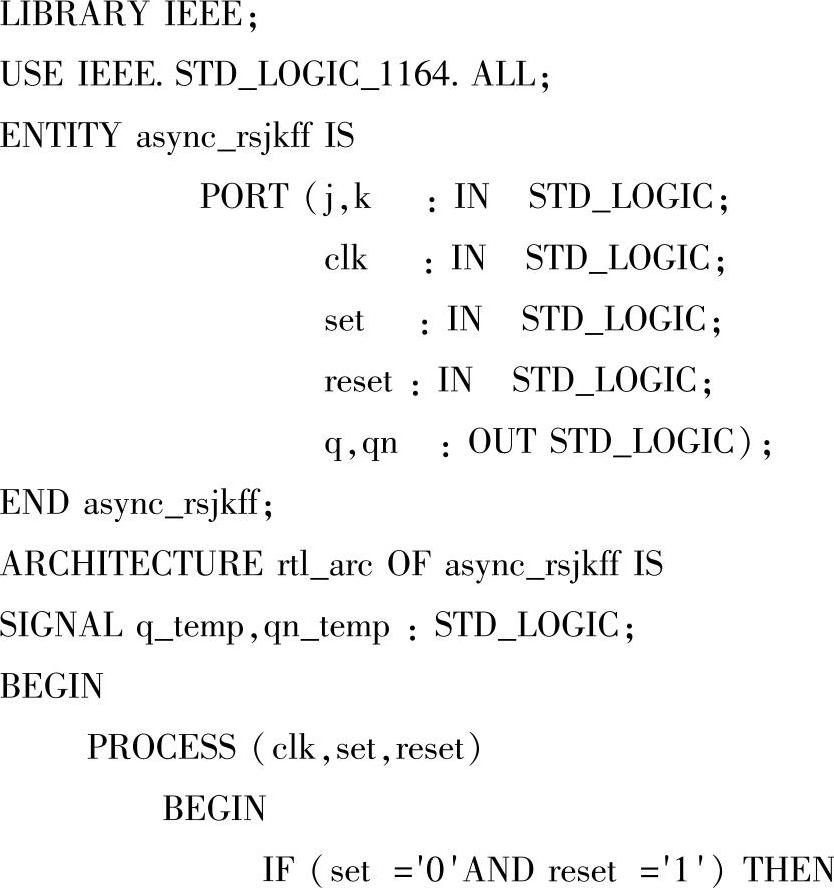

用VHDL描述的带异步置位/复位端的JK触发器源程序如例5.13所示。

例5.13

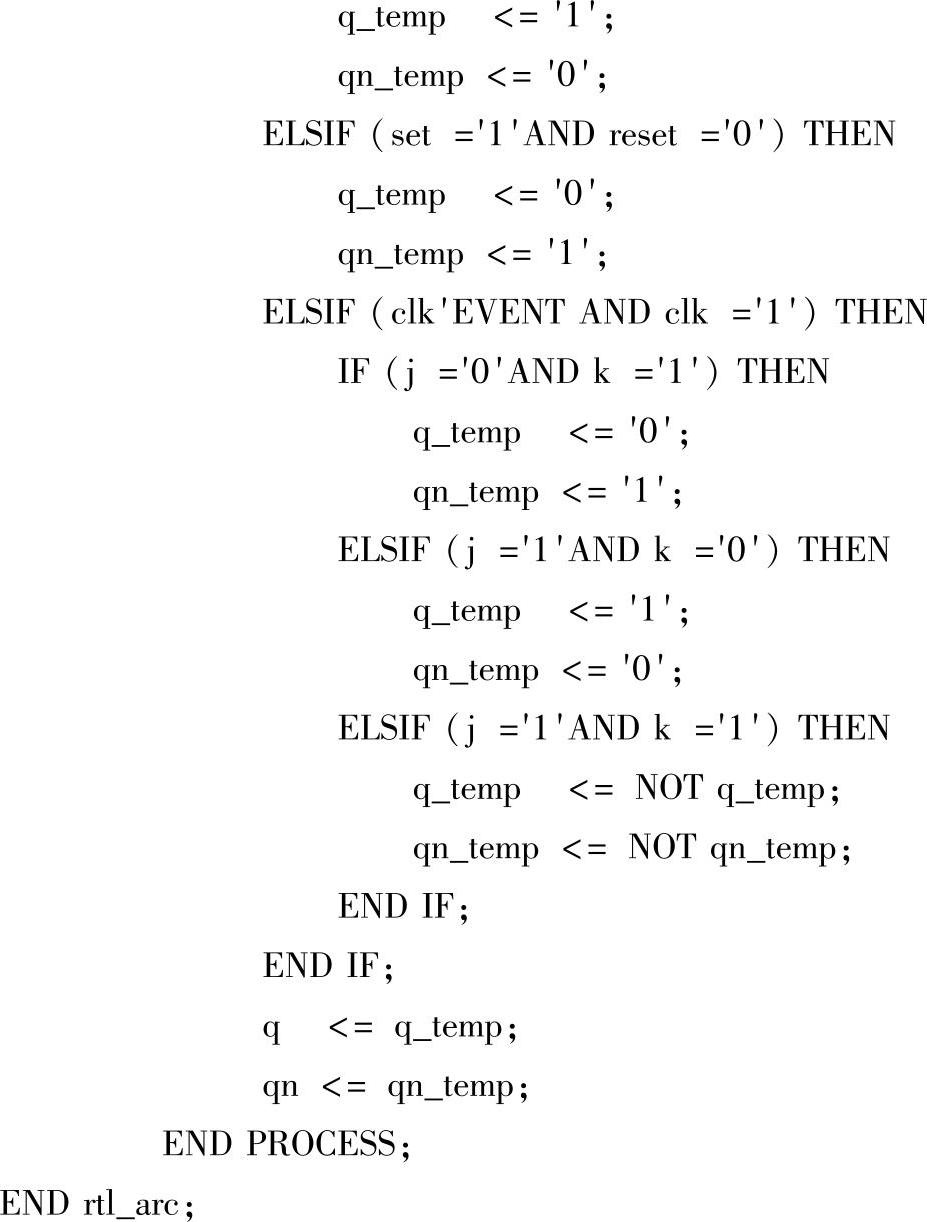

带异步置位/复位端的JK触发器电路仿真波形如图5-11所示。从图中可以看出,置位信号set=‘0’且复位端reset=‘1’时,不管原来的输出状态q是何值都分别置‘1’;置位信号set=‘1’且复位端reset=‘0’时,不管原来的输出状态q是何值都分别复位‘0’;置位信号set=‘1’且复位端reset=‘1’时,j=‘1’,k=‘0’时,当时钟信号clk下降沿到来时,不管原来的输出状态q是何值都分别与j值相同,结果与理论值符合,以此类推。

图5-11 JK触发器电路的仿真波形

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。