元件例化就是将预先设计好的设计实体定义为一个元件,然后引用特定的语句将此元件与当前的设计实体中的指定端口相连接,从而为当前设计实体引入一个新的低一级的设计层次。在这里,当前设计实体相当于一个较大的电路系统,所定义的例化元件相当于一个要插在这个电路系统板上的芯片,而当前设计实体中指定的端口则相当于这块电路板上准备接受此芯片的一个插座。元件例化是使VHDL设计实体构成自上而下层次化设计的一种重要途径。

元件例化是可以多层次的,在一个设计实体中被调用安插的元件本身也可以是一个低层次的当前设计实体,因而可以调用其他的元件,以便构成更低层次的电路模块。因此,元件例化就意味着在当前结构体内定义一个新的设计层次,这个设计层次的总称叫元件,但它可以以不同的形式出现。如上所说,这个元件可以是已设计好的一个VHDL设计实体,可以是来自FPGA元件库中的元件,也可以是别的硬件描述语言(如Verilog)设计实体。该元件还可以是软的IP核,或者是FPGA中的嵌入式硬IP核。

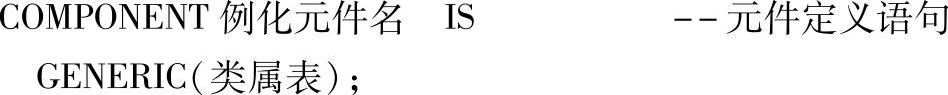

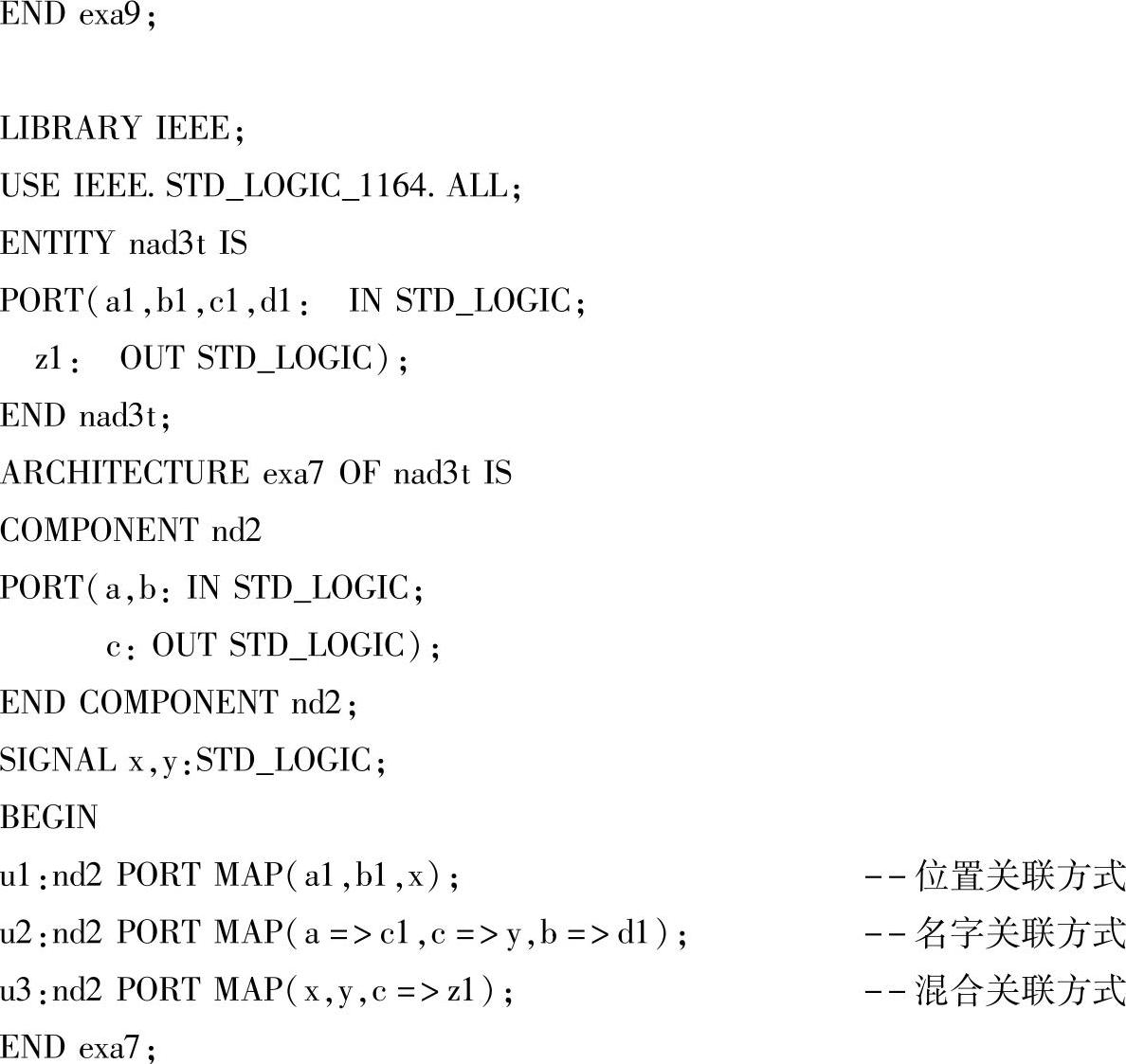

元件例化语句由两部分组成,前一部分是将一个现成的设计实体定义为一个元件的语句,第二部分则是此元件与当前设计实体中的连接说明,它们的语句格式如下:

以上两部分语句在元件例化中都必须存在的。第一部分语句是元件定义语句,相当于对一个现成的设计实体进行封装,使其只留出外面的接口界面。就像一个集成芯片只留几个引脚在外一样,它的类属表可列出端口的数据类型和参数,例化元件端口名表可列出对外通信的各端口名。元件例化的第二部分语句即为元件例化语句,其中的元件例化名是必须存在的,它类似于标在当前系统(电路板)中的一个插座名,而例化元件名则是准备在此插座上插入的、已定义好的元件名。PORTMAP是端口映射的意思,其中的例化元件端口名是在元件定义语句中的端口名表中已定义好的例化元件端口相连的通信端口,相当于插座上各插针的引脚名。

元件例化语句中所定义的例化元件的端口名与当前系统的连接实体端口名的接口表达有两种方式。一种是名字关联方式,在这种关联方式下,例化元件的端口名和关联(连接)符号“=>”两者都是必须存在的。这时,例化元件端口名与连接实体端口名的对应式,在PORTMAP句中的位置可以是任意的。另一种是位置关联方式。若使用这种方式,端口名和关联(连接)符号都可省去,在PORTMAP子句中,只要列出当前系统中的连接实体端口名就行了,但要求连接实体端口名的排列方式与所需例化的元件端口定义中的端口名一一对应。(https://www.xing528.com)

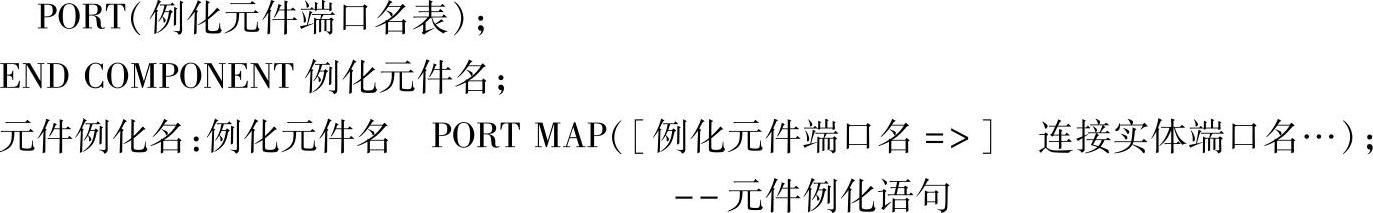

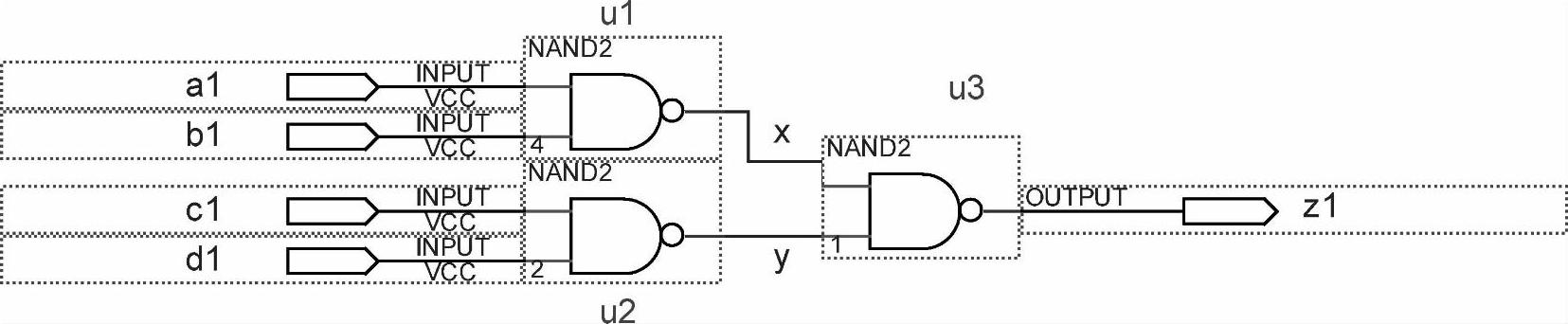

以下是一个元件例化的示例。例4.30中首先完成了一个2输入与非门的设计,然后利用元件例化产生如图4-9所示的由3个相同的与非门连接而成的电路。

图4-9 逻辑原理图

例4.30

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。