(1)逻辑阵列块(LAB)

MAX系列CPLD的内部结构主要是由若干个通过PIA互连的LAB组成,LAB不仅通过PIA互连,而且还通过PIA和全局总线连接起来,全局总线又和PLD的所有专用输入引脚、I/O引脚及宏单元馈入信号相连,这样LAB就和输入信号、I/O引脚及反馈信号连接在一起。对于MAX7128S而言,每个LAB的输入信号有32个通用逻辑输入信号、全局控制信号、从I/O引脚到寄存器的直接输入。

(2)宏单元

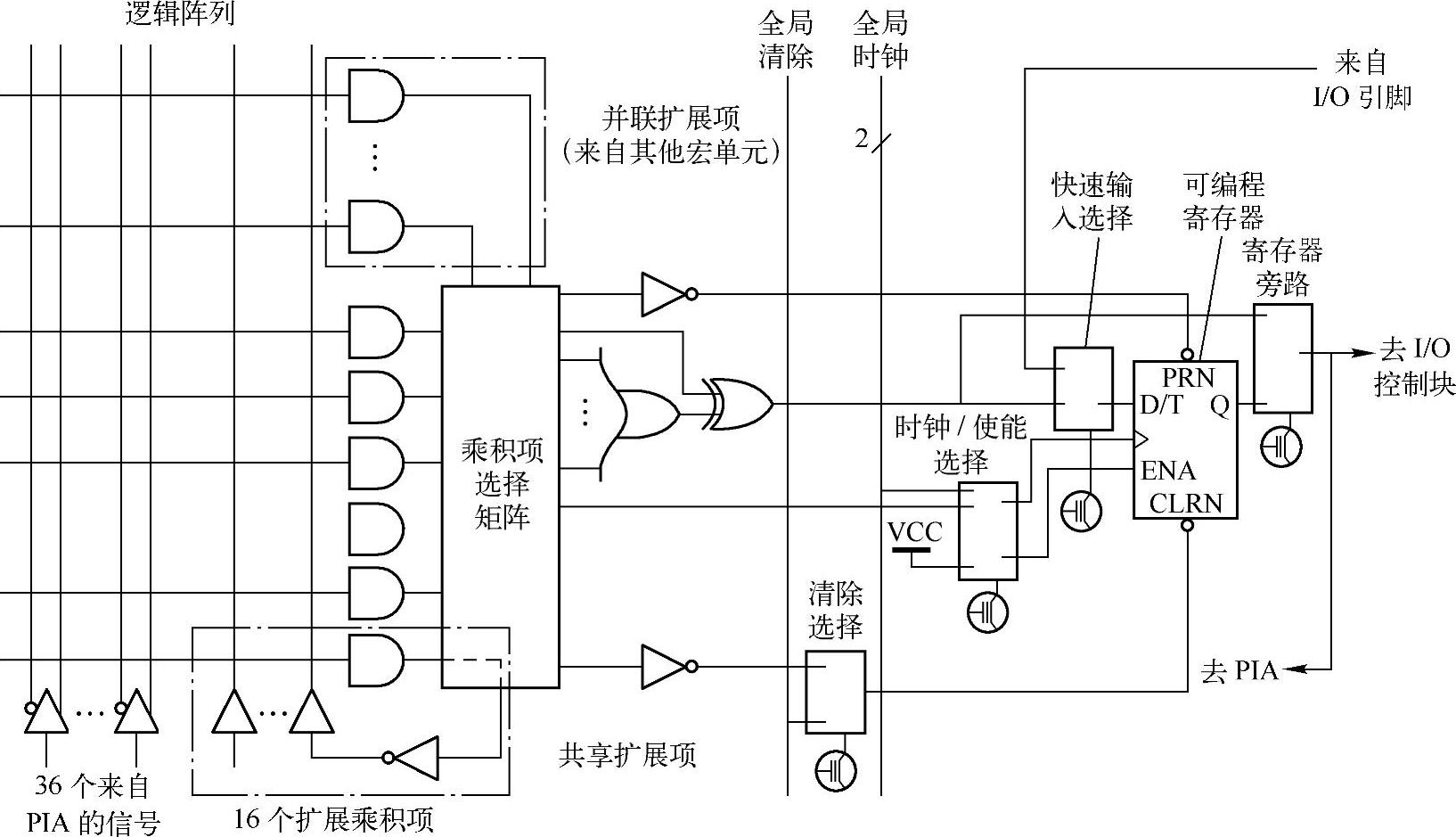

MAX7128S的逻辑宏单元是PLD的基本组成结构,由逻辑阵列、乘积项选择矩阵和可编程寄存器3部分组成,可编程实现组合逻辑和时序逻辑。

逻辑阵列用于实现组合逻辑,为宏单元提供5个乘积项。每个逻辑阵列块LAB又是由16个逻辑宏单元组成的阵列,MAX7128S宏单元的结构如图3-13所示。每个宏单元中有一组共享扩展乘积项,经非门后反馈到逻辑阵列中;还有一组并行扩展乘积项,从邻近宏单元输入。

图3-13 MAX7128S宏单元结构图

乘积项选择矩阵把逻辑阵列提供的乘积项有选择地提供给“或门”和“异或门”作为输入,实现组合逻辑函数;或作为可编程寄存器的辅助输入,用于清0、置位、时钟、时钟使能控制。

可编程寄存器用于实现时序逻辑,可配置为带可编程时钟的D、T、JK、SR触发器,或被旁路掉实现组合逻辑。触发器有3种时钟输入模式:全局时钟模式,全局时钟输入直接和寄存器的CLK端相连,实现最快的输出;全局时钟带高电平有效时钟使能信号模式,使用全局时钟,但由乘积项提供的高电平有效的时钟使能信号控制,输出速度较快;乘积项时钟模式,时钟来自I/O引脚或隐埋的宏单元,输出速度较慢。

寄存器支持异步清0和异步置位,由乘积项驱动的异步清0和异步置位信号高电平有效,而寄存器的复位端由低电平有效的全局复位专用引脚GCLRn信号来驱动。

(3)扩展乘积项XPT

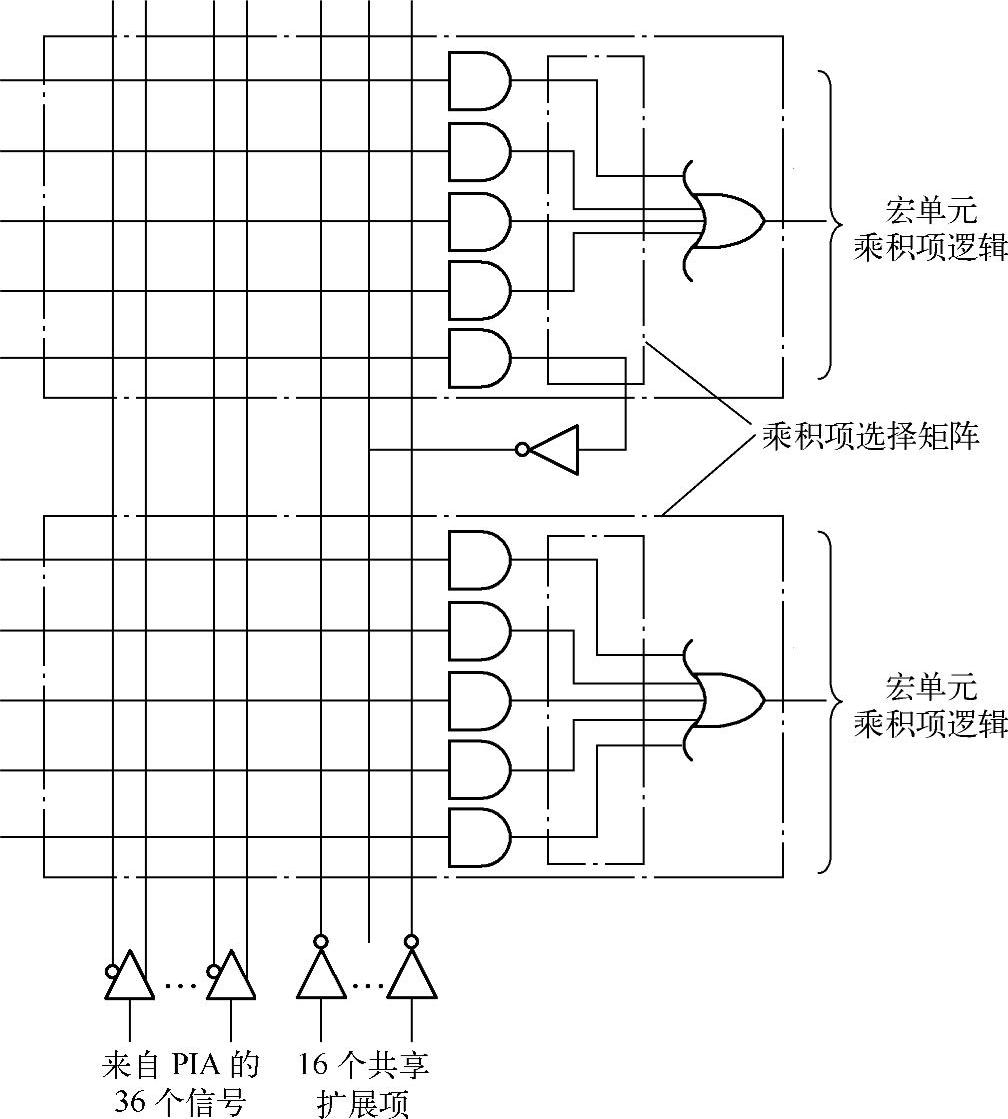

MAX7128S中,有共享扩展乘积项和并行扩展乘积项,如图3-14所示,用于复杂逻辑函数的构造。

图3-14 MAX7128S共享扩展项(https://www.xing528.com)

每个LAB有16个共享扩展乘积项,共享扩展项由每个宏单元提供一个单独的乘积项,经非门后反馈到逻辑阵列中,LAB的宏单元都能共享这些乘积项。但采用共享扩展乘积项后有附加延时。

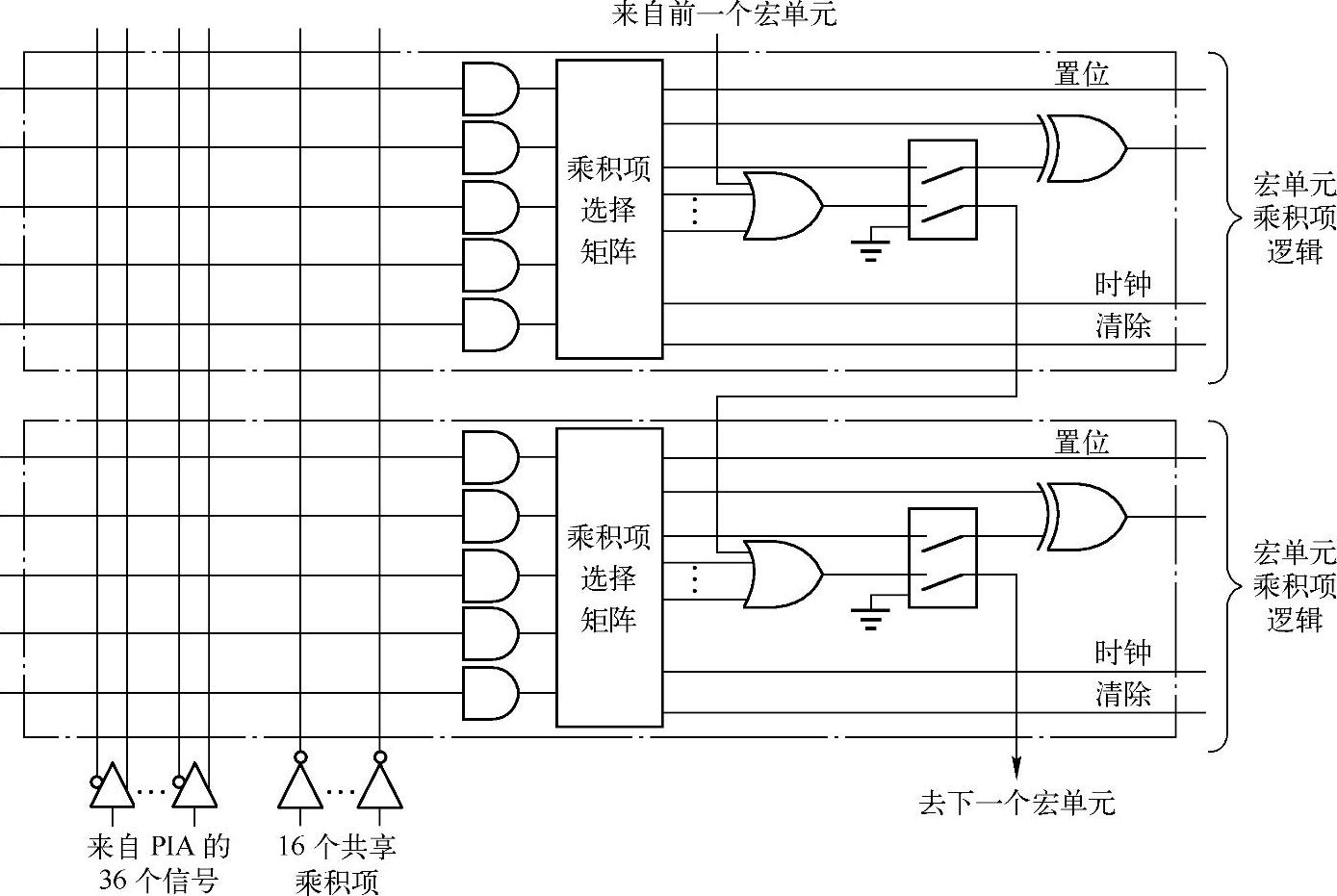

并行扩展乘积项如图3-15所示,是宏单元中一些没有使用的乘积项被分配到邻近的宏单元。使用并行扩展乘积项后,允许最多20个乘积项送宏单元的“或门”。

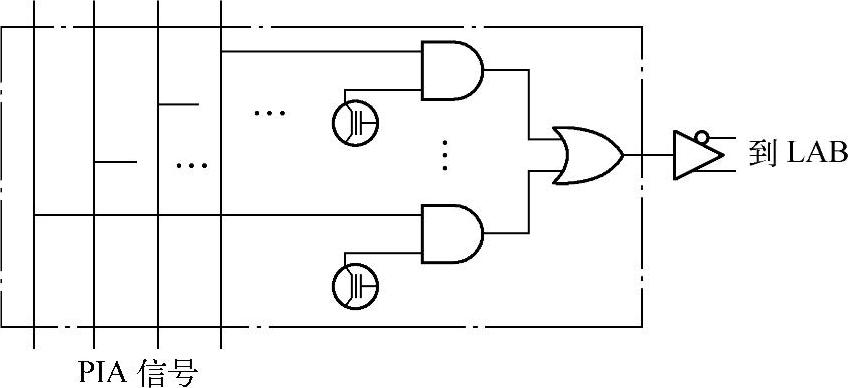

(4)可编程连线阵列(PIA)

通过PIA把各LAB相互连接可构成所需的逻辑。通过PIA可把器件中任一信号源连接到其目的地,所有MAX7128S的专用输入、I/O引脚和宏单元输出均馈送到PIA,PIA可把这些信号送到器件内的各个地方。只有每个LAB所需的信号才真正给它布置从PIA到该LAB的连线。图3-16表示了PIA的信号是如何布线到LAB的,E2PROM控制二输入与门的一个输入端,以选择驱动LAB的PIA信号。

(5)I/O控制块

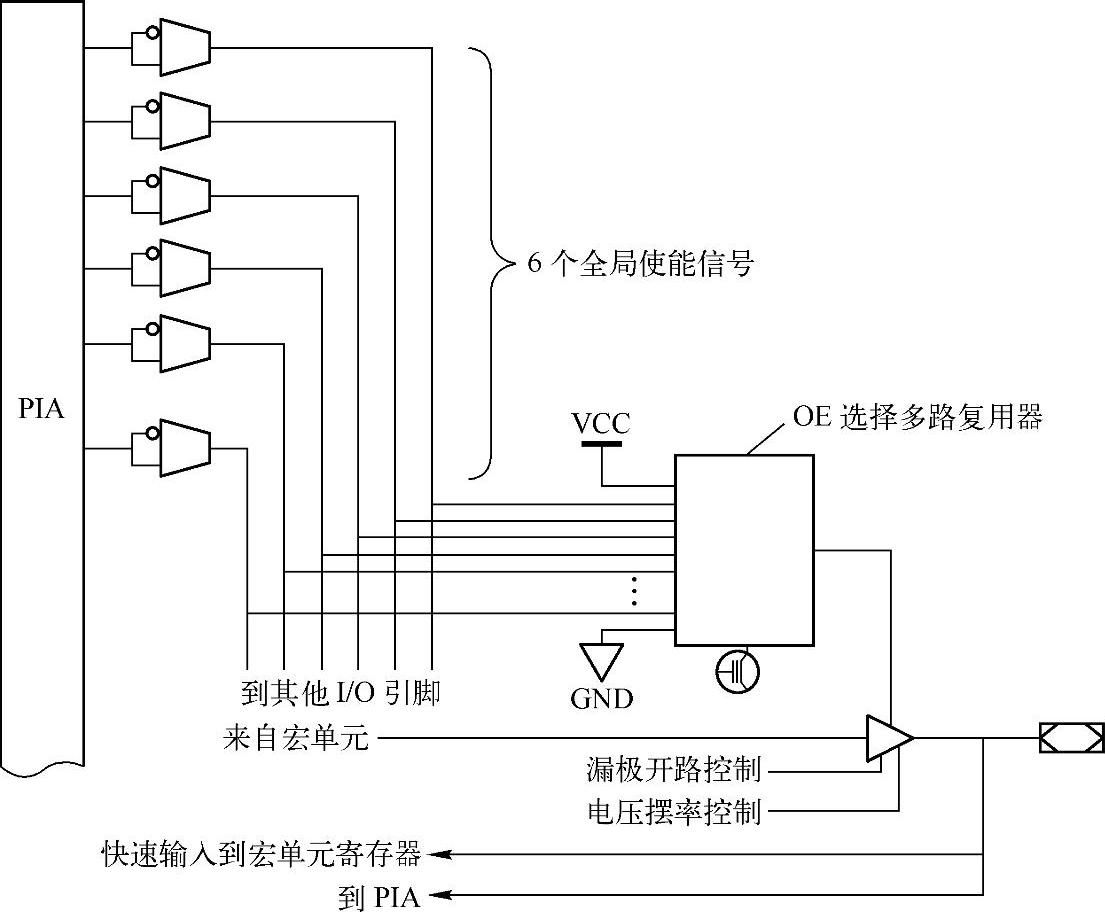

I/O控制块把每个引脚单独配置成所需工作方式,包括输入、输出和双向3种工作方式,其结构如图3-17所示。

图3-15 MAX7128S并联扩展乘积项

三态缓冲器的控制端接GND时,其输出为高阻态,I/O引脚可作为专用输入引脚使用;三态缓冲器的控制端接VCC时,表示是输出使能,I/O引脚可作为专用输出引脚使用;三态缓冲器的控制端接全局输出使能信号时,通过高低电平的控制,可实现输入输出双向工作方式,如图3-17所示。

图3-16 MAX7128S的PIA结构

图3-17 MAX7128S的I/O控制块

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。