层次化设计也称为“自底向上”的设计方法,即将一个大的设计项目分解为若干个子项目或若干个层次来完成。先从底层的电路设计开始,然后在高层次的设计中逐级调用低层次的设计结果,直至最后系统电路的实现。对于每个层次的设计结果,都经过严格的仿真验证,尽量减少系统设计中的错误。与传统的数字电路设计法相比,在EDA设计中,更容易实现层次化设计。其一般步骤是:先利用原理图输入法或硬件描述语言实现底层电路的设计,然后利用原理图输入法,将多个设计元件连接起来,实现多层次系统电路的设计。这种设计方法使得系统设计变得比较直观,另外,由于EDA设计将传统电路设计过程的电路布线、印制电路板绘制、电路焊接等过程取消,提高了设计效率,降低了设计成本,也减轻了设计者的劳动强度。下面通过4位串行进位加法器的设计介绍层次化设计方法。

例2.1 4位串行进位加法器设计。

4位加法器可以用4个1位全加器构成,它的底层设计文件是1位全加器,4位加法器是高层次设计的结果。其设计步骤如下:

①建立4位串行进位加法器工程项目adder4,并将顶层设计项目用adder4表示。

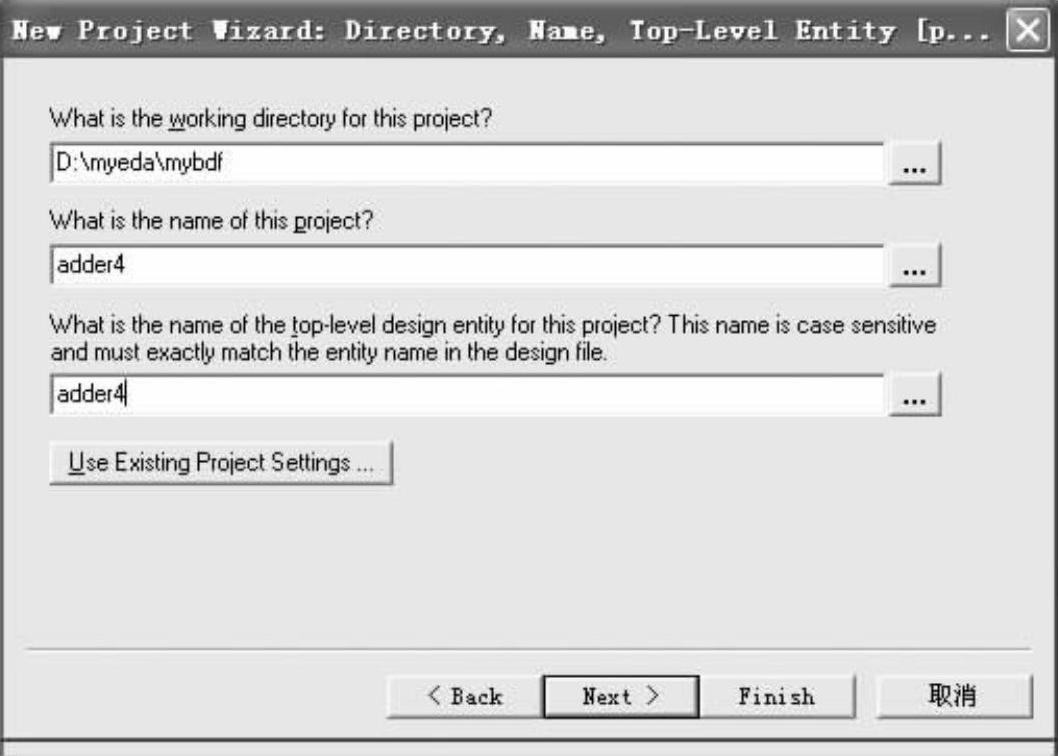

在QuartusII主窗口,从“File”菜单下选择“New Project Wizard…”,出现如图2-28所示的建立新设计项目的对话框。在对话框的第一栏中输入设计工程项目所在的文件夹名;在第二栏中输入新的设计工程项目名adder4;在第三栏中输入设计系统的顶层文件实体名adder4。

图2-28 建立新设计项目的对话框

②用原理图输入法设计1位全加器adder,并为1位全加器生成一个元件符号adder,这可以参考上一节的内容。

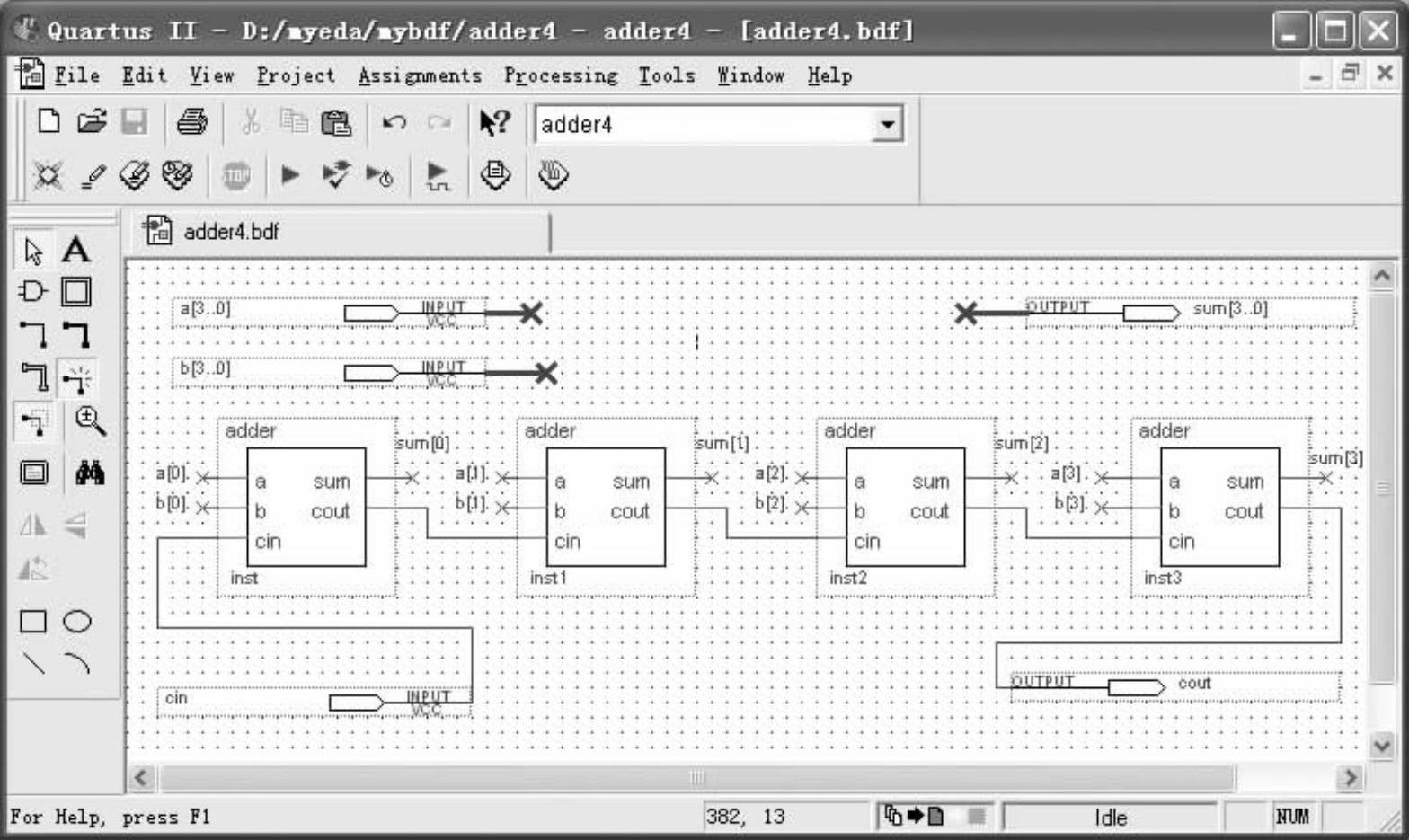

③打开一个新的原理图编辑窗口,在编辑窗口中,双击鼠标左键,在弹出的元件选择对话框的用户工程目录中,选择上述步骤②设计完成的如图2-11的1位全加器元件共4个,然后根据4位串行进位加法器的原理图,构成如图2-29所示的4位加法器电路,并以文件“adder4.bdf”存在工程目录中。(https://www.xing528.com)

图2-29 4位串行进位加法器原理图

在如图2-29所示原理图中,4位加法器输入符号a[3..0]的右边连接了一条粗的信号线,表示该信号线与有a[3]~a[0]文字标注的4个全加器的a输入端连接;b[3..0]输入符号的右边连接了一条粗的信号线,表示该信号线与有b[3]~b[0]文字标注的4个全加器的b输入端连接;输出符号sum[3..0]的左边连接了一条粗的信号线,表示该信号线与有sum[3]~sum[0]文字标注的4个全加器的sum输出端连接。

粗线表示由多条信号线组成的总线,而细线表示单信号线。用鼠标右键单击信号线,在弹出的对话框中,单击“Bus Line”即可设置总线。需要在信号线上加文字标注时,只要按住鼠标左键将信号线拉长,然后在旁边输入文字标注就可以了。

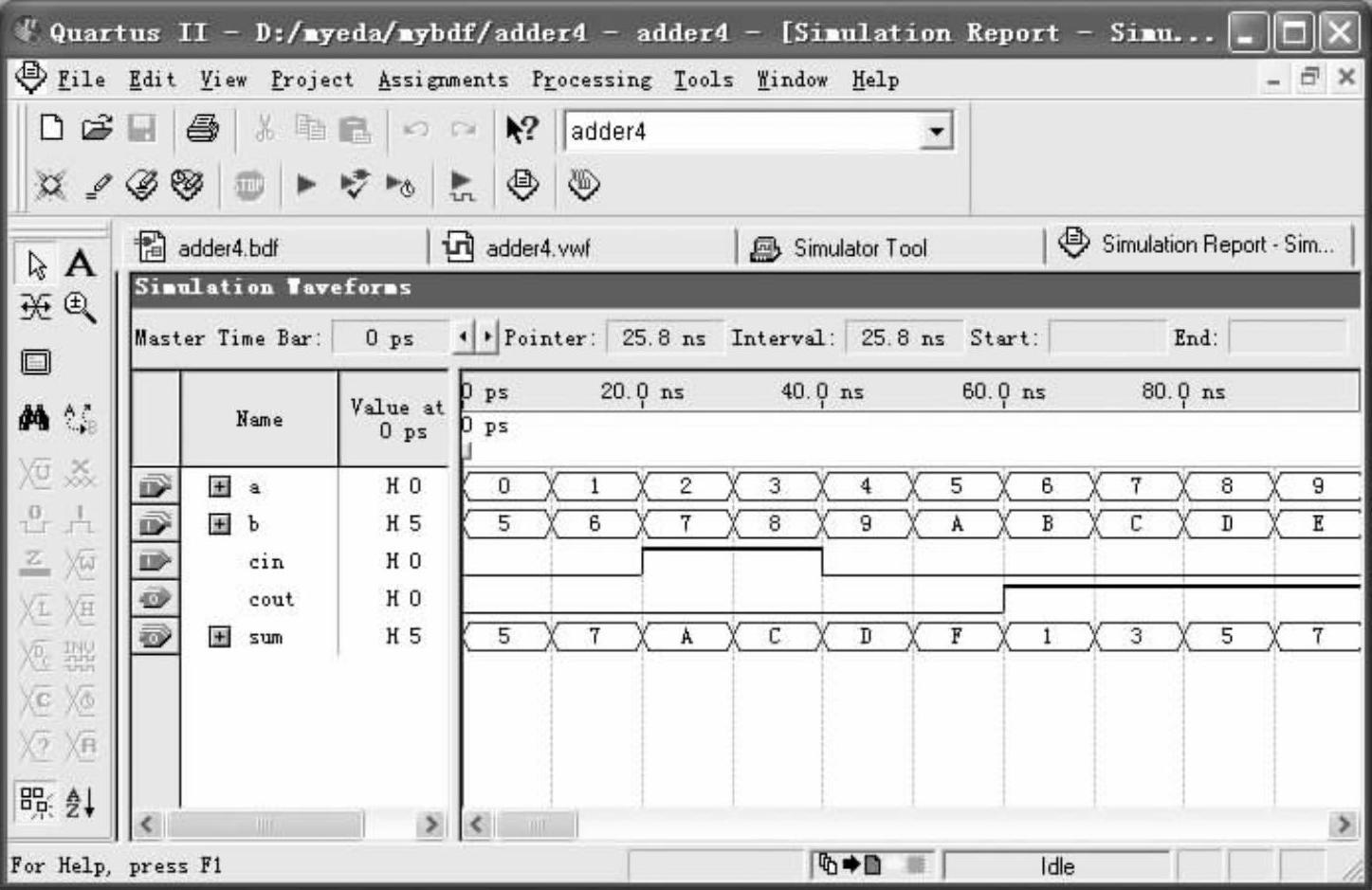

完成4位加法器原理图编辑后,编译工程项目adder4,然后建立波形仿真文件,对4位加法器设计电路进行验证,功能仿真波形如图2-30所示。在图2-30所示的仿真波形中,a[3..0]和b[3..0]表示4条输入信号线,分别代表两个4位二进制被加数、加数输入,它们相加之和由sum[3..0]输出,向高位的进位由cout输出。从仿真波形可以看出所设计电路的逻辑功能是正确的。

图2-30 4位加法器仿真波形图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。