编程下载设计文件包括引脚锁定和编程下载两个部分。

1.引脚锁定

在目标芯片确定后,为了把设计电路的编程文件下载到目标芯片“EP1K30QC208-2”中,还需要确定引脚的连接,即指定设计电路的输入/输出端口与目标芯片哪一个引脚连接在一起,这个过程称为“引脚锁定”。

在目标芯片引脚锁定前,需要根据使用的EDA硬件开发系统的引脚信息(参考附录A ZY11EDA13BE型EDA技术实验箱简介),确定设计电路的输入和输出端与目标芯片引脚的连接关系,再进行引脚锁定,以便能够对设计电路进行实际测试。

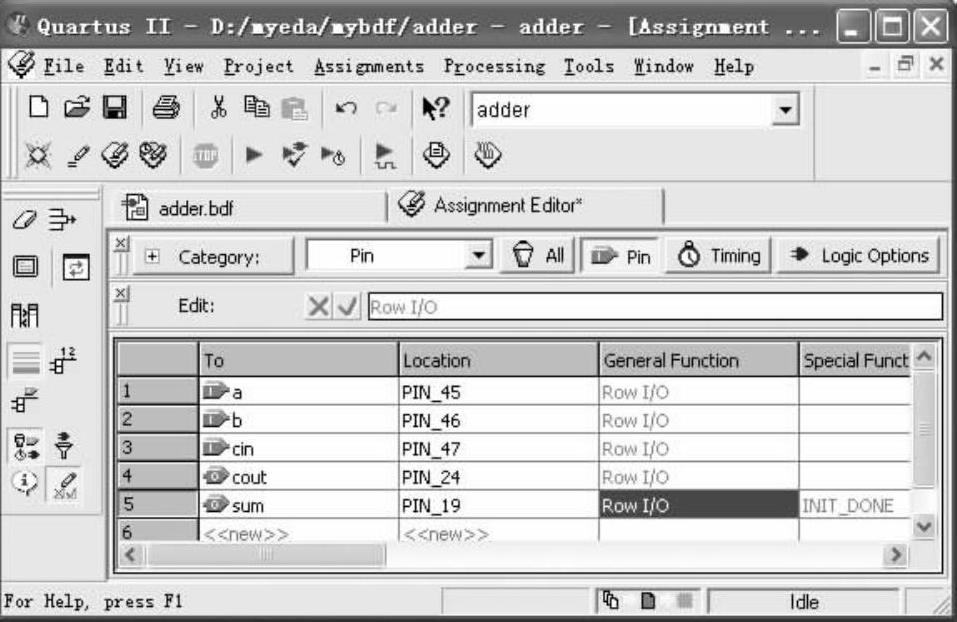

1)执行“Assignments”项中的赋值编辑“Assignments Editor”命令,弹出如图2-21所示的赋值编辑对话框,在对话框的“Category”栏目选择“Pin”项。

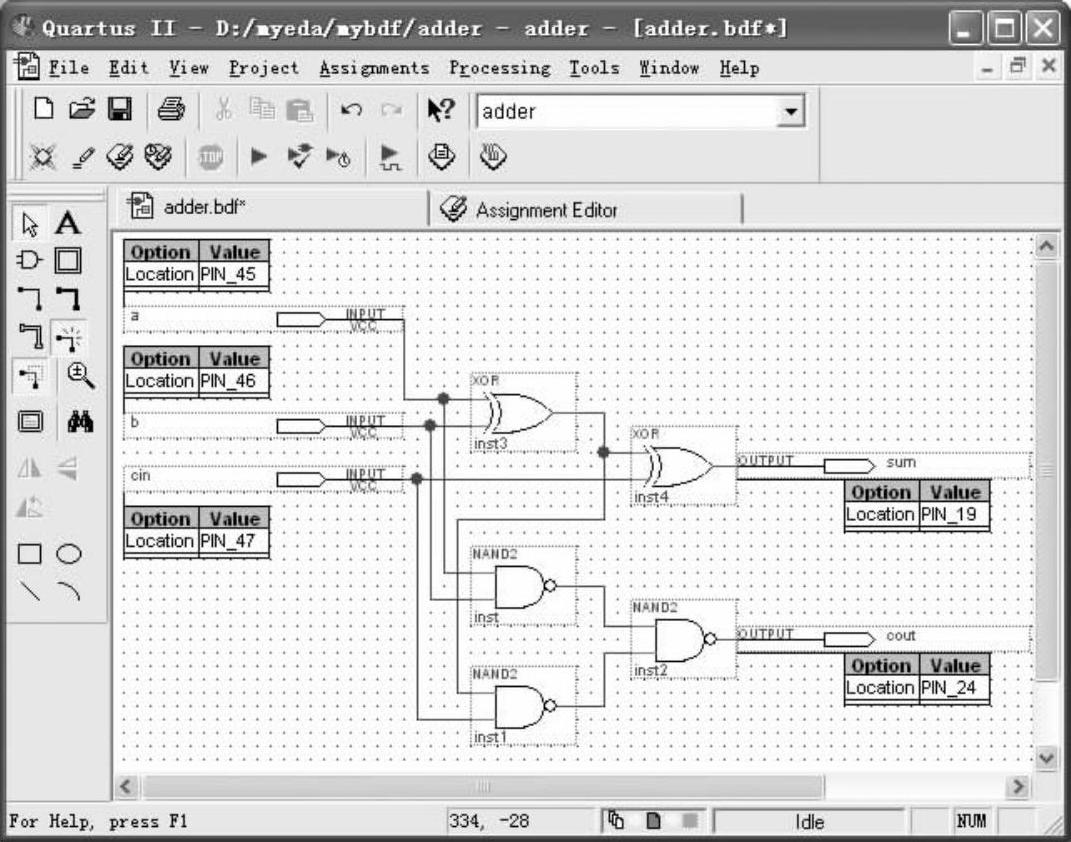

2)用鼠标双击“To”栏目下的“<<new>>”,在其下拉菜单中列出了设计电路的全部输入和输出端口名,例如,全加器的a、b、cin、cout和sum端口等。用鼠标选择其中的一个端口后,再用鼠标双击“Location”栏目下的“<<new>>”,在其下拉菜单中列出了目标芯片全部可使用的I/O端口,然后根据EDA开发系统的实际引脚信息用鼠标选择其中的一个I/O端口。例如,全加器的三个输入端a、b、cin,分别选择Pin_45、Pin_46、Pin_47(相当于ZY11EDA13BE型EDA实验箱上的高低电平输入键“K1”、“K2”、“K3”);全加器的两个输出端和“sum”和进位“cout”端口,分别选择Pin_19和Pin_24(相当于ZY11EDA13BE型EDA实验箱上的发光二极管“LED1”、“LED2”)。赋值编辑操作结束后,完成引脚锁定,如图2-21所示,存盘并关闭此窗口。完成引脚锁定后,相应的全加器原理图文件“adder.bdf”也增加了引脚信息,如图2-22所示。

图2-21 赋值编辑对话框

图2-22 引脚锁定后的全加器原理图

3)锁定引脚后还需要对设计文件重新编译,即执行主菜单“Processing”下的“Start Compilation”命令,产生设计电路的下载文件。对于CPLD,编程文件为熔丝图文件(.pof);而对FPGA,编程文件为位流数据文件(.sof)。

2.时序仿真

时序仿真使用包含延时信息的编译网表,不仅测试逻辑功能,还测试设计的逻辑在目标器件中最差情况下的时序关系,它和器件的实际情况基本一致,因此对整个设计项目进行时序仿真,分析其时序关系,评估设计的性能是非常重要的。

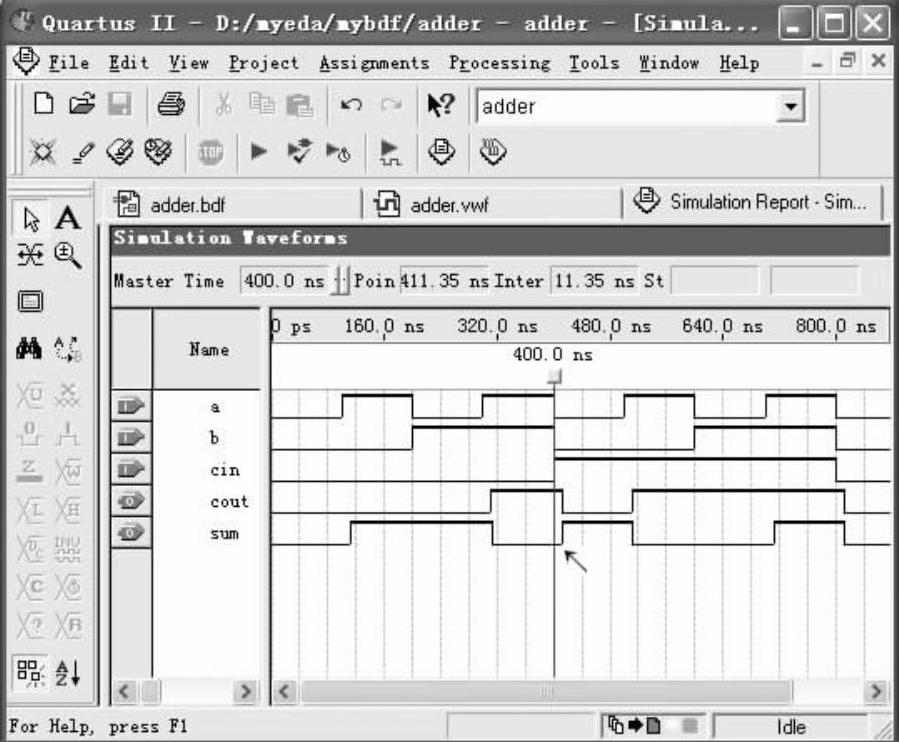

完成引脚锁定并对设计文件重新编译后便可以对设计文件进行时序仿真了。进行时序仿真的步骤和功能仿真的步骤基本相同,只是进行时序仿真时应首先在上述图2-19所示“Simulator Tool”对话框的选项“Simulation mode:”中,选择仿真类型为“Timing”。1位全加器的时序仿真波形如图2-23所示。

从时序仿真波形中不仅可以分析设计电路的正确性,还可以观察设计电路的延时。图2-23左侧的竖线是测试参考线,它上方标出输入a发生变化的时刻是400.0ns,是此线所在的时间坐标位置,鼠标指出的位置是输出sum的时间坐标,为411.35ns,测试参考线与鼠标箭头间的时间差显示在窗口上方的“Interval”小窗中,窗中的数字表示测量出的输入信号与输出响应之间的时间延时量为11.35ns。

图2-23 一位全加器的时序仿真波形

3.编程下载设计文件(https://www.xing528.com)

上述的仿真仅是用来检查设计电路的逻辑功能是否正确,要真正检验设计电路的正确性,必须将设计编程文件下载到实际芯片中进行检验、测试。

在编程下载设计文件之前,需要将硬件测试系统(例如ZY11EDA13BE型EDA技术实验箱)通过计算机的并行打印机接口与计算机连接好,打开电源。

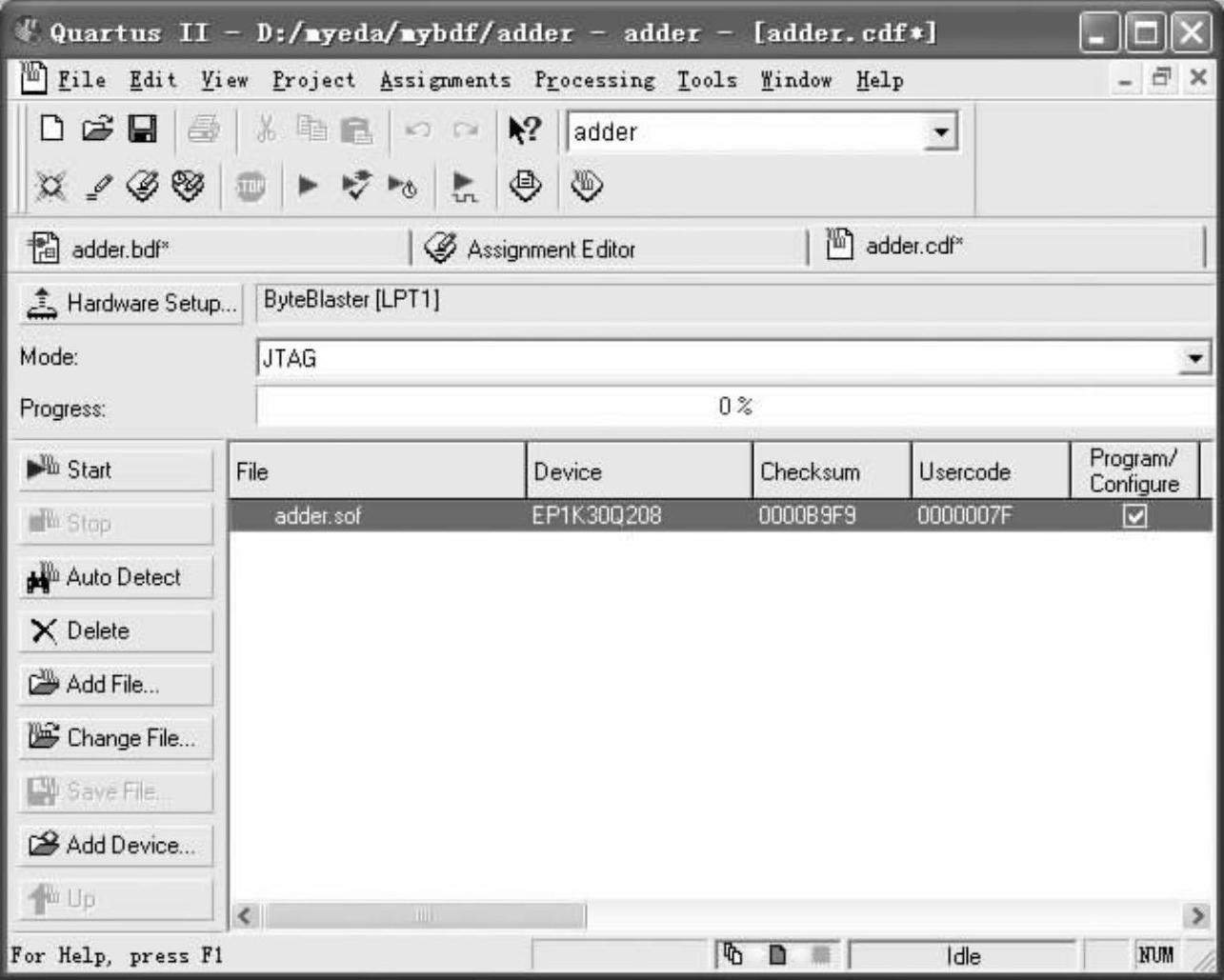

首先设定编程方式。选择“Tools”的编程器“Programmer”命令,弹出设置编程方式窗口,如图2-24所示。

图2-24 设置编程方式窗口

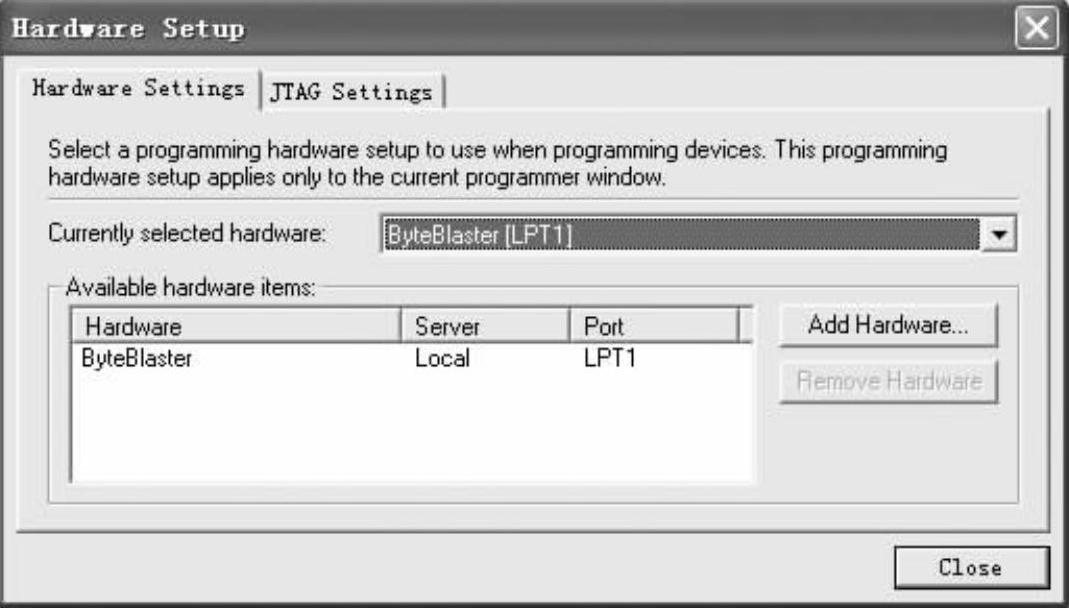

(1)设置硬件

在设置编程方式窗口,用鼠标单击“Hardware Setup…”(硬件设置)按钮,弹出“Hardware Setup”硬件设置对话框,如图2-25所示。在对话框中按下“Add Hardware…”按钮,在弹出的添加硬件对话框中选择ByteBlasterMV编程方式后按“Close”按钮。Byte-BlasterMV编程方式对应计算机的并行口编程下载通道,“MV”是混合电压的意思,主要指针对Altera公司的各类芯片电压的FPGA/CPLD都能由此编程下载。

图2-25 硬件设置对话框

(2)选择下载文件

用鼠标单击下载方式窗口左边的“AddFile”(添加文件)按钮,弹出“Select Program-mingFile”(选择编程文件)对话框,如图2-26所示,选择全加器设计工程目录下的下载文件“adder.sof”(注:在选择下载文件时,对于FPGA,如EP1K30QC208-2,选择的是配置文件,文件类型为.sof,如adder.sof;对于CPLD,如EPM7128SLC84-10或FPGA的配置芯片,如EPC2,选择的是编程文件,文件类型为.pof,如adder.pof)。

图2-26 选择下载文件对话框

(3)编程下载

在设置编程方式窗口,选中需要编程的“adder.sof”文件对应的“Program/Configure”选项,即单击“Program/Configure”选项下的小方框,如图2-27所示,然后单击编程器窗口的“Start”按钮,开始编程,编程结束时有提示信息出现。

图2-27 编程下载窗口

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。