QuartusⅡ编译器主要完成设计项目的检查和逻辑综合,将项目的最终设计结果生成器件的下载文件,并为模拟和编程产生输出文件。

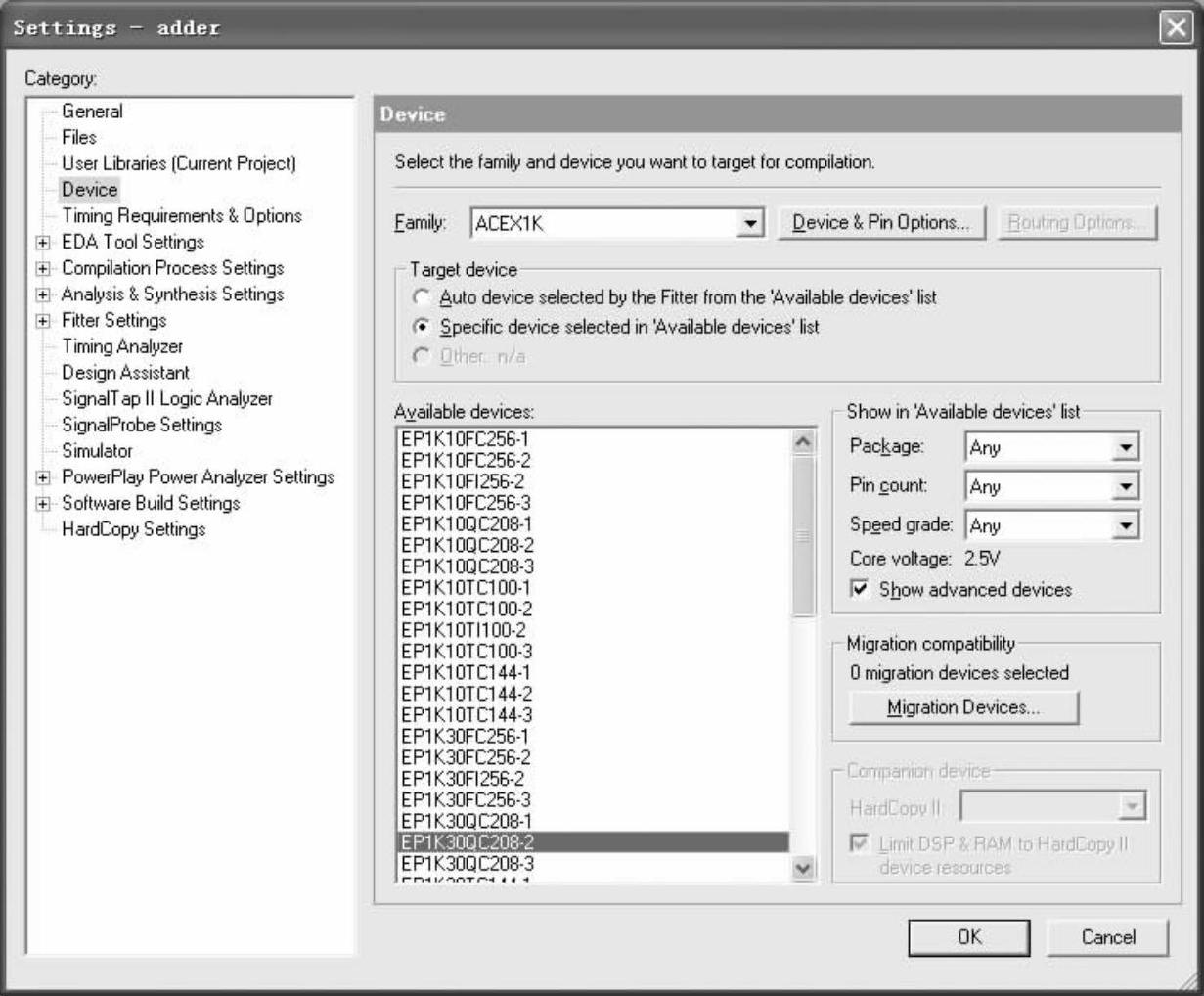

在编译设计文件前,应先选择下载的目标芯片,否则系统将以默认的目标芯片为基础完成设计文件的编译。在QuartusⅡ主窗口,执行“Assignments”菜单下的“Device”命令,出现如图2-8所示的目标芯片选择对话框。在“Family:”栏目中选择目标芯片系列名,如“ACEX1K”,然后在“Available devices:”栏目中用鼠标点黑选择的目标芯片型号,如“EP1K30QC208-2”,单击“OK”按钮选择结束。

图2-8 目标芯片选择对话框

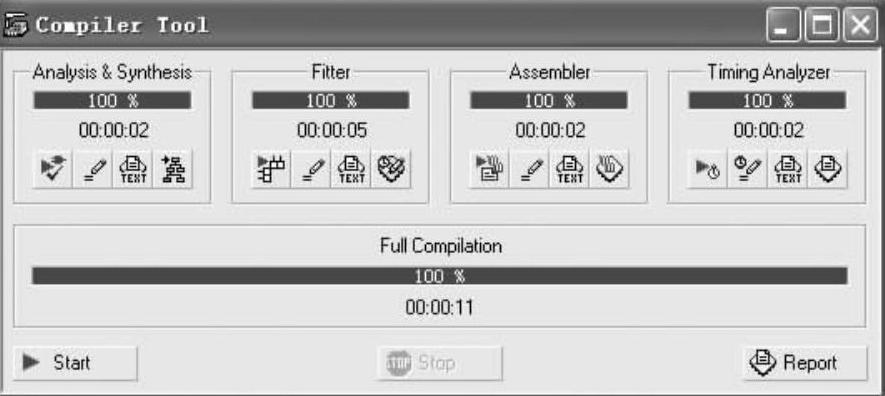

目标芯片选定后,执行QuartusⅡ主窗口“Tools”菜单下的“CompilerTools”命令,出现如图2-9所示的QuartusⅡ的编译器窗口,选择主菜单“Processing”下的“Start Compila-tion”命令或单击图2-9所示QuartusⅡ编译器窗口左下角的“Start”按钮,即可对“adder.bdf”文件进行编译。

(https://www.xing528.com)

(https://www.xing528.com)

图2-9 QuartusⅡ的编译器窗口

QuartusII的编译器窗口包含了对设计文件处理的全过程。“Analysis&Synthesis”(分析和综合)模块创建工程项目数据库,对设计文件进行逻辑综合,完成设计逻辑到器件资源的技术映射。“Fitter”(适配)模块完成布局布线工作。“Assembler”模块产生多种形式的器件编程映象文件,包括.pof、.sof等,可以通过QuartusⅡ软件和编程电缆(ByteBlaster或MasterBlaster)将.pof或.sof文件写入到CPLD或FPGA中。“Timing Analyzer”模块用于计算设计在给定器件上的延时,将延时信息注释到网表文件中,并完成设计的时序分析和所有逻辑的性能分析。“EDA Netlist Writer”模块产生用于第三方EDA工具的网表文件及其他输出文件。

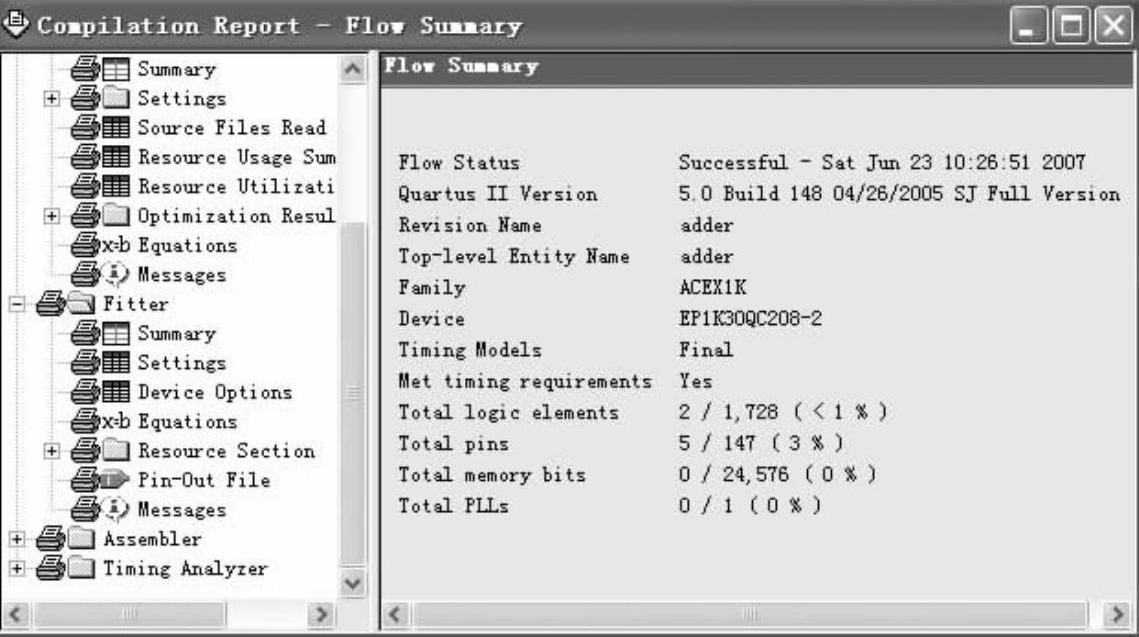

在编译过程中,编译状态窗口将显示全编译过程中各个模块和整个编译进程的进度以及所用的时间;信息窗口将显示编译过程中的信息以及设计中出现的错误等。单击图2-9所示QuartusⅡ的编译器窗口右下角的“Report”按钮,会出现图2-10所示的编译报告窗口,在左边窗口选择要查看的部分,报告内容会在右边窗口显示出来。

图2-10 编译报告窗口

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。