1.去耦合旁路设计

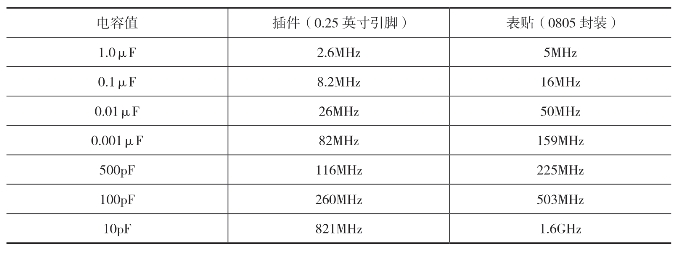

如果器件工作频率为20MHz以下,则通常选择0.1μF的电源去耦电容,否则选用0.01μF甚至更小容量的电源去耦电容。另外需要特别注意,去耦电容的自谐振频率必须高于抑制电路谐波的频率。瓷片电容的自谐振频率如表4-1所示。为了提高抑制干扰的带宽,可将两个不同数量级(如0.1μF和0.001μF,容值相差100倍)的电容并联使用。

表4-1 电容的自谐振频率

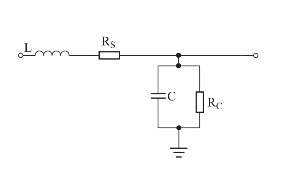

图4-4 单传输线非理想等效电路

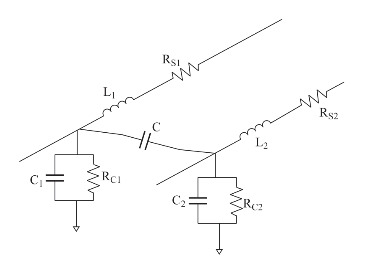

图4-5 并行传输线非理想等效电路

在设计PCB时,电源输入端可接入10~100μF电容,电容容量越大,抗干扰效果越好;每个芯片的电源端跨接0.01μF的瓷片电容,或者4~10个芯片的公共电源端跨接一个1~10μF钽电容(高频阻抗很小,在500kHz~20MHz范围内阻抗小于1Ω,漏电流小于0.5μA);对于抗噪声能力弱、关断时电流变化大的器件,应在其的电源端跨接去耦电容;去耦电容的引线尽量短,高频旁路电容不能有引线。

2.屏蔽设计

屏蔽就是对两个空间区域之间进行金属隔离,减弱甚至消除两区域的元器件、电路等互相电磁干扰。

印制电路板的常用屏蔽措施如下:

(1)在电磁干扰源和对电磁干扰敏感的电路之间插入导线屏蔽层或分别布设屏蔽罩并连接到电路板的基准电位上。

(2)在印制电路板周边布设地线具有一定的屏蔽效果。

(3)在印制电路板之间设置屏蔽板,并接到电路板的基准电位上。

(4)对于多层板,可将易产生辐射干扰的PCB置于不易产生辐射干扰的PCB下面。

(5)印制电路板上较长的信号线的两边应布设地线或覆地线层,避免其成为干扰辐射天线。

(6)印制电路板与较远外围设备通信时,应用屏蔽线连接。

(7)对于容易产生干扰辐射的电路,应单独将其屏蔽。(https://www.xing528.com)

(8)如果信号电路为单点接地,则低频线的屏蔽层也应一点接地,否则将形成噪声源。

(9)如果信号源与放大器有一个接地,则输入端的屏蔽应与放大器的公共端相连。

3.接地设计

由传输线理论可知,当地线的长度接近信号波长的1/4时,它就相当于终端短路的传输线,不仅接地作用失效,而且将产生较强的天线效应,辐射干扰信号。所以地线长度不能超过信号波长的1/20。

(1)接地方式。

①单点接地。在整个电路系统中,所有需要接地的单元电路只连接到一个接地参考点。单点接地可分为串联单点接地和并联单点接地。

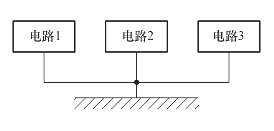

a.串联单点接地。容易引起公共阻抗干扰,不宜采用。串联式单点接地示意图如图4-6所示。

图4-6 串联式单点接地示意图

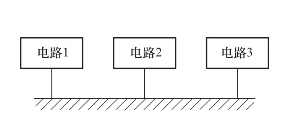

b.并联单点接地。只适用于低频,能有效地避免各电路间的公共阻抗干扰。并联单点接地示意图如图4-7所示。

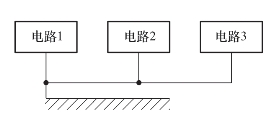

②多点接地。各个电路单元接地点都分别就近接到地平面(设备底板或系统的地导线)上。由于地线较短,适用于高频电路。多点接地示意图如图4-8所示。

图4-7 并联式单点接地示意图

图4-8 多点接地示意图

③混合接地。电路系统中既有单点接地又有多点接地。如果系统的频带很宽,对于低频电路单元需单点接地,对于高频电路单元需多点接地,则可以采用混合接地。

④悬浮接地。悬浮接地(浮地)是指电路系统的地线与电子产品壳体连接的大地系统相互绝缘。浮地易产生静电放电,易受空间耦合干扰。通信系统和一般电子产品不宜浮地。

(2)抑制地线干扰的措施。地线造成电磁干扰的原因是地线存在阻抗,使地线各处不再是等电位而产生地线噪声,形成地线环路干扰。抑制地线干扰的方法如下:将一端的设备浮地,切断地线电流的返回路径;用变压器实现电路设备之间的连接;使用光隔离器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。