1.同步七进制计数器的设计

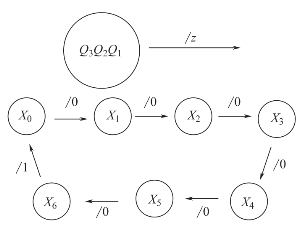

同步七进制计数器有七种稳定状态,记忆这些状态至少需要三个触发器。三个触发器构成的状态编码分别为:X0=000,X1=001,X2=010,X3=011,X4=100,X5=101,X6=110,X7=111。为了设计电路方便,选择前七种编码作为七进制计数器的状态编码,剩余的另外一种编码“111”作为无关状态处理。Z表示进位输出。由此可以得到七进制计数器的原始状态转换图(图3-3)。

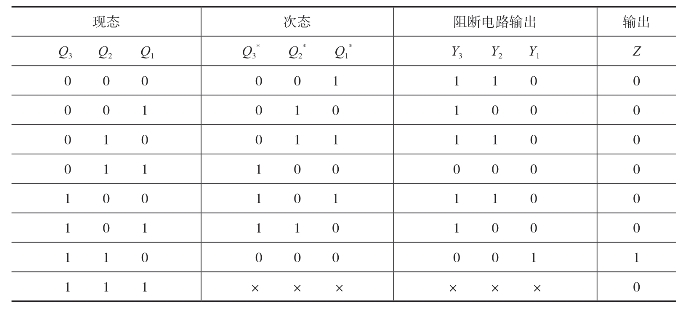

根据上述原始状态转换图可得七进制计数器的状态转换和触发器状态变化表,如表3-1所示。

表3-1 七进制计数器的状态转换和触发器状态变化表

如果选用D触发器,利用其特征方程Q*=D,根据状态转换和触发器状态变化表可以写出七进制计数器的状态方程和输出方程,并利用卡诺图化简后得:

Q3*=Q3·Q′2+Q2·Q1

Q2*=Q′3·Q2·Q′1+Q′2·Q1

Q1*=Q′3·Q′1+Q′2·Q′1

Z=Q3·Q2

根据状态方程可以写出驱动方程:

D3=Q3·Q′2+Q2·Q1

D2=Q′3·Q2·Q′1+Q′2·Q1

D1=Q′3·Q′1+Q′2·Q′1

(https://www.xing528.com)

(https://www.xing528.com)

图3-3 计数器的原始状态转换图

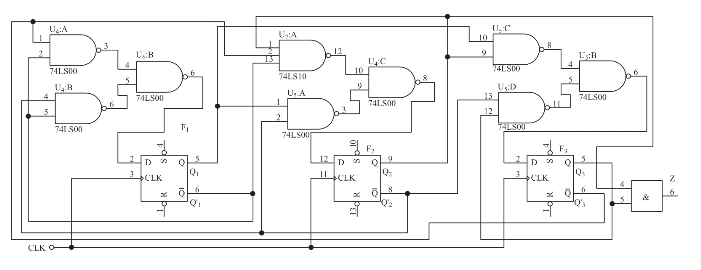

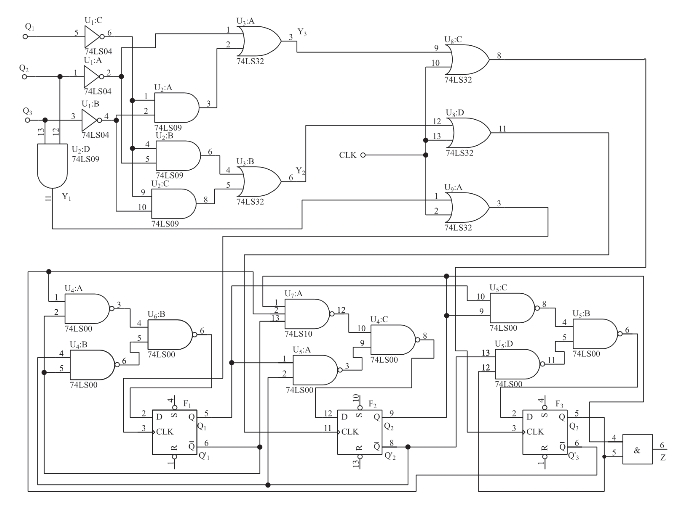

根据驱动方程和输出方程,可以画出同步七进制计数器的电路图,如图3-4所示。

图3-4 同步七进制计数器的电路图

2.时钟阻断电路的设计

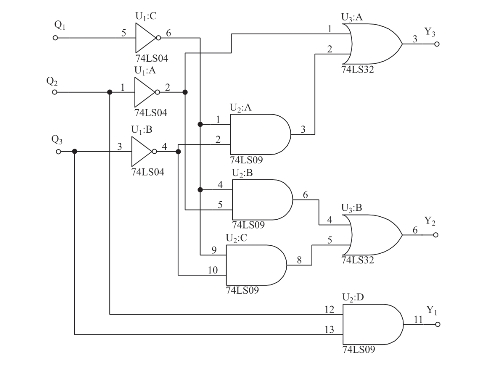

根据七进制计数器的状态转换和触发器状态变化表可以写出各个触发器时钟阻断电路输出逻辑函数式:

Y3=Q′2+Q′3·Q′1

Y2=Q′2·Q′1+Q′3·Q′1

Y1=Q3·Q2

根据时钟阻断电路输出逻辑函数式,可以画出相应的电路图,如图3-5所示。

图3-5 时钟阻断电路

将时钟阻断电路与同步七进制计数器的电路组合起来可以得到低功耗电路图,如图3-6所示。

图3-6 具有时钟阻断的低功耗同步七进制计数器电路图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。