1.标幺化和Q化

由前面章节介绍的关于矢量控制算法分析和仿真可知,在矢量控制中存在着大量的浮点数运算。通常,TMS320F2812定点处理器在实现浮点运算时主要有两种方法:①定义变量为float类型;②对变量进行Q化处理。方法①会大大降低软件效率和实时性;方法②的Q化是将浮点数左移n位进行放大,即乘以2n,以移位后的整数部分来代表该数值。

在对参与矢量运算的各变量进行Q化处理时,可发现由于各物理量实际值有很大的差别,Q值的选取各不相同,这将在实际应用时带来相当大的麻烦。在保证各个变量Q化准确度要求时,几个量的Q值取值相差很大,运算结果准确度以及数据溢出等问题难以保证。因此,在进行高性能的矢量算法编程之前,需要分析异步电动机标幺值模型。通过选择合适的基准值,对各个参数进行标幺化处理,使参与运算的参数处于同一数量级,可大大简化编程、便于计算。同时,标幺化处理也使得对不同对象的电动机,只需输入电动机的铭牌值,而不需要更改具体程序,实现矢量控制程序的通用性。

程序中选择电压、电流和角速度为三个独立的基本物理量,其他各物理量均可由这三者推出,即选择额定相电压峰值、额定线电流峰值和与50Hz对应的角速度为基准值。

标幺化具体公式有

时间基准值:t_base=1/w_base;

电阻基准值:r_base=v_base/i_base;

电感基准值:l_base(Q16)=r_base/w_base;

磁通基准值:fx_base=v_base/w_base;

转矩基准值:te_base=fx_base∗i_base;

转动惯量基准值:j_base=te_base/(w_base)^2。

选择上述基准值进行标幺化处理之后,所有参加运算的参数都在1附近不大的范围内变动,易保证运算的准确度,也易于保证数据不溢出。同时,也为浮点运算的Q格式选择提供了便利。

系统中所有物理量标幺值统一采用Q24格式表示,其数值范围为-128~127.999999940,准确度达到了0.000000060,能满足设计要求。

在程序编写中,调用了TI公司提供给用户的浮点运算库函数IQmath。相比同等标准的ANSI(美国国家标准学会)C语言编写的代码,这些函数拥有更快的执行速度。而且,IQmath的使用使得程序的编写大大简化,缩短了程序的开发周期。

2.DSP程序设计

考虑到级联型变换器系统信息量庞大,而且矢量控制算法相对比较复杂,结合项目的后续研发中软件的兼容性和可移植性,在满足调速控制系统实时性要求的前提下,系统采用C语言,在编程中使用模块化的设计方案,每个功能分别由对应的功能模块实现。

图7-19 A/D中断流程图

A/D采样中断程序是矢量控制的核心程序,其流程图如图7-19所示。进入A/D采样中断后首先从结果寄存器中读取需要的转换结果ia、ib、ic,并用坐标变换模块把电流变换到d、q坐标轴,再根据相关公式计算磁链幅值、估计电动机转速、计算转差和同步转速。计算得到同步转速后,积分计算磁链当前角度,并通过查表的方法计算出角度的正余弦值。磁链闭环计算d轴电流给定值,转速闭环计算q轴电流给定值,然后由电流环计算出d、q轴电压,经电压前馈解耦后,通过坐标变换把电压变换为三相静止电压,在DSP完成输出脉冲的计算,然后DSP将驱动脉冲的脉宽值送给FPGA,FPGA产生多路驱动信号,再通过光纤发送给功率单元中的CPLD控制板,驱动开关器件。

3.多载波PWM脉冲发生原理及实现[189,190]

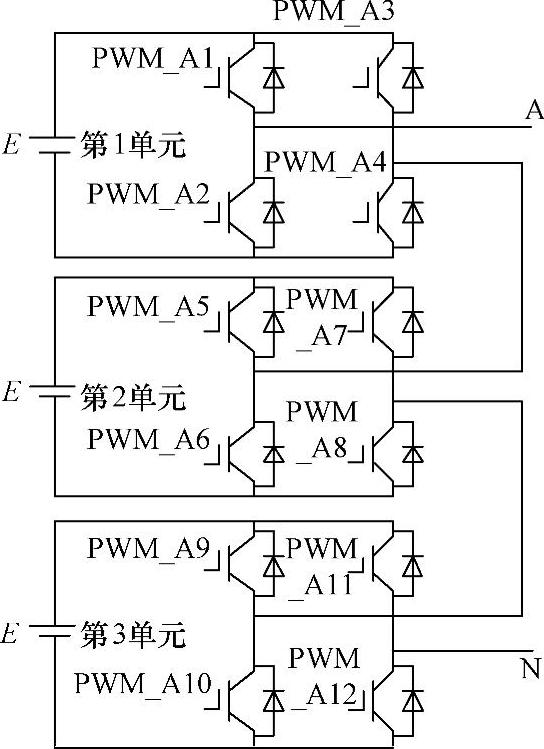

本节介绍以二重化与多载波水平移相相结合的调制策略实现多路驱动脉冲。图7-20所示为三相3功率单元级联型变频器中的A相电路结构。以图7-20为例,对此种调制策略的FPGA实现进行说明。

图7-20 三相3功率单元级联型变频器中的A相电路结构

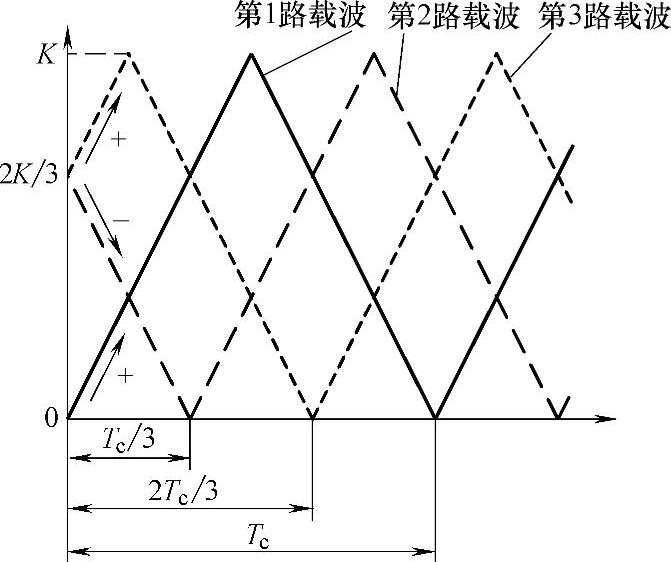

图7-21 与图7-20对应的二重化调制方法与载波相位关系说明

图7-21为与图7-20对应的二重化调制方法与载波相位关系说明。对于N单元串联,第i个三角载波UΔi与第一个载波UΔ1之间的关系可用下式来表示:

UΔi(t)=U[t+(i-1)Tc/N]=UΔ1[t+(i-1)Ts] i=1,2,…,N (7-6)

从式(7-6)可以看出,载波周期Tc=NTs,Ts为采样周期,也是各个载波之间在时间上的相移。在图7-21中,UΔ1、UΔ2、UΔ3对应于图7-20中的第1、第2、第3单元的3路载波,载波之间移相Ts=Tc/3;Ur(t)、-Ur(t)为图7-20中某一功率单元的左、右桥臂调制波,其调制波相位相差180°。

对于级联型变频器,多载波的形成及载波之间相位的精确锁定是实现前述调制策略的关键,只有这样,才能保证变频器输出获得良好的谐波特性。

(1)多载波的形成

以图7-21所示的3路三角载波为例来说明多载波之间相移的形成,载波移相原理如图7-22所示。

图7-22 三角载波移相原理

为了在FPGA中,得到不同初始相位的载波发生器,达到载波移相的效果,需要由DSP对载波的初值以及计数的初始方向进行设置,然后再使载波发生器完成可逆计数。在图7-22中,对于所需要的3路三角载波来说,若设置载波幅值为K,第1路载波的初始相位为0,初值为0,其计数方向为加计数;则第2路载波在相位上滞后第1路Tc/3,幅值为2K/3,且计数方向为减计数;而第3路载波在相位上滞后第1路2Tc/3,幅值同样为2K/3,但是其计数方向为加计数。依据此原理,同样可以产生更多路载波,只需要由DSP对各个载波计数器的初值及初始计数方向进行设置。

(2)多载波之间相位准确锁定的实现方法

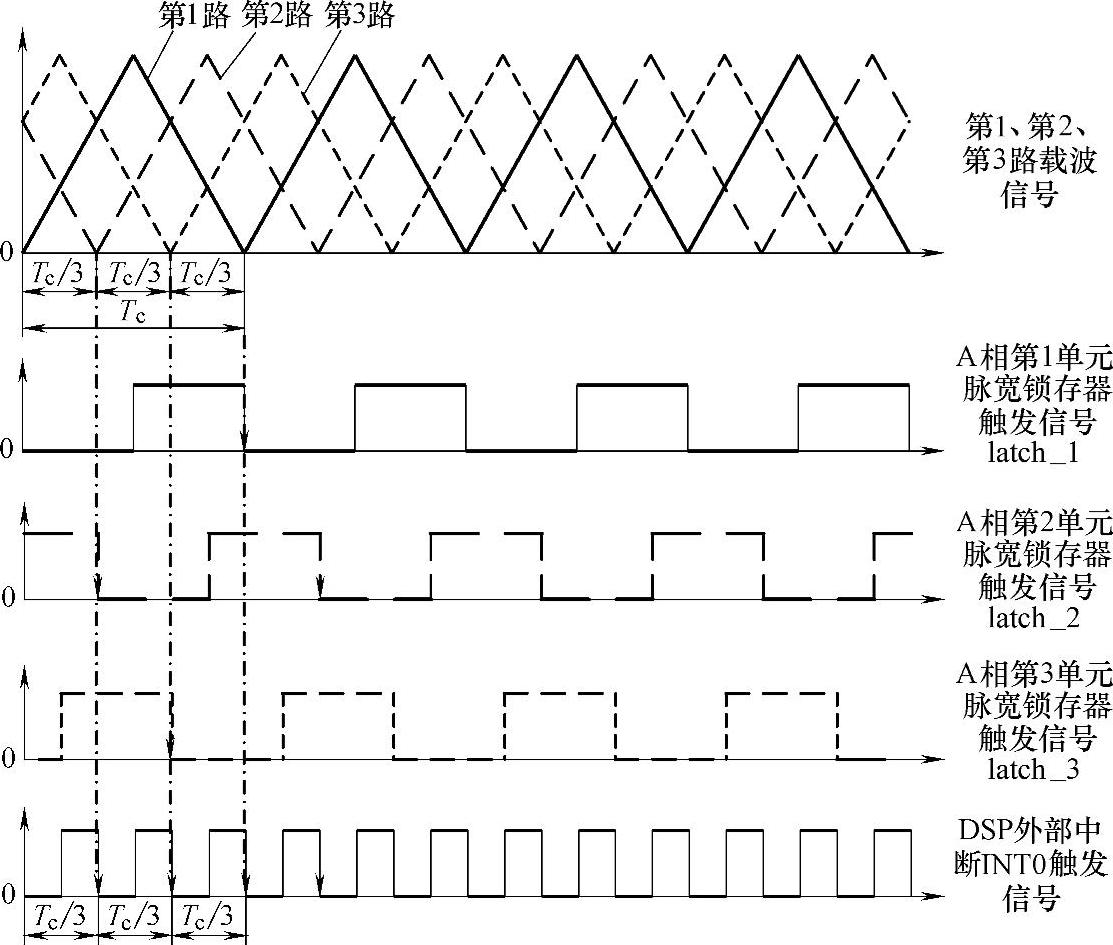

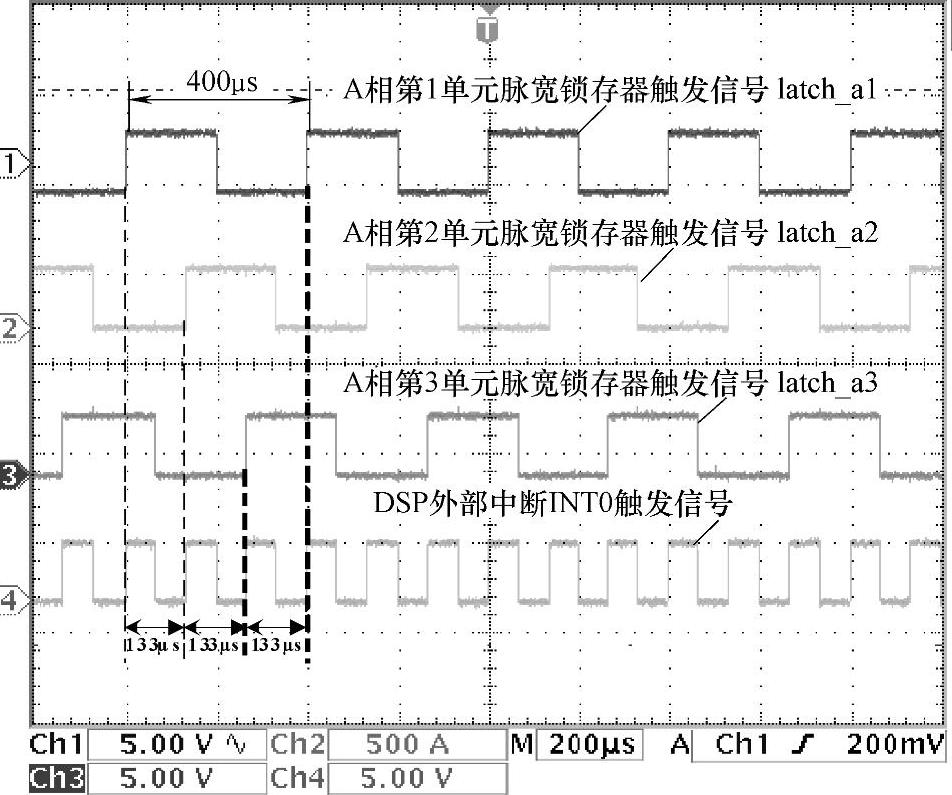

在多载波水平移相调制策略中,载波之间的相位关系是保证该调制策略优良特性的关键,而移相造成驱动脉冲脉宽数据更新时刻的不同。以A相为例,对相位关系准确定位的方法进行说明,如图7-23所示。图7-23中,载波周期是Tc,相邻载波之间移相Tc/3,因此计算脉宽值的中断频率将是载波频率的三倍,即中断时间为Tc/3。

对于3路载波可逆计数器,首先要形成反映每路可逆计数器方向的正反向计数信号。该信号实际是载波计数器的加减计数信号,是周期为Tc的方波,也是各个脉宽锁存器的触发信号。在图7-23中,A相3个单元脉宽锁存器触发信号分别为latch_1、latch_2、latch_3。脉宽计算中断的触发信号可以通过latch_1、latch_2、latch_3得到,其逻辑关系式表示为(latch_1 or latch_2)and(latch_2 or latch_3)and(latch_3 or latch_1),送入DSP外部中断INT0,来决定脉宽数据更新的时刻。

(3)多路驱动脉冲的具体实现方式

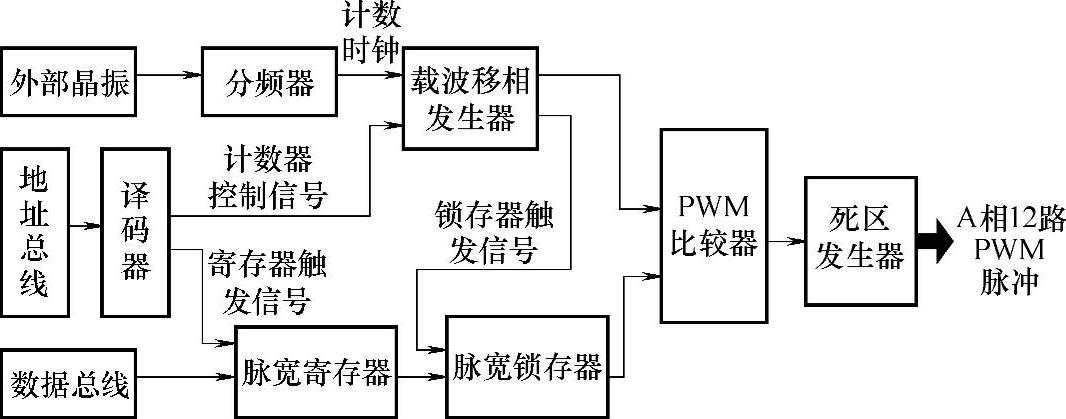

以3单元串联三相逆变器为例,构造了36路PWM发生器。所构造的36路PWM发生器是由3个单相12路PWM发生器构成的。以A相为例,12路PWM发生器结构如图7-24所示。

1)译码器:主要功能就是对DSP所提供的地址总线、控制信号进行译码,来形成各个脉宽寄存器、死区寄存器和计数峰值寄存器等的触发信号,以实现不同数据的正确分配。

图7-23 脉宽锁存器及脉宽计算中断触发信号的逻辑综合图

图7-24 A相12路PWM发生器结构

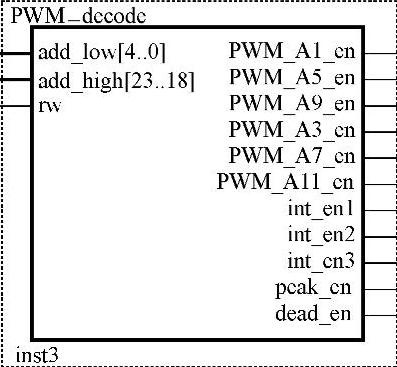

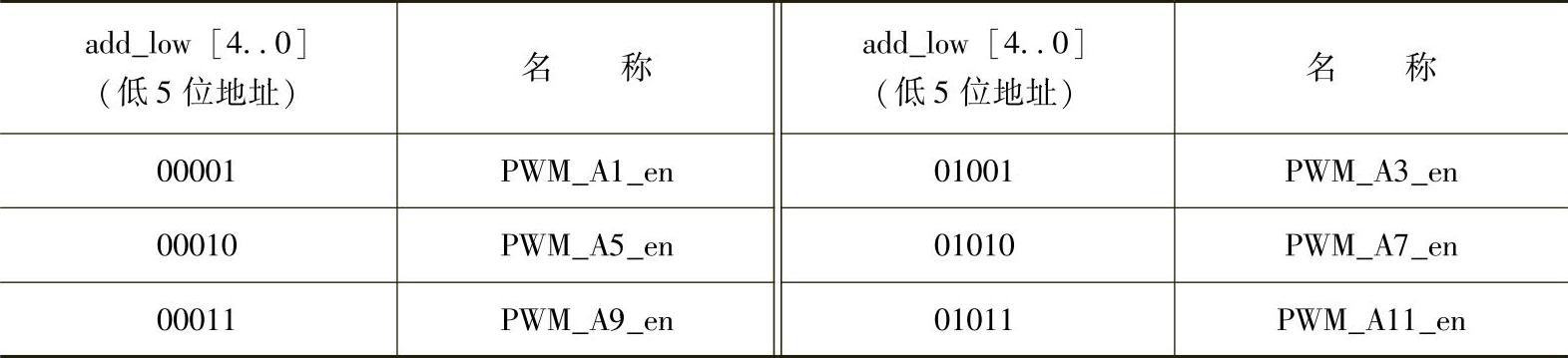

图7-25为在QuartusII中实现的译码器。A相脉宽寄存器地址译码及对应内容见表7-1,其中高6位地址add_high[23..18]=“101000”。

(https://www.xing528.com)

(https://www.xing528.com)

图7-25 译码器

图7-26 载波移相发生器

表7-1 A相脉宽寄存器地址译码及对应内容

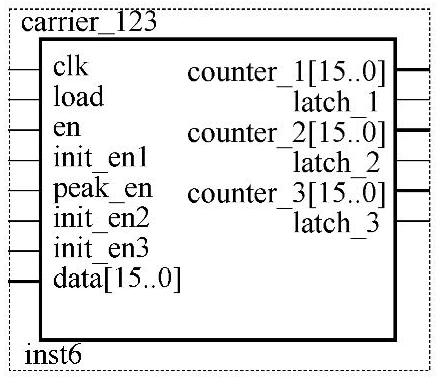

图7-26中,load是载波初值装载信号;en是载波计数使能信号;init_en1、init_en2、init_en3分别是载波移相发生器的第1、第2、第3路载波的初值寄存器触发信号;peak_en是载波计数峰值寄存器的触发信号。

2)载波移相发生器:用来产生模拟电路中的三角载波信号,是一个最小计数值为0,最大计数值为DSP设定值,计数方向交替变化的可逆计数器。

图7-26为在QuartusII中实现的载波移相发生器。输入信号和前面说明的译码器的输出信号完全一致。counter_1[15..0]、counter_2[15..0]、counter_3[15..0]分别对应于第1、第2、第3路载波计数信号;latch_1、latch_2、latch_3分别对应于A相第1、第2、第3单元脉宽锁存器触发信号。

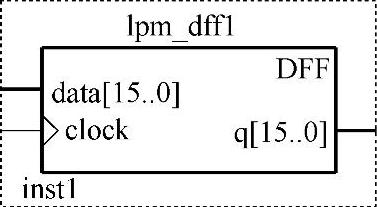

3)脉宽寄存器:作为影子寄存器,在控制周期的任何时刻,DSP都可以对脉宽寄存器进行更新。

图7-27中,脉宽寄存器采用QuartusII中的可参数化模块,输入信号中包含数据输入data[15..0],与DSP的数据总线相连;时钟信号clock与脉宽寄存器触发信号相连。输出信号是数据输出q[15..0]。在脉宽寄存器触发信号的上升沿把更新后的数据data[15..0]赋值给q[15..0]。

图7-27 脉宽寄存器

图7-28 脉宽锁存器

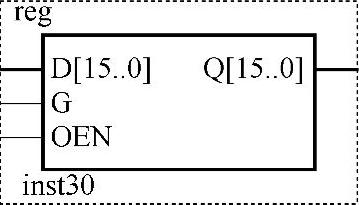

4)脉宽锁存器:在锁存器触发信号发生时,把脉宽寄存器更新后的脉宽值放在脉宽锁存器中。在图7-28中,输入信号有数据输入D[15..0];锁存器触发信号G;赋值使能OEN,其值为1时,允许将D[15..0]赋值给Q[15..0],否则清零Q[15..0]。输出信号是数据输出Q[15..0]。

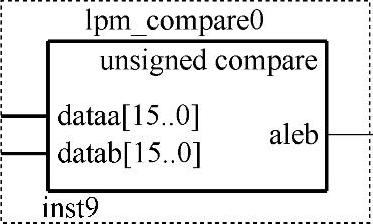

5)PWM比较器:根据图7-23,在锁存器触发信号发生时,对应的载波计数器从0开始进行可逆计数。在一个载波周期内,载波计数器值与脉宽值有两次比较匹配,分别发生在加计数与减计数期间,经PWM比较器后输出驱动脉冲。

由QuartusII自带的参数化比较器LPM_COMPARE模块来实现,如图7-29所示。LPM_COMPARE的两个输入dataa[15..0]和datab[15..0]分别接脉宽锁存寄存器和载波移相发生器,从而完成等幅不等宽的PWM脉冲信号的生成。

图7-29 PWM比较器

图7-30 分频器

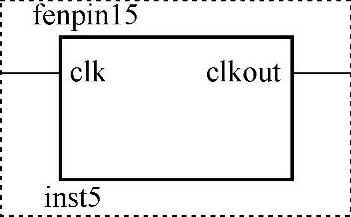

6)分频器:分频器的输入是控制板上晶体振荡器产生的系统时钟,其功能是将系统时钟分频,产生不同频率的时钟脉冲,给载波提供时钟用以计数。在程序里,对分频器设置不同的值,就可以实现不同的时钟分频,得到符合要求的载波频率。

在图7-30中,输入信号是时钟clk,输出信号是clkout。

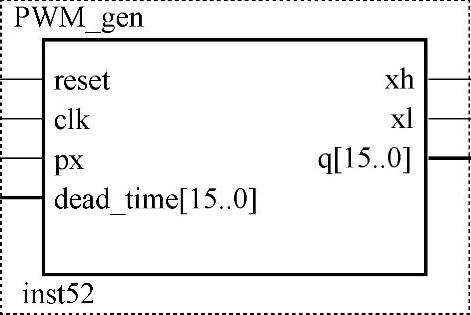

7)死区发生器:为了防止上下桥臂直通,功率器件之间要加入死区,死区发生器如图7-31所示。

在图7-31中,输入信号中包含时钟clk;没有加入死区值的PWM信号px,复位控制信号reset;死区值信号dead_time[15..0]。输出信号是加入死区值后的PWM信号xh和xl。

图7-31 死区发生器

(4)实验结果

基于DSP和FPGA相结合的数字化实验系统平台,依据二重化与多载波水平移相相结合的调制策略,对多路驱动脉冲的产生进行了实验研究。FPGA芯片选用CycloneIII系列的EP3C25Q240C8N,用来产生PWM驱动脉冲,编程软件采用QuartusII。DSP选用

图7-32 DSP与FPGA之间的连接框图

TMS320F2812,用来完成对FPGA中的各种寄存器进行配置和脉宽值的计算。在实验中,FPGA芯片的外部晶体振荡频率为15MHz,调制波频率为50Hz,载波频率fc为2.5kHz(载波周期为400μs),采样频率为7.5kHz,死区时间4μs。图7-32为DSP与FPGA之间的连接框图。

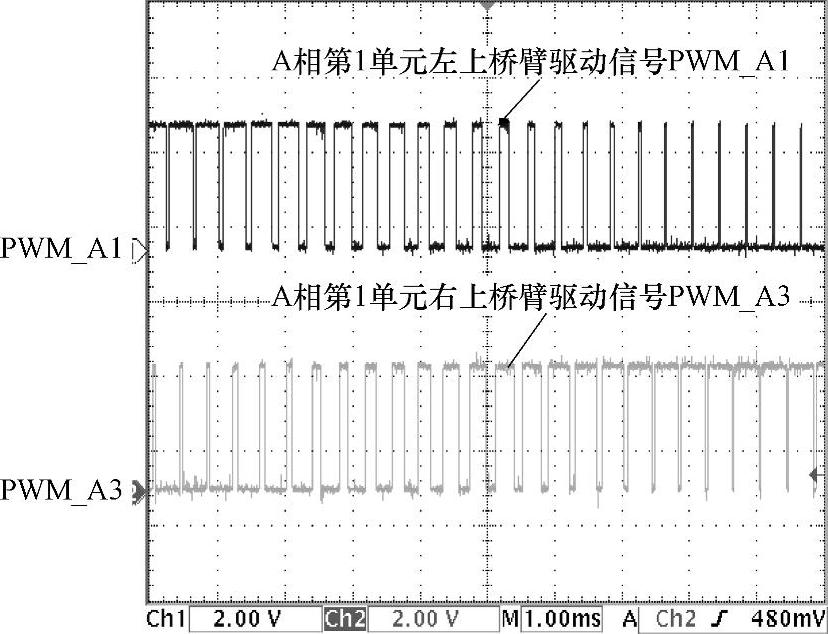

图7-33为采用二重化调制方法后,A相第1单元的驱动波形PWM_A1、PWM_A3。

图7-33 A相第1单元的驱动波形PWM_A1、PWM_A3

图7-34为与图7-23对应的脉宽锁存器触发信号。在图7-34中,3倍频信号周期为133μs,正好是载波周期的1/3。实验结果与图7-23中分析的各单元脉宽锁存器的触发信号,以及DSP外部中断触发信号完全一致,证明了多载波相位锁定方法的正确性。

图7-34 与图7-23对应的脉宽锁存器触发信号

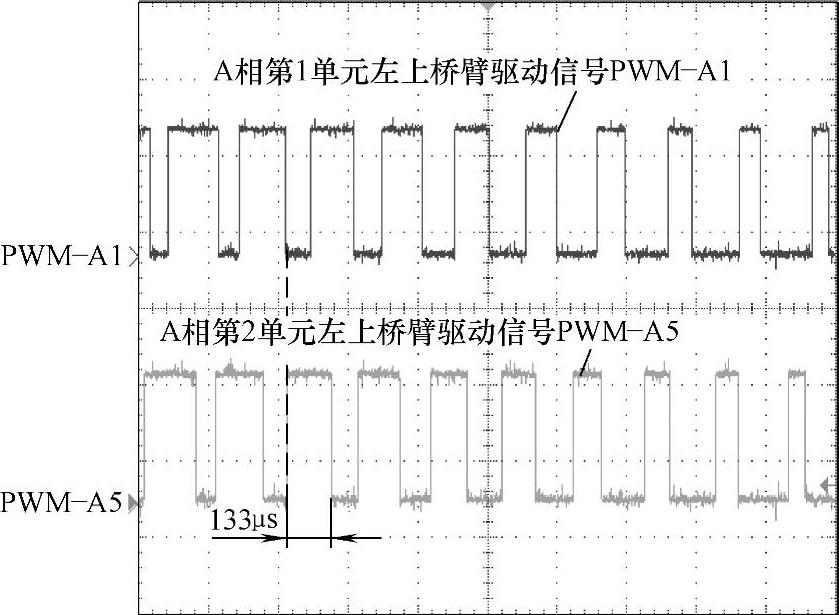

图7-35为A相第1、第2单元左上桥臂PWM_A1、PWM_A5的驱动信号。从图7-35中触发发脉冲的相移可以看出,它们之间的相移为三分之一载波周期,即133μs,与前述的多载波移相原理一致,同时也证明了基于FPGA的多路PWM脉冲发生方式及具体实现的可行性。

图7-35 A相第1、第2单元左上桥臂PWM_A1、PWM_A5的驱动信号

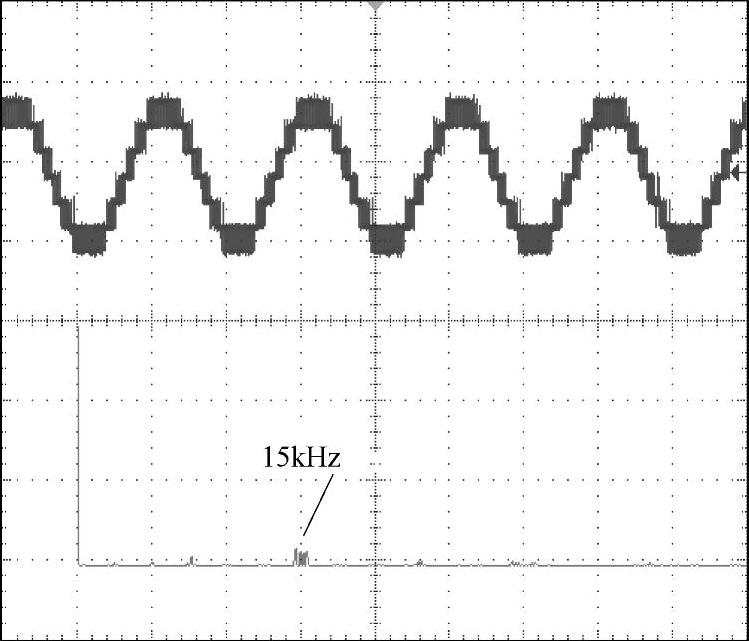

图7-36分别为三单元级联逆变器实验系统的7电平阶梯波及其频谱分析。图7-36中的频谱分析结果表明:输出7电平的谐波主要位于2Nfc=15kHz及其边带谐波,与理论分析一致。

图7-36 实验输出的7电平阶梯波及其频谱分析

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。