【实验目的】

(1)了解施密特触发器、单稳态触发器、多谐振荡电路的构成和工作原理。

(2)了解脉冲信号产生电路的实际应用。

(3)掌握555定时器原理和典型应用。

(4)练习脉冲信号产生电路实际调测方法。

【设计任务】

(1)用二输入与非门分别构成微分型和积分型单稳态触发电路。

给定条件:

◆+5 V供电;

◆CD4011,阻容元件自选。

指标要求:

◆定时时间分别为20μs、20 ms、2 s。

(2)用555定时器构成一个延时照明控制电路。

给定条件:

◆+5 V供电;

◆555定时器×1、发光二极管×1,按键×1,阻容元件自选。

功能要求:

◆按动一次按键,发光管持续点亮5秒后自动熄灭。

(3)用适当的逻辑门构成环形振荡电路。

给定条件:

◆+5 V供电;

◆逻辑门和阻容元件自选。

指标要求:

◆振荡周期100μs±5%范围。

(4)用555定时器构成一个多谐振荡电路,驱动扬声器发出中音“LA”的音调。

给定条件:

◆+5 V供电;

◆555定时器×1、0.5 W扬声器×1,晶体管和阻容元件自选。

指标要求:

◆频率误差不超过±0.5%。

(5)将任务(2)电路和任务(4)电路结合,实现按键控制扬声器发出中音“LA”的音调,每按一次按键,扬声器发出中音“LA”的音调,5秒后自动停止。

【测试任务】

(1)微分型和积分型单稳态触发电路的调测

①根据电路特点选择适当的输入信号。

②同时观测输入输出波形并记录。

③从输出波形读出输出高、低电平值,定时宽度值,并与计算值相比较。

④将微分型和积分型两种单稳态触发电路进行比较,总结它们各自的特点和应用场合。

(2)延时照明控制电路的调测

①按照设计图分别规范连接各类电路。

②不接发光二极管,直接用示波器捕捉振荡输出脉冲并读出其高、低电平值以及周期。

③接入发光二极管,观察二极管点亮的情况,测量相关参数,计算发光二极管导通时的功率。

(3)环形振荡电路的调测

①根据电路图规范连接电路。

②同时观测振荡输出波形并记录。

③从示波器读出输出波形的高、低电平、周期和频率值,并与设计值相比较。如果周期与要求值不符,那么调节电路元件使之符合要求。

④如果输出波形不理想,输出加一级反相门后,观察波形的改善情况。

(4)555定时器构成的多谐振荡电路的调测

①扬声器暂不接入,观测电路的振荡输出波形并记录。

②从输出波形读出输出高、低电平值以及周期和频率,如果频率与中音“LA”相差较大,调节电路使频率符合要求。

③将扬声器规范接入电路,试听扬声器的发声情况,并测相关参数估算扬声器发声时的功率。

④如果声音不够响亮,接入三极管以提高输出电流,对比声音的变化情况。再一次估算扬声器的功率。

⑤调整电路振荡频率,观察声音音调的变化情况。

(5)实际测试验证任务(2)电路和任务(4)电路结合后的功能

【实验预习】

(1)查阅相关资料,了解并整理TTL集成电路和CMOS集成电路使用注意事项。

(2)查阅相关集成电路的器件资料和数据手册,了解这些器件的相关特性和使用注意事项。

(3)阅读本实验【相关知识】,掌握相关电路的分析、设计和调测方法,设计相关电路,列出详细设计过程并画出完整详细的电路图。并对电路进行仿真和分析。

(4)针对测试任务拟订详细的调测操作步骤,设计相关数据表格,列出实验注意事项。

(5)在面包板上搭建实验电路。

(6)预习思考题:

①TTL集成电路在使用时,不用的输入端如何处理?其输入端悬空意味着什么?

②CMOS集成电路在使用时,不用的输入端如何处理?假如只使用CD4011中的三个门,剩余一个不用的门的输入端需要处理吗?为什么?

③用TTL电路的输出驱动CMOS电路有哪些注意事项?反之如何?

④图8.9.8(a)门电路构成的环行振荡器电路中,电阻RS起什么作用?如何取值?

【报告撰写】

实验之前

◆参考本书附录“实验报告格式”,结合实验预习过程完成报告1~5项。

实验之后

◆结合实验过程继续完成报告6~9项。

【相关知识】

1.单稳态电路

单稳态电路又称单稳态触发器,有稳态和暂稳态两种工作状态。在外接触发信号的作用下,单稳态电路从稳态转换到暂稳态,暂稳态持续一段时间后,自动回到稳态,暂稳态持续的时间取决于电路中的阻容元件。

单稳态触发器可由二极管、晶体管等分立元件或运算放大器构成,也可以由逻辑门电路构成,也有集成的单稳态触发器芯片。单稳态触发器广泛应用于定时、延时和波形的整形等方面。

门电路加上适当的RC元件,可以构成各种形式的单稳态触发器。

(1)微分型单稳态触发器

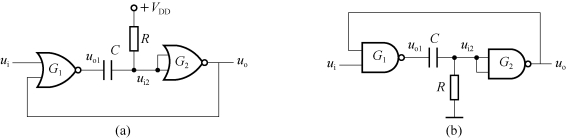

单稳态触发器可分别由与非门和或非门电路组成,逻辑门之间由RC微分电路的形式耦合,故称为微分型单稳态触发器。图8.9.1(a)(b)分别为由或非门和与非门构成的微分型单稳态触发器。

图8.9.1 两种微分型单稳态触发电路

下面以图8.9.1(a)所示或非门构成的单稳态触发电路为例,分析其工作波形,说明其工作原理。

图8.9.2给出或非门构成的单稳态触发电路工作波形示意。

t<t1时,ui为低电平,由于门G2的输入端经电阻R接VDD,因此ui2为高电平,uo为低电平,G1的两个输入均为低电平,故输出uo1为高电平。电容C两端的电压接近0V,电路处于“稳态”。稳态时电路输出uo=UoL。

图8.9.2 或非门构成的微分单稳态电路工作波形

t=t1时,ui出现由低到高的跳变,当其电压上升达到门电路的阈值电压Uth后,G1的输出uo1由高变低,经电容C耦合使ui2为低电平,G2的输出uo由低变高。同时uo的高电平接至G1门的输入端。从而在此瞬间存在如下正反馈过程:

![]()

t=t2时,触发信号ui变为低电平,但由于uo为高的作用,uo1仍维持为低电平。然而,由于VDD通过电阻R对电容C充电,使ui2从低到高持续增加,可以预见uo=UoH的状态不能长久保持,故称之为暂稳态。(https://www.xing528.com)

暂稳态时,VDD通过电阻R对电容C充电,使ui2从低到高增加。

t=t3时,ui2增加到门电路的阈值电压Uth,G2的输出uo由高电平变为低电平,电路由暂稳态返回至稳态。

从上述过程可以看出,电路输出的正脉冲宽度tw即暂稳态持续时间,是由RC充电速度决定的。充电过程的起始电压近似为G1输出的低电平UoL≈0 V,终止电压为门电路的阈值电压![]() ,经过推算近似有:

,经过推算近似有:

tw=RC ln 2=0.69RC

但各种单稳态电路由于参数的分散性,一般tw在0.69RC~1.3RC的范围内。所以具体电路的实际定时脉宽,需要经过实际调测。一般通过更换不同容值的电容器粗调,使用电位器改变R细调。

需要说明一点:在上述分析中,t=t3时刻G2的输出uo由高到低跳变时,当uo等于G1的阈值电压Uth时,G1的输出产生由低到高的跳变,使门G2的输入电压ui2瞬间高达VDD+Uth,可能导致G2的损坏。为了避免这种现象发生,在CMOS器件内部输入端到VDD端设有保护二极管VD,在输入端电压高于VDD+UD后二极管VD导通,使门的输入端电压钳位于VDD+UD,保护了门电路。

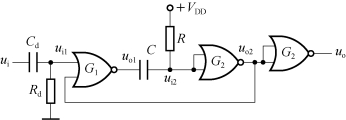

图8.9.1(a)所示的单稳态电路,如果输入信号ui的脉冲宽度大于输出信号uo的宽度tw时,则在uo变为低电平后,G1没有响应,uo1保持为低电平,所以uo的输出边沿变缓。因此,当输入脉冲宽度较宽时,可在单稳态触发器的输入端加入Rd、Cd组成的微分电路。为了进一步改善输出波形,可在图8.9.1中G2的输出端再加一级反相器G3,具体如图8.9.3所示。

图8.9.3 改进的微分型单稳态电路

(2)积分型单稳态触发器

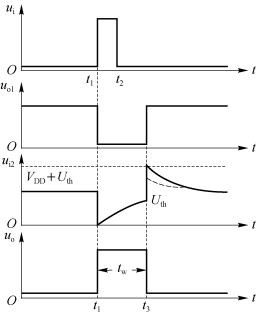

积分型单稳态触发器也可分别由与非门和或非门电路组成,逻辑门之间由RC积分电路的形式耦合。图8.9.4(a)(b)分别为由或非门和与非门构成的积分型单稳态触发器。

图8.9.4 两种积分型单稳态触发电路

以图8.9.4(b)与非门构成的单稳态电路为例,简单说明其工作原理。图8.9.4(b)电路的工作波形如图8.9.5所示。

图8.9.5 与非门构成的积分型单稳态电路

t<t1时,ui为低电平,G1和G2截止,uo1和uo均为高电平,电路处于“稳态”。稳态时电路输出uo=UoH。

t=t1时,ui由低电平变为高电平,G1的输出uo1随之由高变低,但电容C上的电压不能跳变,所以使ui2仍为高电平,此时G2的两个输入端均为高,因此输出uo由高变为低。但此时电容通过R放电,使ui2从高到低持续减小,可以预见uo=UoL的状态不能长久保持,故称之为暂稳态。

t=t2时,ui2降低到门电路的阈值电压Uth,G2的输出uo由低电平变为高电平,电路由暂稳态返回至稳态。而ui2继续下降。

t=t3时,输入信号ui由高电平变为低电平,G1截止使uo1变为高电平。uo1通过R对电容充电,ui2增大,一段时间后ui2为高电平。但由于ui为低电平,所以uo保持为高电平。

取![]() ,经过推导可得:

,经过推导可得:

![]()

同微分型单稳态电路一样,具体电路的定时脉宽均需通过实验,实际进行调测。

(3)集成单稳态触发器

集成单稳态触发器有不可重复触发型和可重复触发型两种。不可重复触发的单稳态触发器一旦被触发进入暂稳态后,再加入触发脉冲不会影响电路的工作过程,必须在暂稳态结束后,才接受下一个触发脉冲而转入暂稳态。可重复触发的单稳态触发器进入暂稳态后,如果再次加入触发脉冲,电路将重新被触发,使输出脉冲再继续维持一个tw宽度。

常见的低功耗肖特基型集成单稳态触发器有74LS121、74LS122和74LS123等。

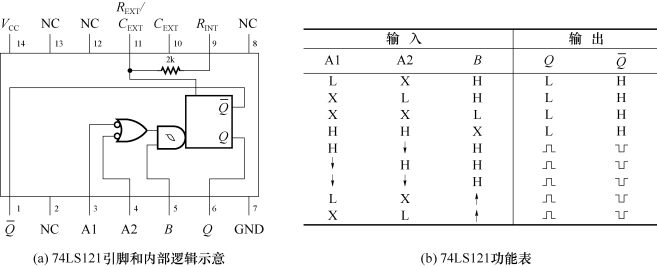

74LS121为具有施密特触发器输入的不可重触发的单稳态触发器,其输出脉冲范围为40 ns~28 s,其外部引脚和内部逻辑示意如图8.9.6(a)所示,图8.9.6(b)为其功能表。

图8.9.6 集成单稳态触发器74LS121

单稳态电路的定时时间取决于定时电阻和定时电容的取值。74LS121的定时电容连接于第10、11管脚之间。如果接电解电容则正极接第10脚。

74LS121的定时电阻有两种选择,第一种是采用芯片内部2 kΩ定时电阻,此时第9管脚接电源VCC。

第二种选择使用外部定时电阻,定时电阻取值范围为1.4~40 kΩ,接在11和14管脚之间,而第9管脚悬空。

输出脉宽也称为定时时间,用tw≈0.7RC计算。通常R在2~30 kΩ范围、C在10 p F~10μF之间取值,定时时间范围为20 ns~200 ms。

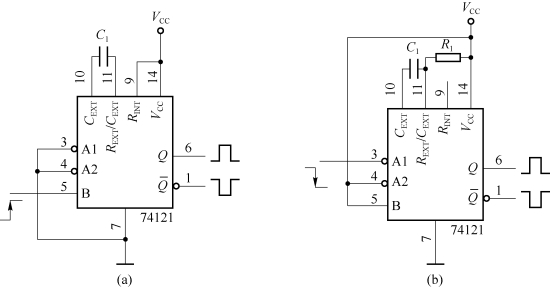

图8.9.7给出了74LS121两种应用电路,其中(a)为上升沿触发,使用了芯片内部定时电阻;(b))为下降沿触发,使用了外部定时电阻。

图8.9.7 74LS121两种应用电路

除74LS121外,74LS122为带清除端的可再触发集成单稳态触发器,而74LS123为双可再触发集成单稳态触发器,后二者的具体使用可参考相关数据手册。

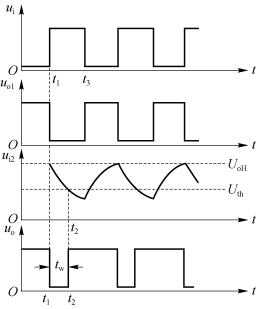

2.门电路构成环行振荡器

环行振荡器是奇数个反相门串接成环形结构,利用门的延迟时间或RC网络的延时,实现两种暂稳态交替变化,输出矩形脉冲信号。

图8.9.8是三个非门构成的环行振荡器电路和工作波形。

图8.9.8 环行振荡器电路和工作波形

t<t1时,vo为低电平,vo1为高电平vo2为低电平,电容自左向右充电,va下降。

t=t1时,va下降至vth,vo反转至高电平,vo1反转至低电平vo2反转至高电平,由于电容C两端的电压不能突变,所以va有向下的跳变,然后电容C开始自右向左反向充电,va上升。

t=t2时,va上升至vth,vo反转至低电平,vo1反转至高电平vo2反转至低电平,同样由于电容C两端的电压不能突变,所以va有向上的跳变,然后电容C上电流反向,开始自左向右充电,va下降,直至降到vth,开始又一次的反转。

如此循环,电路持续输出矩形波。

TTL和CMOS门电路均可用于构成环行振荡器,但在采用TTL门电路时应注意,R和Rs的阻值不宜过大,否则将导致G3的输入端始终处于高电平,电路无法工作。一般Rs取100~200Ω,R取2 kΩ以下。图8.9.8(a)电路的振荡周期可由下式估算:

![]()

环行振荡器由于工作频率较高,会出现输出波形不是理想矩形波的情况,为了改善波形,可以在输出端再加一级反相门。

3.555定时器及应用

(1)555定时器结构特点

555定时器是一种用途广泛的双极型数模混合集成电路。555定时器外加少量阻容元件,即可构成单稳态触发器、施密特触发器、多谐振荡器等电路。

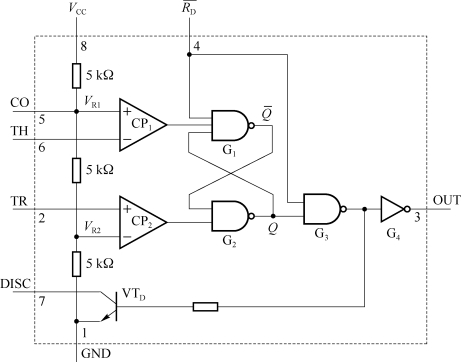

555定时器的外部引脚及内部逻辑结构框图如图8.9.9所示。

图8.9.9 555定时器引脚及内部逻辑结构框图

555定时器内部三个5 kΩ组成分压电路,将![]() 引入运放CP1的同相输入端,将

引入运放CP1的同相输入端,将![]() VCC引入运放CP2的反相输入端,这两个运放分别组成反相和同相的两个电压比较器,其输出接G1和G2构成的RS触发器。触发器输出经G3和G4两次反相后输出。晶体管VTD为外部电路提供放电通道,被称为放电管。

VCC引入运放CP2的反相输入端,这两个运放分别组成反相和同相的两个电压比较器,其输出接G1和G2构成的RS触发器。触发器输出经G3和G4两次反相后输出。晶体管VTD为外部电路提供放电通道,被称为放电管。

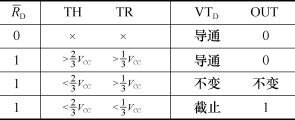

图8.9.10 555定时器功能表

555定时器功能表如图8.9.10所示。,接低电平时无论RS触发器输出如何,OUT输出恒为低电平。第5端为控制端CO,接电压源时,则两个电压比较器的比较电压由CO所接电压控制,与VCC无关。

555定时器产品既有TTL也有CMOS的,其中TTL产品以555命名,而CMOS产品以7555命名,在使用时应注意区分。

(2)555定时器构成单稳态触发器

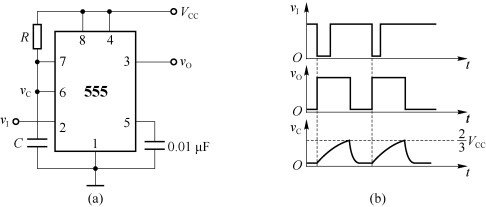

图8.9.11(a)(b)分别为555定时器构成的单稳态触发器电路及工作波形。

555的第4端为复位端![]()

图8.9.11 555构成单稳态触发器及其工作波形

图8.9.11与图8.9.9相结合进行分析,输入信号vi接入了555内部运放CP2的同相输入端。当vi下降沿到达,电压低于![]() 时,CP2输出低电平,G2输出Q为高电平,vo输出高电平,电路进入暂稳态。此时晶体管VTD截止,VCC经R向C充电,vC升高。

时,CP2输出低电平,G2输出Q为高电平,vo输出高电平,电路进入暂稳态。此时晶体管VTD截止,VCC经R向C充电,vC升高。

当vc未充电至![]() 的过程中,vi由低电平变为高电平,CP2输出高电平。但由于

的过程中,vi由低电平变为高电平,CP2输出高电平。但由于 为低,所以vo输出仍为高电平。

为低,所以vo输出仍为高电平。

当vC升高至![]() 时,CP1输出低电平G1输出

时,CP1输出低电平G1输出 由低变高,vo输出由高变低进入稳态,触发器翻转。晶体管VTD饱和导通,电容C经VTD迅速放电。

由低变高,vo输出由高变低进入稳态,触发器翻转。晶体管VTD饱和导通,电容C经VTD迅速放电。

vi下一个下降沿到达,重复上述过程。

该单稳态触发器的定时时间,即vO的脉冲宽度tw由下式近似计算:

![]()

从上述分析可以看出,该电路输入信号vi的低电平宽度必须小于定时时间,电路才能正常工作。如果vi不能满足这一要求,可以通过在输入端接一个微分电路,将过宽的触发脉冲变窄。

(3)555定时器构成多谐振荡器

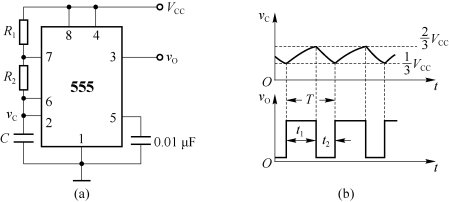

图8.9.12(a)(b)分别为555定时器构成的多谐振荡器电路及工作波形。

图8.9.12 555构成单多谐振荡器及其工作波形

结合图8.9.9中555的内部电路进行分析,电路初上电时,vC电压低于![]() ,CP1输出高电平CP2输出低电平,G2输出Q高电平,vo输出高电平。晶体管VTD截止,VCC经R1和R2向C充电,vC升高。

,CP1输出高电平CP2输出低电平,G2输出Q高电平,vo输出高电平。晶体管VTD截止,VCC经R1和R2向C充电,vC升高。

vC升高过程中,当![]() 时,两个运放输出均为高电平,RS触发器保持,vo输出仍为高电平。晶体管VTD截止,vC继续升高。当vC升高至

时,两个运放输出均为高电平,RS触发器保持,vo输出仍为高电平。晶体管VTD截止,vC继续升高。当vC升高至![]() 时,运放CP1输出由高变低,RS触发器反转,vo输出由高变低。晶体管VTD饱和导通,电容通过R2向VTD放电,vC下降。

时,运放CP1输出由高变低,RS触发器反转,vo输出由高变低。晶体管VTD饱和导通,电容通过R2向VTD放电,vC下降。

vC下降过程中处于![]() 范围时,两个运放输出均为高电平,RS触发器保持,vo输出仍为低电平。晶体管VTD截止,vC继续下降。

范围时,两个运放输出均为高电平,RS触发器保持,vo输出仍为低电平。晶体管VTD截止,vC继续下降。

vC下降至![]() 时,CP2输出低电平,电路又一次反转,重复以上过程。

时,CP2输出低电平,电路又一次反转,重复以上过程。

从以上过程分析可以看出,输出vo的高电平持续时间t1为VCC经R1和R2向C充电,vC从![]() 到

到![]() 的过程,所以有:

的过程,所以有:

![]()

vo的低电平持续时间t2为电容经R2向晶体管放电,vC从![]() 到

到![]() 的过程,所以有:

的过程,所以有:

![]()

所以555构成的多谐振荡器的振荡周期T和频率f分别为:

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。