逐次比较型A/D转换电路是ADC0809内部的核心电路,主要由D触发器、数据寄存器和移位寄存器构成,功能是对预设的数字量进行逐次比较和结果处理。

1.电路结构

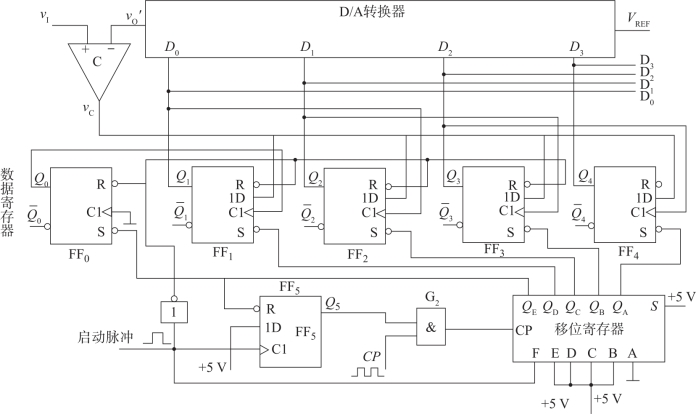

4位逐次比较型A/D转换电路如图7-28所示。由图可见,逐次比较型A/D转换电路由1个5位的移位寄存器、5个D触发器构成的数据寄存器、D/A转换器、电压比较器和启停控制D触发器、逻辑门等逻辑控制电路构成。

微课 逐次比较型A/D转换电路

图7-28 A/D转换内部电路

其中,各D触发器的R端为低电平有效的复位端,S端为低电平有效的置位端;移位寄存器的A、B、C、D、E为并行输入端,F为高电平有效的并行输入使能控制端,当F=1时,移位寄存器的输出QEQDQCQBQA=EDCBA。S为左移位串行输入端,在时钟脉冲信号CP的控制下,依次进行左移一位操作。

2.电路原理

(1)启动脉冲作用下,电路的工作状态。

①反相器使D触发器FF0~FF3的低电平有效,清0端R得到低电平有效信号,清0。

②移位寄存器的F端得到高电平信号,实现并行输入,QEQDQCQBQA=11110。

③D触发器FF4的置位端S得到低电平有效信号,置1。

④D3D2D1D0=1000,送入D/A转换电路,转换结果送电压比较器反相输入端。(https://www.xing528.com)

⑤D触发器FF5的输出端Q5接收输入端D的数据,Q5=1,与门G2开启,CP脉冲进入移位寄存器。

(2)1CP上升沿后,电路的状态。

①移位寄存器输入串行端S的数据,QEQDQCQBQA=11101,FF3的置位端得到低电平有效信号,D2=Q3=1。

②因Q3=0→1,触发器FF4时钟信号出现上升沿,FF4接收第一位数字量转换后的电压比较器输出结果,如v′O<vI,Q4=1;如v′O>vI,Q4=0。

(3)2CP上升沿后,电路的状态。

①移位寄存器继续左移,QEQDQCQBQA=11011,FF2的置位端得到低电平有效信号,D1=Q2=1。

②因Q2=0→1,触发器FF3时钟信号出现上升沿,FF3接收第二位数字量转换后的电压比较器输出结果,如v′O<vI,Q3=1;如v′O>vI,Q3=0。

(4)3CP上升沿后,电路的状态。

①移位寄存器继续左移,QEQDQCQBQA=10111,FF1的置位端得到低电平有效信号,D0=Q1=1。

②因Q1=0→1,触发器FF2时钟信号出现上升沿,FF2接收第三位数字量转换后的电压比较器输出结果,如v′O<vI,Q2=1;如v′O>vI,Q2=0。

(5)4CP上升沿后,电路的状态:

①移位寄存器继续左移,QEQDQCQBQA=01111,FF0的置位端得到低电平有效信号,Q0=1。

②因Q0=0→1,触发器FF1时钟信号出现上升沿,FF1接收最后一位数字量转换后的电压比较器输出结果,如v′O<vI,Q1=1;如v′O>vI,Q1=0。

③因QE=0,触发器FF5的低电平有效复位端信号有效,Q5=0,与门G2截止,时钟脉冲信号CP被阻断,转换结束。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。