微课 寄存器认知

寄存器是数字逻辑电路中应用非常广泛的时序逻辑器件。ADC0809内部的核心电路就是逐次逼近寄存器。根据功能,寄存器分为数据寄存器和移位寄存器两大类。

7.4.1 数据寄存器

数据寄存器的功能是在接收脉冲的作用下,并行输入输出数据。由D触发器构成的4位数据寄存器电路如图7-20所示。

图7-20 4位数据寄存器

由图可见,4个D触发器共用时钟脉冲,但彼此相互独立。当输入端D3D2D1D0置入一个4位二进制数时,在接收脉冲CP的上升沿,4个D触发器同时接收各自D输入端的数据,即Q3Q2Q1Q0=D3D2D1D0。

7.4.2 移位寄存器

移位寄存器的功能是在时钟脉冲的控制下,逐位串行输入、并行/串行输出数据。根据移位方式,移位寄存器可分为左移位寄存器、右移位寄存器、双向移位寄存器。

(1)左移位寄存器。

左移位寄存器的电路如图7-21所示。

图7-21 左移位寄存器电路

图中![]() 为低电平有效清0端。CP为移位脉冲,D0为串行数据输入端,Q2、Q1、Q0为并行数据输出端,Q3为串行数据输出端。

为低电平有效清0端。CP为移位脉冲,D0为串行数据输入端,Q2、Q1、Q0为并行数据输出端,Q3为串行数据输出端。

由图7-21可见,移位寄存器中前一级触发器的输出作为后一级触发器的输入,从D0输入的数据,在第一个时钟脉冲信号的上升沿后,送入Q0,即Q0=D。因Q0与触发器FF1的输入端D连接,在第二个时钟脉冲上升沿后,Q1=Q0,即D0的数据送入Q1。如此,每个时钟信号的上升沿,从串行输入端输入的数据向左移一位,经过4个时钟脉冲后,第一个时钟脉冲信号上升沿前的串行输入数据从串行输出端Q3输出,第一至第四个时钟脉冲信号上升沿前D0的数据从并行输出端Q3Q2Q1Q0输出。

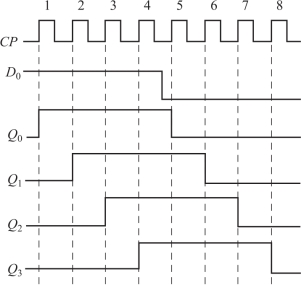

左移位寄存器的时序图如图7-22所示。

(https://www.xing528.com)

(https://www.xing528.com)

图7-22 左移位寄存器时序图

(2)右移位寄存器。

右移位寄存器的电路如图7-23所示。

图7-23 右移位寄存器电路

由图7-23可见,右移位寄存器与左移位寄存器相比,只是移位方向不同,数据传送过程及时序完全一样。右移位寄存器的时序图如图7-24所示。

(3)集成双向移位寄存器74LS194。

74LS194是一款比较典型的中规模集成双向移位寄存器。其引脚图和功能表分别如图7-25和表7-7所示。

图7-24 右移移位寄存器时序图

图7-25 74LS194引脚排列

表7-7 74LS194功能表

由功能表可知:

![]() 是寄存器的清0端,当

是寄存器的清0端,当![]() 时,不论其他信号是什么值,寄存器直接清0;

时,不论其他信号是什么值,寄存器直接清0;

DSL、DSR分别是寄存器的左移位和右移位串行输入端,S0和S1是寄存器工作方式选择的使能控制端。在![]() 为无效信号时,若S0=S1=1时,寄存器在CP脉冲的作用下执行并行输入功能;若S0=0、S1=1时,寄存器在CP脉冲的作用下执行左移位功能,数据从DSL端输入并依次向左移位;若S0=1、S1=0时,寄存器在CP脉冲的作用下执行右移位功能,数据从DSR端输入并依次向右移位;若S0=S1=0时或CP=0时,寄存器保持原来的数据不变。

为无效信号时,若S0=S1=1时,寄存器在CP脉冲的作用下执行并行输入功能;若S0=0、S1=1时,寄存器在CP脉冲的作用下执行左移位功能,数据从DSL端输入并依次向左移位;若S0=1、S1=0时,寄存器在CP脉冲的作用下执行右移位功能,数据从DSR端输入并依次向右移位;若S0=S1=0时或CP=0时,寄存器保持原来的数据不变。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。