地址译码和锁存电路位于ADC0809的输入通道,主要作用是根据锁存地址从8路模拟信号通道中选通一路模拟量输入。其中,锁存器是将ADC0809的输入通道选择端的地址信号锁存,译码器是将通道地址信号转换成通道选择信号。

7.2.1 ADC0809地址译码原理

1.译码器概述

译码器是将具有特定含义的二进制或其他编码转换成对应的信号输出的组合逻辑器件。常见的种类有二进制译码器、二—十进制译码器。二进制译码器的输入如果是n位,则输出为2n个。

2.典型译码器74HC138

(1)引脚结构。

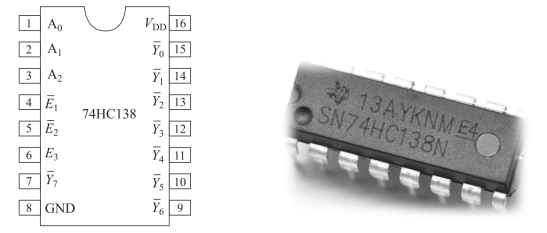

74HC138芯片的引脚结构和实物如图7-3所示。其封装形式为DIP16,有双列直插16个引脚。

微课 ADC0809的地址译码与锁存原理

图7-3 74HC138芯片引脚和实物

(2)引脚功能。

74HC138芯片的引脚功能如表7-1所示。

表7-1 74HC138功能表

引脚1、引脚2、引脚3:输入引脚。

引脚4、引脚5、引脚6:控制引脚,也称使能引脚。其中4、5引脚低电平有效,6引脚高电平有效。

引脚7、引脚9~15:低电平输出引脚![]()

引脚16:电源。

引脚8:接地端。

由表7-1可见,只有当3个使能控制信号同时有效时,对应3位输入编码的任意一种输入组合,有且只有一路输出信号为低电平,输出有效信号的下标即为输入编码对应的二进制数。

(3)内部电路。

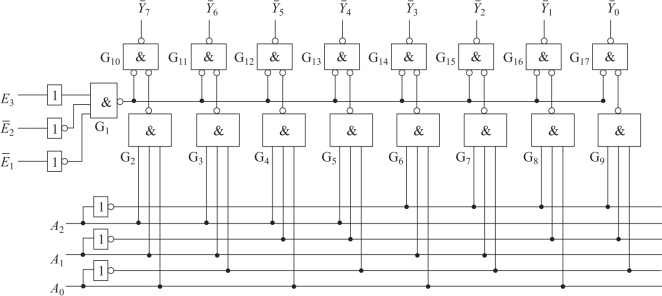

74HC 138内部电路结构如图7-4所示。由图可见,只要使能信号不全有效,如E3=0或![]() 至少有一个为1,与非门G1的输出都为高电平,经非运算后送入到与非门G10~G17的输入端的信号为低电平,使得不论输入端A2、A1、A0输入的编码是什么,G10~G17的输出均为高电平,称高阻状态[1];只有当使能信号全部有效,即

至少有一个为1,与非门G1的输出都为高电平,经非运算后送入到与非门G10~G17的输入端的信号为低电平,使得不论输入端A2、A1、A0输入的编码是什么,G10~G17的输出均为高电平,称高阻状态[1];只有当使能信号全部有效,即![]() 时,与非门G1的输出才为低电平,经非运算后送入到与非门G10~G17的输入端的信号为高电平,这时与非门G10~G17才根据A2、A1、A0输入的编码,每次有一个输出低电平,如表7-1所示。

时,与非门G1的输出才为低电平,经非运算后送入到与非门G10~G17的输入端的信号为高电平,这时与非门G10~G17才根据A2、A1、A0输入的编码,每次有一个输出低电平,如表7-1所示。

图7-4 74HC138芯片内部电路

7.2.2 ADC0809地址锁存原理

1.D锁存器

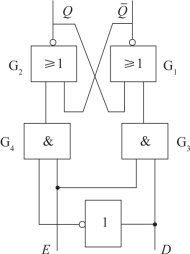

D锁存器是数字逻辑电路中常用的时序逻辑器件之一,其逻辑符号和内部电路如图7-5、图7-6所示。由图7-6可见,D锁存器实际是由一个高电平有效的基_本SR锁存器和一个控制逻辑电路构成。只有当E为高电平时,与门G3和G4才能使D和D 输出。当E=1,D=0时,与门G3输出为0,G4输出为1,锁存器![]() ;当E=1,D=1时,与门G3输出为1,G4输出为0,锁存器

;当E=1,D=1时,与门G3输出为1,G4输出为0,锁存器![]() 。而当E=0时,与门G4和G3输出均为0,SR锁存器保持原来的状态。

。而当E=0时,与门G4和G3输出均为0,SR锁存器保持原来的状态。

图7-5 D锁存器逻辑符号

图7-6 D锁存器逻辑电路

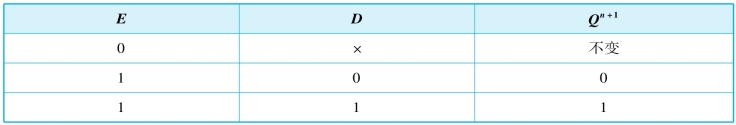

D锁存器的功能表如表7-2所示。

表7-2 D锁存器功能表(https://www.xing528.com)

D锁存器的功能可用特性方程Qn+1=D表示。Qn+1称为“次态”,是在使能信号作用下触发器将变成的状态。相对于次态,触发器当前的状态称为“现态”,用Qn表示。

2.集成8D锁存器74HC373

(1)引脚结构。

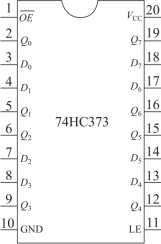

74HC373是中规模的集成8D锁存器,芯片封装形式为DIP20,有双列直插20个引脚,其引脚排列如图7-7所示。

图7-7 74HC373引脚排列

(2)引脚功能。

![]() 输出允许信号,低电平时锁存器数据才能输出。

输出允许信号,低电平时锁存器数据才能输出。

LE:使能信号,高电平时锁存器才能接收数据。

D0~D7:输入引脚。

Q0~Q7:输出引脚。

VCC:电源端。

GND:接地端。

(3)内部电路。

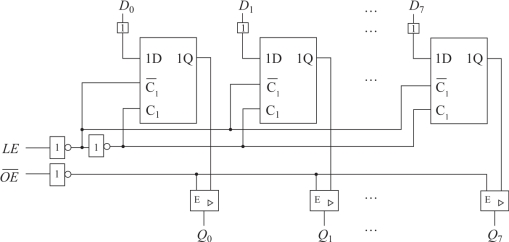

74HC373内部电路如图7-8所示。由图可见,74HC373主要由8个D锁存器和8个三态门构成。

图7-8 74HC373内部电路

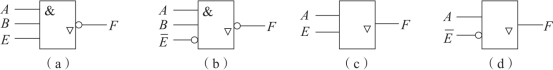

三态门是一种增加了使能控制端的逻辑器件。“三态”是指其输出有“0态”“1态”和“高阻态”3种状态。

图7-9所示为两类常见的三态门。图7-9(a)和图7-9(b)分别是高、低电平有效的三态与非门,图7-9(c)和图7-9(d)分别是高、低电平有效的三态传输门。

图7-9 常见三态门逻辑符号

(a)高电平有效三态与非门;(b)低电平有效三态与非门;(c)高电平有效三态传输门;(d)低电平有效三态传输门

对于高电平有效的三态与非门,当E=1时,![]() 低电平有效的三态与非门,当

低电平有效的三态与非门,当![]()

对于高电平有效的三态传输门,当E=1时,F=A;低电平有效的三态传输门,当![]() 时,F=A。

时,F=A。

(4)逻辑功能。

当LE=1时,非运算后,使8个D锁存器互反的使能控制端C1和的信号同时有效,8个D锁存器分别接收其输入端D0~D7输入的数据。

当![]()

![]() 时,非运算后,使输出三态传输门的使能控制信号有效,8个D锁存器数据可以传输到各自的输出端Q0~Q7。

时,非运算后,使输出三态传输门的使能控制信号有效,8个D锁存器数据可以传输到各自的输出端Q0~Q7。

7.2.3 ADC0809的地址译码锁存电路仿真

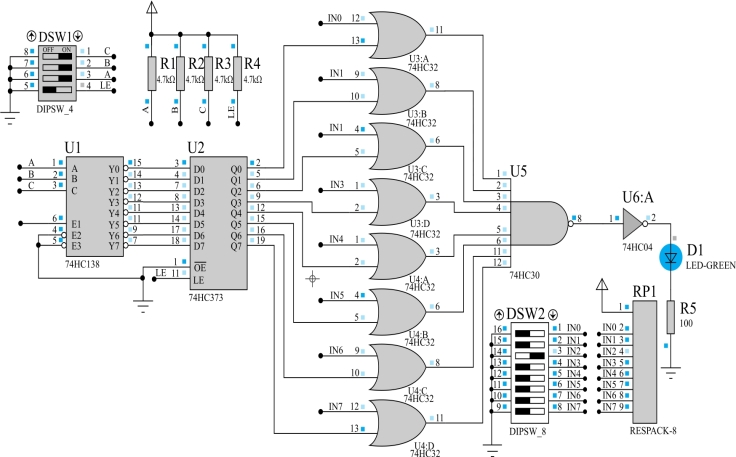

根据ADC0809的地址译码锁存电路的功能及实现方法,由Proteus仿真的案例电路如图7-10所示。

图7-10 ADC0809的地址译码锁存电路仿真

图7-10中,ADC0809的通道地址码从3-8译码器74HC138的输入端C、B、A输入,使对应用于通道地址码的输出端为低电平,在8D锁存器74HC373的使能信号LE=1时,该低电平信号进入锁存器锁存,在允许输出信号![]() 时,该低电平信号从锁存器输出,使对应的模拟输入通道INi的或门打开,实现了通道选择。

时,该低电平信号从锁存器输出,使对应的模拟输入通道INi的或门打开,实现了通道选择。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。