计数作为人们日常生活中的一项重要活动,无时无刻不在伴随着我们。原始社会人们曾用“结绳”“契刻”等方法进行计数,但人类最早的计数工具是我国春秋时期出现的“算筹”。算筹是用竹子、木头或兽骨做材料,约270枚一束,放在布袋里可随身携带。“算盘”也是我国彪炳史册的计数工具的另一项重大发明。

随着社会的发展和科技的不断进步,人类的计数工具逐渐从简单到复杂,从低级到高级。本项目的计数器是一种时序逻辑器件,可以对输入时钟脉冲的个数进行计数。计数值随输入时钟脉冲个数增加的为递增计数器,减少的为递减计数器。以二进制计数的为二进制计数器,以十进制计数的为十进制计数器。二进制计数器的计数值与位数有关,n位二进制计数器的计数值从0~2n-1,共2n个状态。计数器的计数状态数称为计数器的“模”,2n个计数状态的计数器即模为2n计数器。

计数器一般由触发器构成,但实际应用的计数器多为中规模集成计数器。74LS161和74LS90是两款较典型的集成计数器芯片。

微课 计数器认知

6.2.1 74LS161

1.引脚结构及功能

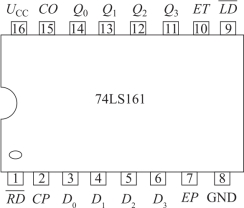

74LS161是4位二进制模16的中规模集成计数器芯片,采用DIP16的封装形式,其引脚结构如图6-8所示。

各引脚的功能如下。

UCC(16脚)为电源引脚,GND(8脚)为接地引脚。

![]() (1脚)为低电平有效的清0控制引脚。

(1脚)为低电平有效的清0控制引脚。

![]() (9脚)为低电平有效的预置数控制引脚。

(9脚)为低电平有效的预置数控制引脚。

ET(10脚)和EP(7脚)为高电平有效的计数控制引脚。

Q3、Q2、Q1、Q0(11~14脚)为从高到低的输出引脚。

D3、D2、D1、D0(6~3脚)为从高到低的预置数输入引脚。

CO(15脚)为进位输出引脚。

2.逻辑功能

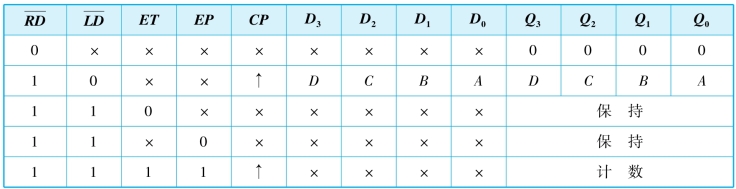

74LS161具有异步清0、同步预置数、计数和保持4个功能,其功能如表6-1所示。

图6-8 74LS161引脚排列

表6-1 74LS161的功能表

①异步清0功能。当![]() 时,不论CP端是否有时钟脉冲,输出端立即全部清0,这种不受时钟脉冲控制的清0功能称为“异步清0”。

时,不论CP端是否有时钟脉冲,输出端立即全部清0,这种不受时钟脉冲控制的清0功能称为“异步清0”。

②同步预置数功能。当![]() 时,计数器在时钟脉冲信号CP上升沿的作用下,输出端Q3Q2Q1Q0的值等于预置数输入端D3D2D1D0的值,这种在时钟信号的作用下才能实现的置数功能称“同步预置数”。

时,计数器在时钟脉冲信号CP上升沿的作用下,输出端Q3Q2Q1Q0的值等于预置数输入端D3D2D1D0的值,这种在时钟信号的作用下才能实现的置数功能称“同步预置数”。

③保持功能。当![]() 都为高电平,信号无效时,若ET或EP任意一个为低电平,计数器保持原来的状态不变,称为保持功能。

都为高电平,信号无效时,若ET或EP任意一个为低电平,计数器保持原来的状态不变,称为保持功能。

④计数功能。当![]() 时,在CP上升沿的作用下,计数器的值在0000~1111之间循环计数,即进行模16加法计数。当计数值Q3Q2Q1Q0=1111时,进位输出端CO输出高电平。

时,在CP上升沿的作用下,计数器的值在0000~1111之间循环计数,即进行模16加法计数。当计数值Q3Q2Q1Q0=1111时,进位输出端CO输出高电平。

6.2.2 74LS90

1.引脚结构及功能

74LS90是一个集成的二-五-十进制计数器,其内部有一个二进制计数器和一个五进制计数器。芯片封装形式为DIP14,即双列直插14个引脚,如图6-9所示。

由图可见,74LS90芯片的电源引脚和接地引脚的分布与之前的芯片有所不同,其引脚5是电源引脚UCC,引脚10为接地引脚GND。

其余各引脚的功能以下。

![]() (14脚)为二进制计数器的时钟输入端。

(14脚)为二进制计数器的时钟输入端。

![]() (1脚)为五进制计数器的时钟输入端。

(1脚)为五进制计数器的时钟输入端。

图6-9 74LS90的引脚排列

Q3Q2Q1Q0(11脚、8脚、9脚、12脚)为从高到低的计数器输出端,其中Q0为二进制计数器的输出端、Q3Q2Q1为五进制计数器的输出端。

R0A(2脚)和R0B(3脚)为高电平有效的清0引脚。

S9A(6脚)和S9B(7脚)为高电平有效的置9引脚。

NC(4脚和13脚)为空引脚。

2.逻辑功能

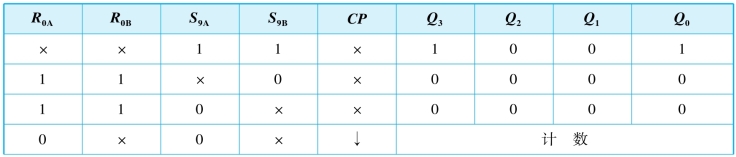

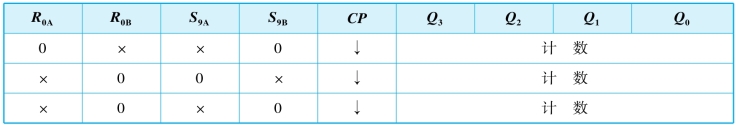

74LS90既可以作为二进制计数器使用,也可以作为五进制计数器使用,更多情况是接成8421BCD码的十进制计数器使用。_用74LS90作为8421BCD码的十进制计数器时,计数脉冲需从![]() (14脚)端输入,而

(14脚)端输入,而![]() (1脚)需与Q0短接,其功能如表6-2所示。

(1脚)需与Q0短接,其功能如表6-2所示。

表6-2 74LS90的真值表

续表

由表可见,74LS90作为8421BCD码的十进制计数器时,有清0、置9和计数3个功能。

①清0功能。当S9A和S9B不全为1,R0A=R0B=1时,计数器输出端Q3Q2Q1Q0输出为0000(“0”的8421BCD码),即十进制数清“0”。(https://www.xing528.com)

②置9功能。当S9A=S9B=1时,计数器输出端Q3Q2Q1Q0输出为1001(“9”的8421BCD码),即十进制数被置“9”。

③计数功能。当R0A和R0B任意一端为低电平,且S9A和S9B任意一端为低电平时,计数器在时钟脉冲的下降沿的作用下进行计数,计数值在0000~1001这10个状态之间循环。

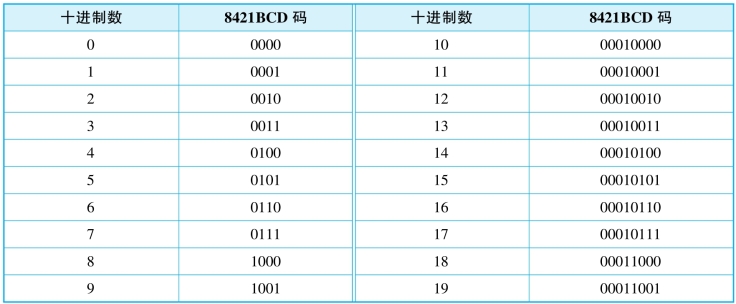

8421BCD码是将每一位十进制数都用4位二进制数表示,从高到低的权值分别是8-4-2-1,加权之和即为其表示的十进制数。0~19的8421BCD码如表6-3所示。

表6-3 0~19的8421BCD码

在用8421BCD码表示十进制数时,应注意两个问题:一是每个8421BCD码只能表示一位十进制数;二是BCD码是一种编码,与数值不同,数值的高位“0”不影响数值的大小,可以去掉,但编码要求足位,高位的“0”有效,不能随意去掉。

6.2.3 其他进制计数器

计数器的功能是计数,即累计输入的时钟脉冲的个数。计数器还可用于定时。如计数器的时钟脉冲频率为f,则其周期T=1/f,当其计数个数为n时,n·T即为其定时的时间。

实际应用中,对计数器的需求各种各样,如用于电子钟表计时的计数器需实现60 s、60 min、24 h的计数;交通灯中的倒计时器,需根据路口的车流量情况进行各种计数等。而计数器的芯片供应是无法满足这种无止境需求的。因此,实际应用所需的任意进制计数器是用典型的集成计数器芯片通过适当连接实现的。

1.用74LS161构成任意进制计数器

(1)实现思路。

如前所述,74LS161是一个集成4位二进制模16递增计数器,正常情况下其计数值在0000~1111这16个状态之间循环。用74LS161构成任意进制计数器的基本思路是,在其达到规定的最大计数值时,使其计数值强制为0或规定的最小值,这样其计数值就会在0与最大值之间或最小值与最大值之间循环,进行任意进制的计数。

为实现上述控制要求,需解决两个关键问题:

①如何使74LS161的计数值强制为0或规定的最小值;

②在74LS161达到规定的最大值时,用什么方法使其清0端![]() 或预置数控制端

或预置数控制端![]() 置入低电平信号?

置入低电平信号?

根据74LS161的逻辑功能,可以通过异步清0和同步预置数的功能解决其强制清0和置入最小值的问题。而控制计数器在达到规定的最大值时,使其清0端![]() 或预置数控制端

或预置数控制端![]() 置入低电平信号的方法,则可以通过适当的逻辑门将输出的最大计数值的相应位作逻辑运算后,反馈到清0端

置入低电平信号的方法,则可以通过适当的逻辑门将输出的最大计数值的相应位作逻辑运算后,反馈到清0端![]() 或预置数控制端

或预置数控制端![]() 。因为与非门具有“输入全1,输出为0”的逻辑功能,故用与非门将计数器为规定的最大计数值时输出为“1”的输出端,进行与非运算后,接入到74LS161的清0端

。因为与非门具有“输入全1,输出为0”的逻辑功能,故用与非门将计数器为规定的最大计数值时输出为“1”的输出端,进行与非运算后,接入到74LS161的清0端![]() 或预置数控制端

或预置数控制端![]() ,可以实现当计数值为规定的最大计数值时,

,可以实现当计数值为规定的最大计数值时,![]()

(2)实现方法。

因74LS161的异步清0功能和同步预置数功能都可控制计数器的最小值,故用74LS161构成任意进制计数器有两种方法:一是“反馈复位法”,二是“反馈置位法”。

①反馈复位法。反馈复位法是利用74LS161的异步清0功能,使计数器在达到计数值的最大值时,用与非门反馈给![]() 端一个低电平信号,使计数器强制清0。

端一个低电平信号,使计数器强制清0。

图6-10 十三进制计数器(反馈复位法)

图6-10所示案例是用74LS161的反馈复位法构成的十三进制计数器的实现方法。

由图可见,74LS161预置数控制端![]() 为无效信号;计数控制端ET=EP=1,为有效信号;异步清0端

为无效信号;计数控制端ET=EP=1,为有效信号;异步清0端![]() 通过与非门接在计数器的Q3Q2Q0端,在计数器的输出Q3Q2Q1Q0≠1101时,

通过与非门接在计数器的Q3Q2Q0端,在计数器的输出Q3Q2Q1Q0≠1101时,![]() ,为无效信号。故74LS161工作在计数状态,计数值从0000开始进行加1计数,当计数值达到1101时,异步清0端

,为无效信号。故74LS161工作在计数状态,计数值从0000开始进行加1计数,当计数值达到1101时,异步清0端![]() ,计数器立即清0,因此,计数器的有效计数状态为0000~1100,共13个状态,为十三进制计数器。

,计数器立即清0,因此,计数器的有效计数状态为0000~1100,共13个状态,为十三进制计数器。

采用反馈复位法构成任意进制计数器时,预置数输入端D3D2D1D0可为任意值,建议接地。同时,因是“异步清0”,反馈输出值需用计数器最大计数值N的下一个状态,即N+1反馈,这样计数器的计数值才能得到0~N个状态。

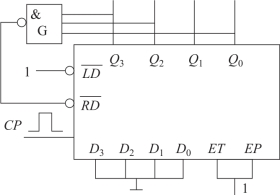

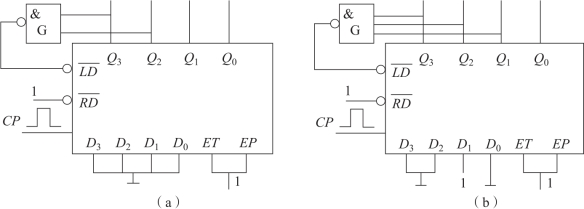

②反馈置位法。图6-11所示案例是用74LS161的反馈置位法构成的十三进制计数器的实现方法,其中图6-11(a)所示为计数最小值为0000的计数器的实现电路,图6-11(b)所示为计数最小值不是0000的计数器的实现电路。

图6-11 十三进制计数器(反馈置位法)

(a)计数值为0000~1100;(b)计数值为0010~1110

由图6-11(a)可见,74LS161异步清0端RD=1,为无效信号;计数控制端ET=EP=1,为有效信号;预置数控制端![]() 通过与非门接在计数器的Q3Q2端,预置数输入端D3D2D1D0=0000。在计数器的输出Q3Q2Q1Q0≠1100时,

通过与非门接在计数器的Q3Q2端,预置数输入端D3D2D1D0=0000。在计数器的输出Q3Q2Q1Q0≠1100时,![]() ,为无效信号。故74LS161工作在计数状态,计数值从0000开始进行加1计数,当计数值达到1100时,预置数控制端

,为无效信号。故74LS161工作在计数状态,计数值从0000开始进行加1计数,当计数值达到1100时,预置数控制端![]() ,计数器在时钟信号的上升沿时,置入D3D2D1D0输入的0000,Q3Q2Q1Q0从1100跳到0000,重新开始加1计数。因此,计数器的有效计数状态为0000~1100,共13个状态,为十三进制计数器。

,计数器在时钟信号的上升沿时,置入D3D2D1D0输入的0000,Q3Q2Q1Q0从1100跳到0000,重新开始加1计数。因此,计数器的有效计数状态为0000~1100,共13个状态,为十三进制计数器。

由图6-11_(b)可见,74LS161异步清0端与计数控制端的接法同图6-11(a);但其预置数控制端![]() 通过与非门接在计数器的Q3Q2Q1端,预置数输入端D3D2D1D0=0010。计数器的输出Q3Q2Q1Q0≠1110时,

通过与非门接在计数器的Q3Q2Q1端,预置数输入端D3D2D1D0=0010。计数器的输出Q3Q2Q1Q0≠1110时,![]() ,为无效信号。故74LS161工作在计数状态。计数开始时,计数器可能从0000开始加1计数,当计数值达到1110时,预置数控制端

,为无效信号。故74LS161工作在计数状态。计数开始时,计数器可能从0000开始加1计数,当计数值达到1110时,预置数控制端![]() 计数器在时钟信号的上升沿时,置入D3D2D1D0输入的0010,Q3Q2Q1Q0从1110跳到0010后,从0010开始进行加1计数,到1110时,又回到0010。因此,计数器的有效计数状态为0010~1110,共13个状态,为十三进制计数器。

计数器在时钟信号的上升沿时,置入D3D2D1D0输入的0010,Q3Q2Q1Q0从1110跳到0010后,从0010开始进行加1计数,到1110时,又回到0010。因此,计数器的有效计数状态为0010~1110,共13个状态,为十三进制计数器。

采用反馈置位法构成任意进制计数器时,预置数输入端D3D2D1D0需接入计数器的最小值。同时,因是“同步预置数”,在计数值达到最大值时,需要在时钟脉冲的下降沿,计数器才能置入D3D2D1D0输入的值,故可直接用计数器的最大计数值N反馈。

2.用74LS90构成任意进制计数器

(1)实现思路。

用74LS90构成任意进制计数器的思路与74LS161基本相同,即可使计数器工作在计数状态,利用其异步清0功能,在计数值达到要实现的计数器的最大计数值时,控制其异步清0端为有效信号,实现清0。因74LS90的清0信号为高电平有效,故反馈控制逻辑门需用与门。

(2)实现方法。

①10以内的任意进制计数器。74LS90芯片用作8421BCD码十进制计数时,其计数值在0~9间循环。因此,构成10以内进制的计数器,仅需一片74LS90。

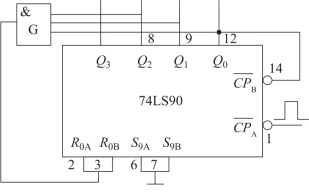

图6-12所示为计数值在0~6的七进制计数器的实现案例。

图6-12 用74LS90构成的7进制计数器

由图6-12可见,74LS90的计数脉冲从![]() (14脚)端接入;

(14脚)端接入;![]() (1脚)与Q0(12脚)短接;高电平有效的置9端S9A(6脚)、S9B(7脚)同时接地,为低电平无效信号;高电平有效的异步清0端R0A(2脚)和R0B(3脚)同时通过与门与计数器的输出端Q2Q1Q0(8、9、12脚)连接,当Q3Q2Q1Q0≠0111时,与运算使R0A=R0B=0,计数器工作在8421BCD码的计数状态,计数器从0000开始进行加1计数。当计数值Q2Q1Q0=0111时,与门使R0A=R0B=1,计数器立即清0,因此计数器的值在0000~0110间循环,为七进制计数器。

(1脚)与Q0(12脚)短接;高电平有效的置9端S9A(6脚)、S9B(7脚)同时接地,为低电平无效信号;高电平有效的异步清0端R0A(2脚)和R0B(3脚)同时通过与门与计数器的输出端Q2Q1Q0(8、9、12脚)连接,当Q3Q2Q1Q0≠0111时,与运算使R0A=R0B=0,计数器工作在8421BCD码的计数状态,计数器从0000开始进行加1计数。当计数值Q2Q1Q0=0111时,与门使R0A=R0B=1,计数器立即清0,因此计数器的值在0000~0110间循环,为七进制计数器。

与74LS161的反馈复位法相同,因是“异步清0”,需用计数器最大计数值N的下一个状态,即N+1反馈。

②11-100的任意进制计数器。当用74LS90构成计数值在11-99的计数器时,则需要2片74LS90;若构成计数值在100~999之间的计数器,则需要3片74LS90,以此类推。

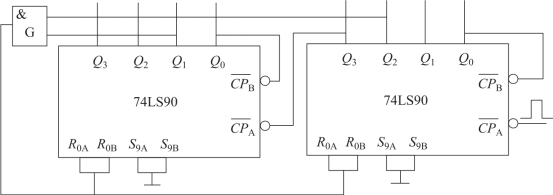

图6-13所示为用74LS90构成的24进制计数器的实现案例。

图6-13 用74LS90构成的24进制计数器逻辑图

由图6-13可见,电路中采用了两片74LS90芯片,且两芯片的高电平有效的置9端S9A和S9B均接地,两芯片的Q0均与各自的![]() 短接,两芯片的高电平有效的清0端短接后通过与门和十位(高位)芯片的_Q1端与低位芯片的Q2端连接,计数脉冲从个位(低位)芯片的

短接,两芯片的高电平有效的清0端短接后通过与门和十位(高位)芯片的_Q1端与低位芯片的Q2端连接,计数脉冲从个位(低位)芯片的![]() 端接入,高位芯片的

端接入,高位芯片的![]() 端与低位芯片的最高位Q3连接。因此,两芯片都工作在8421BCD码的十进制计数状态,在外部计数脉冲的每个下降沿,个位芯片从0000(0的8421BCD码)开始加1计数,当计数值达到1001(9的8421BCD码)时,下一个计数脉冲的下降沿,个位芯片的Q3端从1跳到0,为十位芯片的

端与低位芯片的最高位Q3连接。因此,两芯片都工作在8421BCD码的十进制计数状态,在外部计数脉冲的每个下降沿,个位芯片从0000(0的8421BCD码)开始加1计数,当计数值达到1001(9的8421BCD码)时,下一个计数脉冲的下降沿,个位芯片的Q3端从1跳到0,为十位芯片的![]() 端提供一个下降沿,十位芯片计数值加1,实现了“逢十进一”的进位操作。个位芯片又开始0000~1001的加1计数。当十位芯片的计数值Q3Q2Q1Q0=0010(2的8421BCD码)、个位芯片的计数值Q3Q2Q1Q0=0100(4的8421BCD码),即计数器的计数值为24时,两芯片的清0端同时得到高电平,两计数器芯片立即同时清0,因此电路的计数值是在十进制数的00~23间循环,为24进制计数器。

端提供一个下降沿,十位芯片计数值加1,实现了“逢十进一”的进位操作。个位芯片又开始0000~1001的加1计数。当十位芯片的计数值Q3Q2Q1Q0=0010(2的8421BCD码)、个位芯片的计数值Q3Q2Q1Q0=0100(4的8421BCD码),即计数器的计数值为24时,两芯片的清0端同时得到高电平,两计数器芯片立即同时清0,因此电路的计数值是在十进制数的00~23间循环,为24进制计数器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。