4.2.1 555定时器简介

555定时器是一种集成电路芯片,常被用于定时器、脉冲信号发生器和振荡电路,也可被作为电路中的延时器件、触发器或起振元件。

1.引脚结构

微课 555定时器认知

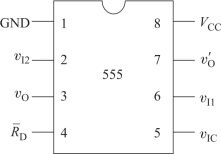

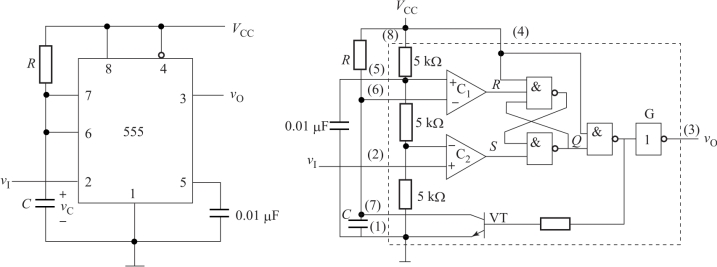

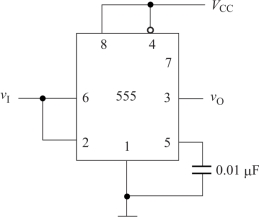

图4-4 555定时器引脚排列

555定时器的引脚排列如图4-4所示。其芯片封装为DIP8,即双列直插8个引脚。各引脚的功能如下。

引脚1(GND):接地引脚。

引脚2(TRIG,vI2):触发输入引脚,当此引脚电压降至1/3VCC(或由引脚5控制的阈值电压)时,输出端输出高电平。

引脚3(OUT,vO):输出引脚。

引脚4![]() 复位引脚,低电平有效,即该引脚为低电平时,555定时器输出端输出低电平。

复位引脚,低电平有效,即该引脚为低电平时,555定时器输出端输出低电平。

引脚5(CTRL,vIC):阈值电压控制引脚,控制芯片的阈值电压。该引脚接空时默认两阈值电压为1/3VCC与2/3VCC。

引脚6(THR,vI1):阈值输入引脚,当此引脚电压升至2/3VCC(或由引脚5控制的阈值电压)时,输出端输出低电平。

引脚7(DIS,v′O):放电端,内接晶体管,用于给电容放电。

引脚8(VCC):电源引脚。

2.工作特性

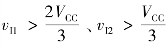

(1)![]() 时,输出vO为低电平。

时,输出vO为低电平。

(2)![]() 时,输出vO为高电平。

时,输出vO为高电平。

(3)![]() 时,输出vO保持不变。

时,输出vO保持不变。

3.电路结构

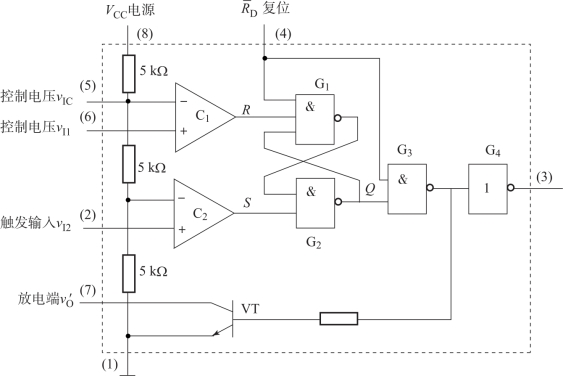

555定时器的内部电路如图4-5所示。

图4-5 555定时器的内部电路

由图可知,555定时器内部有一个由3个5 kΩ构成的分压电路、两个电压比较器、一个SR锁存器、一个放电晶体管、一个与非门和一个反相器。

4.工作原理

根据电阻串联分压原理,电路中由分压电路送至电压比较器C2的反相输入端的电压为1/3 VCC,送到电压比较器C1的同相输入端的电压为2/3 VCC。

因此,555定时器的特性可描述如下。

当 时,电压比较器C1因反相输入端电位大于同相输入端电位,输出低电平,SR锁存器的复位端R=0。电压比较器C2因同相输入端电位大于反相输入端电位,输出高电平,SR锁存器的置位端S=1。低电平有效的SR锁存器置0,即Q=0。其后的与非门输出高电平,放电晶体管T导通,再经反相缓冲器后,555定时器输出低电平。

时,电压比较器C1因反相输入端电位大于同相输入端电位,输出低电平,SR锁存器的复位端R=0。电压比较器C2因同相输入端电位大于反相输入端电位,输出高电平,SR锁存器的置位端S=1。低电平有效的SR锁存器置0,即Q=0。其后的与非门输出高电平,放电晶体管T导通,再经反相缓冲器后,555定时器输出低电平。

当![]() 时,电压比较器C1因反相输入端电位小于同相输入端电位,输出高电平,SR锁存器的复位端R=1。电压比较器C2因同相输入端电位小于反相输入端电位,输出低电平,SR锁存器的置位端S=0。低电平有效的SR锁存器置1,即Q=1,其后的与非门输出低电平,放电晶体管VT截止,再经反相缓冲器后,555定时器输出高电平。

时,电压比较器C1因反相输入端电位小于同相输入端电位,输出高电平,SR锁存器的复位端R=1。电压比较器C2因同相输入端电位小于反相输入端电位,输出低电平,SR锁存器的置位端S=0。低电平有效的SR锁存器置1,即Q=1,其后的与非门输出低电平,放电晶体管VT截止,再经反相缓冲器后,555定时器输出高电平。

当![]() 时,电压比较器C1因反相输入端电位小于同相输入端电位,输出高电平,SR锁存器的复位端R=1。电压比较器C2因反相输入端电位也小于同相输入端电位,输出也为高电平,SR锁存器的置位端S=1。低电平触发的SR锁存器,保持原来的状态,故555定时器也保持原来的状态。

时,电压比较器C1因反相输入端电位小于同相输入端电位,输出高电平,SR锁存器的复位端R=1。电压比较器C2因反相输入端电位也小于同相输入端电位,输出也为高电平,SR锁存器的置位端S=1。低电平触发的SR锁存器,保持原来的状态,故555定时器也保持原来的状态。

4.2.2 555定时器典型应用

1.多谐振荡电路

多谐振荡电路是一种能产生矩形波的自激振荡器,也称为矩形波发生器。在接通电源后,不需要外加脉冲就能自动产生矩形脉冲。

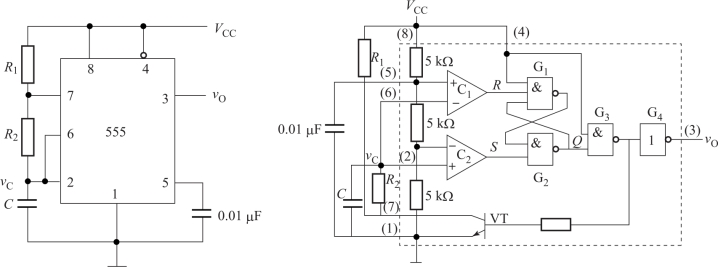

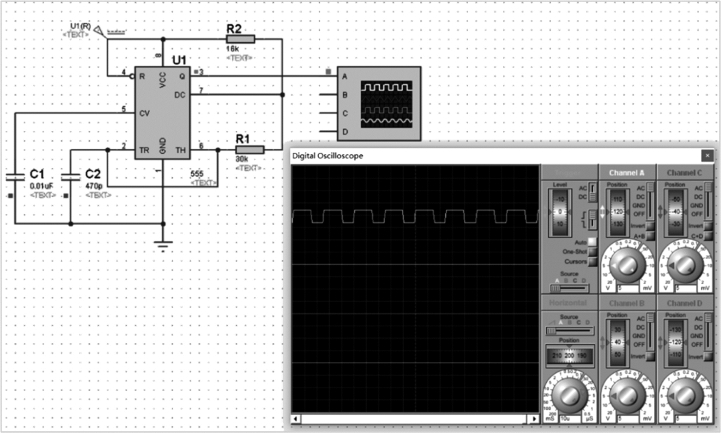

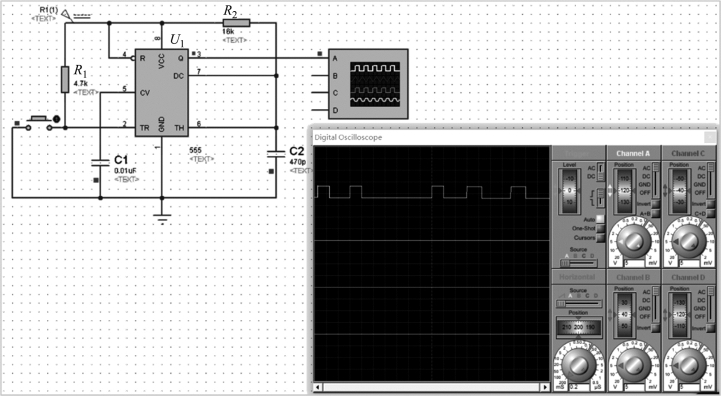

由555定时器构成的多谐振荡电路如图4-6所示。电路的Proteus仿真波形如图4-7所示。

微课 555定时器典型应用

(https://www.xing528.com)

(https://www.xing528.com)

图4-6 基于555定时器的多谐振荡电路

由图4-6可见,555定时器的阈值输入引脚6和触发输入引脚2短接之后,通过电容C接地,电路没有外部信号的输入端,因此,电路的振荡为自激振荡。

电路的工作过程:接通电源后,电容C通过电阻R1、R2充电,当电容电压vC上升至![]() 时,SR锁存器的S=1,R=0,输出Q=0,电路输出vO=0,放电晶体管VT导通。电容C通过电阻R2和放电晶体管VT放电,当vC减小到

时,SR锁存器的S=1,R=0,输出Q=0,电路输出vO=0,放电晶体管VT导通。电容C通过电阻R2和放电晶体管VT放电,当vC减小到![]() 时,S=0,R=1,输出Q=1,电路输出vO=1,放电晶体管VT截止,电容C又开始充电。如此往复,电路输出端vO在0~1之间循环切换,电路没有稳定状态。

时,S=0,R=1,输出Q=1,电路输出vO=1,放电晶体管VT截止,电容C又开始充电。如此往复,电路输出端vO在0~1之间循环切换,电路没有稳定状态。

图4-7 基于555定时器的多谐振荡电路仿真波形

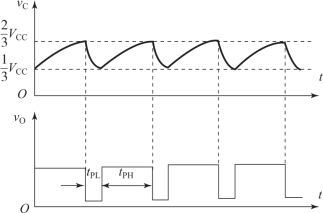

电容电压vC和输出电压vO的波形如图4-8所示。

图4-8 基于555定时器的多谐振荡电路输出波形

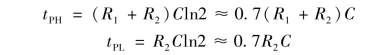

图中,tPH为正脉冲持续时间,即电容充电时间;tPL为负脉冲持续时间。经过分析计算,得

故振荡脉冲的周期和频率分别为

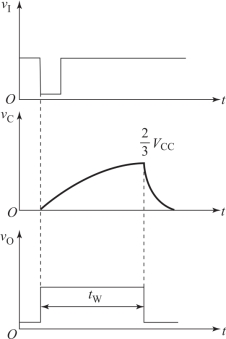

2.单稳态触发电路

单稳态触发器是有一个稳定状态和一个暂稳态的脉冲信号发生电路。在外加脉冲的作用下,单稳态触发器可以从一个稳定状态翻转到一个暂稳态,之后在电路的RC延时环节的作用下,该暂稳态维持一段时间又回到原来的稳态,暂稳态维持的时间取决于RC的参数值。

由555定时器构成的单稳态触发电路如图4-9所示,Proteus仿真结果如图4-10所示。

图4-9 基于555定时器的单稳态触发电路

图4-10 基于555定时器的单稳态触发电路仿真结果

由图4-9可见,555定时器的触发输入引脚2用于外部触发信号输入端,阈值输入引脚6与引脚7短接后,通过电容C接地。

电路的工作过程:无触发信号输入时,![]() ,电压比较器C2的同相输入端电位高于反相输入端电位,锁存器的置位端S=1。

,电压比较器C2的同相输入端电位高于反相输入端电位,锁存器的置位端S=1。

若通电后锁存器的输出Q=0,则电路输出vO=0,放电晶体管VT导通,电容C通过晶体管VT放电,电容电压降低,当其降至![]() 以下时,电压比较器C1的同相输入端电位高于反相输入端电位,锁存器的复位端R=1,SR锁存器保持Q=0的状态,vO稳定输出低电平。

以下时,电压比较器C1的同相输入端电位高于反相输入端电位,锁存器的复位端R=1,SR锁存器保持Q=0的状态,vO稳定输出低电平。

若通电后锁存器的输出Q=1,则电路输出vO=1,放电晶体管VT截止,电源通过电阻R向电容C充电,电容电压升高,当其上升至![]() 以上时,电压比较器C1的反相输入端电位高于同相输入端电位,锁存器的复位端R=0,SR锁存器输出端Q=0,vO输出低电平,放电晶体管导通,电容器C又开始放电,当电容电压下降至

以上时,电压比较器C1的反相输入端电位高于同相输入端电位,锁存器的复位端R=0,SR锁存器输出端Q=0,vO输出低电平,放电晶体管导通,电容器C又开始放电,当电容电压下降至![]() 以下时,R=1,SR锁存器保持Q=0的状态,使vO稳定,输出低电平。

以下时,R=1,SR锁存器保持Q=0的状态,使vO稳定,输出低电平。

当输入端施加触发负脉冲信号时,![]() ,电压比较器C2的同相输入端电位低于反相输入端电位,锁存器的置位端S=0,SR锁存器Q=1,电路输出vO=1,进入暂稳态。这时,放电晶体管VT截止,电源通过电阻R给电容C充电,当电容电压上升至

,电压比较器C2的同相输入端电位低于反相输入端电位,锁存器的置位端S=0,SR锁存器Q=1,电路输出vO=1,进入暂稳态。这时,放电晶体管VT截止,电源通过电阻R给电容C充电,当电容电压上升至![]() 以上时,电压比较器C1的反相输入端电位高于同相输入端电位,锁存器复位端R=0。因这时触发负脉冲已撤销,锁存器的复位端S=1,故SR锁存器输出端Q=0,vO恢复到低电平。放电晶体管VT导通,电容器开始放电,当电容电压降至

以上时,电压比较器C1的反相输入端电位高于同相输入端电位,锁存器复位端R=0。因这时触发负脉冲已撤销,锁存器的复位端S=1,故SR锁存器输出端Q=0,vO恢复到低电平。放电晶体管VT导通,电容器开始放电,当电容电压降至![]() 以下时,锁存器复位端R=1,保持了vO稳定,输出低电平。

以下时,锁存器复位端R=1,保持了vO稳定,输出低电平。

单稳态触发电路在触发负脉冲的作用下,进入暂稳态,输出正脉冲的宽度由电容C的充电时间常数决定,tW=RC ln3≈1.1RC,其波形如图4-11所示。

单稳态触发电路通常用于脉冲的整形、延时及定时等。

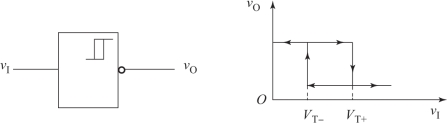

3.施密特触发电路

施密特触发器是一种有两个稳定状态的脉冲信号发生电路。与多谐振荡电路、单稳态触发电路等信号发生电路不同,施密特触发器采用电位触发方式,其状态由输入信号电位维持,且有正向阈值VT+和负向阈值VT-两个不同的触发电位。当输入电位上升到VT+以上时,输出低电平;当输入电压减小到VT-以下时,输出高电平。两个阈值电压之差ΔVT=VT+-VT-,称为回差电压。

施密特触发器的逻辑符号及工作特性如图4-12所示。

图4-11 基于555的单稳态触发电路输出波形

图4-12 施密特触发器的逻辑符号及工作特性

由555定时器构成的施密特触发电路如图4-13所示。

由图可见,555定时器的阈值输入引脚和触发引脚短接后作为施密特触发器的输入引脚。根据555定时器的特性,当输入电位大于2/3VCC时,vO输出低电平;当输入电位小于1/3VCC时,vO输出高电平。故正向阈值电压是2/3VCC,负向阈值电压是1/3VCC。

施密特触发器常用于波形变换(如正弦变余弦)、波形整形与抗干扰、幅度鉴别等。

图4-13 基于555定时器的施密特触发器

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。