2.3.1 逻辑运算

逻辑门与锁存器是逻辑电路的基础。逻辑电路是实现逻辑运算的电路。逻辑运算是对逻辑变量进行的运算,逻辑变量的值是仅取“0”或“1”的逻辑值,其中“0”表示低电平,“1”表示高电平。

常用的逻辑运算有与运算、或运算、非运算3种基本运算,以及由其组合而成的与非运算、或非运算、异或运算等。

1.与运算

微课 逻辑门认知

与逻辑关系是指“当决定某一事件发生的条件全具备时,事件才能发生”的逻辑关系。比如,“全面小康的路上,一个都不能少”就是一个典型的与逻辑关系。

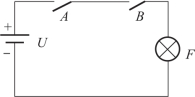

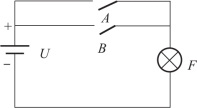

与逻辑可以用图2-4所示的电路来说明。根据电路知识,只有当两个开关A、B全闭合时,灯F才能亮;有一个开关断开,灯F就会灭。若设开关闭合为1、断开为0;灯亮为1、灯灭为0;这种逻辑关系可用表2-1所示真值表描述。

图2-4 串联开关电路

表2-1 与逻辑真值表

(1)与运算表达式。

设图2-4所示电路中,A、B为输入变量,F为输出变量,则有

![]()

(2)与运算法则。

0·0=0,0·1=0,1·0=0,1·1=1。

即:输入有0,输出为0;输入全1时,输出为1。

2.或运算

或逻辑关系是指“当决定某一事件发生的条件有一个具备时,事件就能发生”的逻辑关系,如成语“一荣俱荣”“一损俱损”就体现了或的逻辑关系。

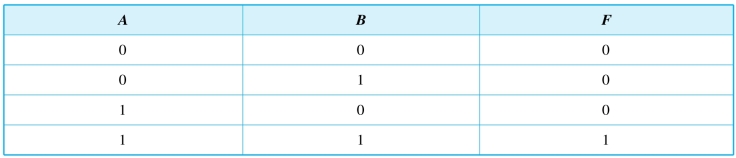

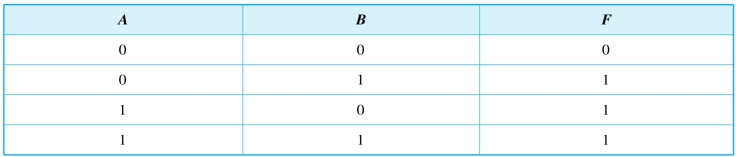

或逻辑可以用图2-5所示的电路来说明。图中,当开关A和B有一个闭合时,灯F就可以亮;只有当两个开关全断开,灯F才会灭。所以,开关A,B之间是或的关系。这种逻辑关系可用表2-2所示真值表描述。

图2-5 并联开关电路

表2-2 或逻辑真值表

(1)或运算表达式。

在设F为输出变量,A、B为输入变量的情况下,则有

![]()

(2)或运算法则。

0+0=0,0+1=1,1+0=1,1+1=1。

即:输入有1,输出为1;输入全0,输出为0。

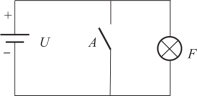

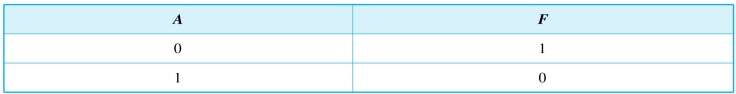

3.非运算

非逻辑是指“如果决定某一事情的条件具备了,结果便不发生;而条件不具备时,结果才发生”的逻辑关系,如“坚不可摧”就体现了一种非的逻辑关系。

非逻辑可以用图2-6所示电路来说明。图中,开关A与灯F并联,所以当开关A闭合时,灯F被开关短接,不亮;只有当开关A断开时,灯F才会亮。称为非逻辑关系,即条件总是与结果相反的逻辑关系。所以,开关A和灯F之间是非逻辑关系。表2-3是非运算的真值表。

图2-6 开关短接电路

表2-3 非运算真值表

(1)非运算表达式。

设输入变量为A,输出变量为F,则有

![]()

(2)非运算法则。

![]()

即:输入为0,输出为1;输入为1,输出为0。

4.与非运算

与运算之后,再进行非运算,就构成与非运算。与非运算法则是:输入有0,输出为1;输入全1,输出为0。

逻辑表达式为

![]()

5.或非运算

或运算之后,再进行非运算,就构成或非运算。或非运算法则是:输入有1,输出为0;输入全0,输出为1。

逻辑表达式为

![]()

6.异或运算

(1)两变量异或。

①逻辑功能:两变量取值相同时,异或运算后结果为0;两变量取值不同时,异或运算结果为1。

②逻辑表达式为

![]()

(2)3个以上变量异或。

①逻辑功能:3个以上变量进行异或运算时,若取值为1的输入变量个数为奇数,输出为1;若取值为1的输入变量个数为偶数,输出为0。

②逻辑表达式为

![]()

③逻辑含义:当输入变量A、B、C取001、010、100、111时,输出逻辑值为1。

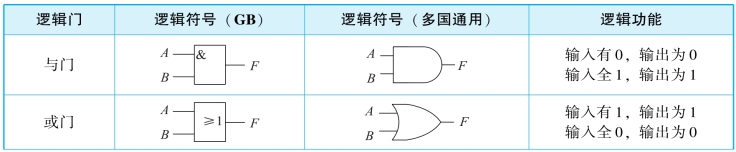

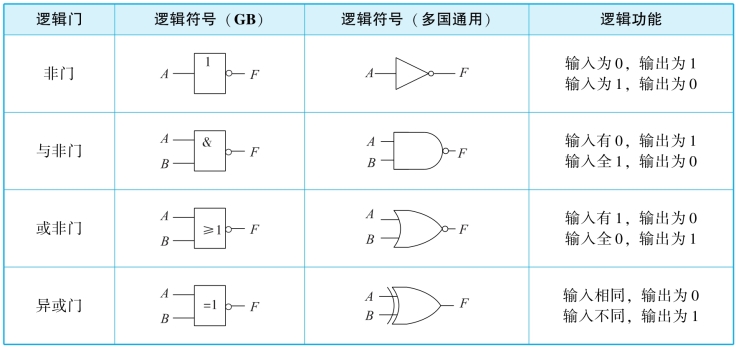

2.3.2 常用逻辑门及功能

常用的逻辑门有与门、或门、非门、与非门、或非门、异或门等,分别用于实现与运算、或运算、非运算、与非运算、或非运算、异或运算等。

常用逻辑门的逻辑符号及逻辑功能如表2-4所示。

表2-4 常用逻辑门的逻辑符号及逻辑功能

续表

2.3.3 集成逻辑门简介

1.半导体集成电路概述

在实际应用逻辑器件时,通常都采用集成逻辑电路芯片(Integrated Circuit,IC)。集成逻辑门是将多个逻辑门集成在一块半导体芯片上的逻辑器件。

集成电路按导电类型可分为双极型(TTL)集成电路和单极型(CMOS)集成电路。双极型集成电路是由晶体管构成的集成电路,其制作工艺复杂、功耗较大,代表产品主要是74[2]系列的74LS和74ALS[3];单极型集成电路是由CMOS[4]构成的集成电路,其制作工艺简单,功耗较低,易于制成大规模集成电路,代表产品主要有74系列的74HC、74HCT[5]和40××系列。

集成逻辑门在使用时,需根据其型号选用。但不同公司生产的半导体集成芯片型号含义不同,一般用头字母识别产地或厂商。例如,国产芯片的头字母为C;日本日立公司生产的数字集成电路芯片头字母为HD;日本索尼公司生产的混合集成电路头字母为BX或SBX;美国无线电公司生产的数字电路芯片头字母为CD;美国摩托罗拉公司生产的集成芯片头字母为M;美国德克萨斯公司标准电路字头为SN等。其余部分一般给出器件类型、设计序号、工作温度、封装形式等信息。

(https://www.xing528.com)

(https://www.xing528.com)

延伸阅读2

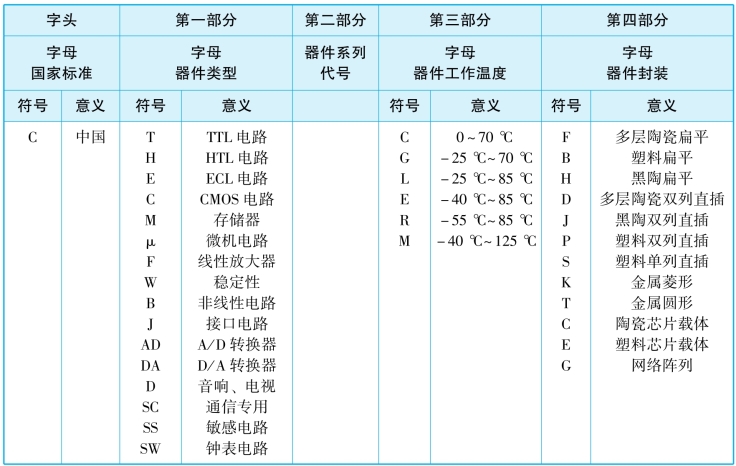

现仅介绍国产半导体集成芯片的命名方式及含义,其他请读者根据需要自行查阅相关资料。

国产半导体集成芯片的命名根据是《半导体集成电路型号命名方法》(GB 3430—1989)。集成电路的型号由五部分构成,含义如表2-5所示。

表2-5 国产集成电路的型号(GB 3430—1989)

2.常用集成逻辑门

集成逻辑门应用的关键是清楚其引脚结构及功能。下面通过几个典型的集成逻辑门,来介绍如何正确使用集成芯片。

(1)集成与门。

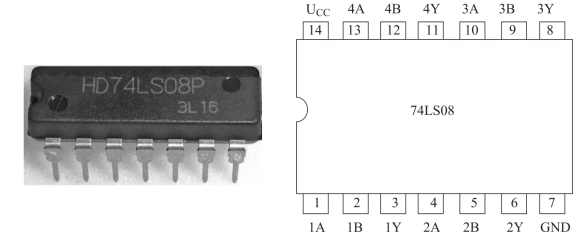

74LS08是一款DIP14型封装,即双列直插14个引脚的四-二输入的集成与门,其外形结构及引脚如图2-7所示。

图2-7 74LS08结构及引脚排列

由引脚图可见,74LS08内有4个独立的与门,其中,引脚7为接地引脚,引脚14为电源引脚;引脚1、2、3为一个与门,1、2为输入,3为输出;引脚4、5、6为一个与门,4、5为输入,6为输出;引脚8、9、10为一个与门,9、10为输入,8为输出;引脚11、12、13为一个与门,12、13为输入,11为输出。

CD4081是40××系列的集成四-二输入与门,其引脚结构与74LS08不同,如图2-8所示。

(2)集成或门。

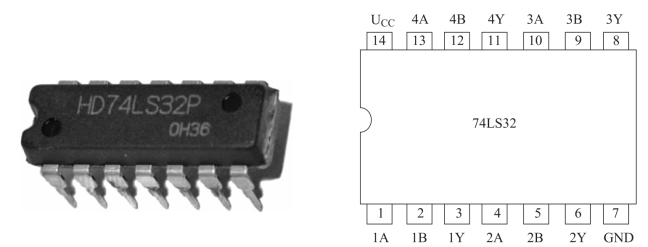

74LS32是一个双列直插14个引脚的四-二输入的集成或门,其外形结构及引脚如图2-9所示。

图2-8 CD4081引脚排列

图2-9 74LS32结构及引脚排列

由引脚图可见,74LS32内有4个独立的或门,其中,引脚7为接地引脚,引脚14为电源引脚;引脚1、2、3为一个或门,1、2为输入,3为输出;引脚4、5、6为一个或门,4、5为输入,6为输出;引脚8、9、10为一个或门,9、10为输入,8为输出;引脚11、12、13为一个或门,12、13为输入,11为输出。

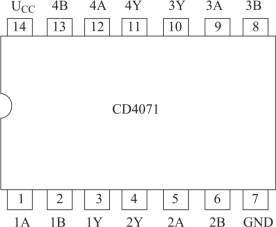

CD4071是40××系列的一款集成四-二输入或门,其引脚排列如图2-10所示。

(3)集成非门(反相器)。

74LS04是74系列的一款双列直插14个引脚的集成六反相器,其外形结构及引脚如图2-11所示。

由引脚图可见,74LS04内有6个独立的反相器,即非门。其中,引脚7为接地引脚,引脚14为电源引脚;其他引脚中1A~6A为输入,1Y~6Y为输出。

图2-10 CD4071引脚图

图2-11 74LS04结构及引脚排列

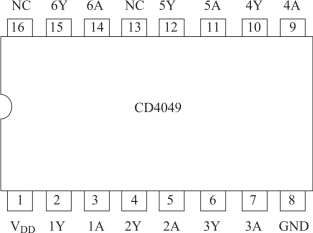

CD4049是40××系列的集成六反相器,其引脚结构为双列直插16脚,引脚排列如图2-12所示。其中1A~6A为输入。1Y~6Y为输出,NC为空引脚。使用时,需特别注意该芯片的电源引脚。

图2-12 CD4049引脚排列

(4)集成与非门。

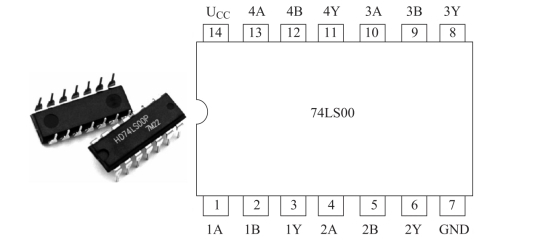

74LS00是74系列的一款双列直插14个引脚的四-二输入集成与非门,其外观结构及引脚如图2-13所示。

图2-13 74LS00结构及引脚排列

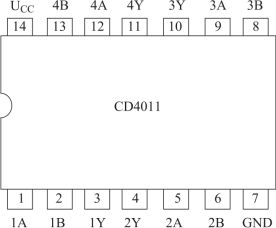

CD4011是40××系列的四-二输入集成与非门,其引脚排列如图2-14所示。

图2-14 CD4011引脚排列

(5)集成或非门。

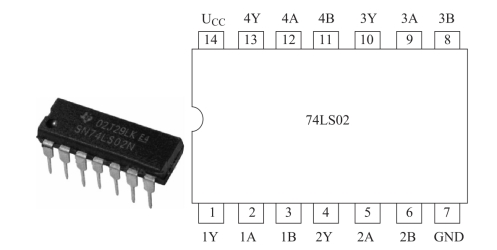

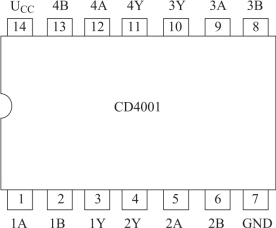

74LS02是74系列的一款双列直插14个引脚的四-二输入的集成或非门,其外观结构及引脚如图2-15所示。CD4001是40××系列的四-二输入集成或非门,其引脚排列如图2-16所示。

图2-15 74LS02的结构及引脚排列

图2-16 CD4001引脚排列

(6)多输入与非门。

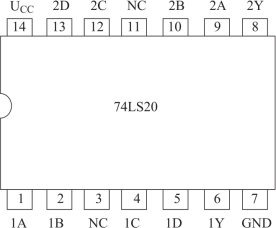

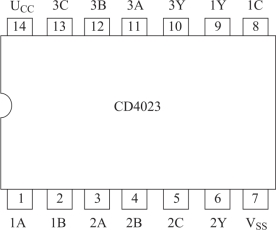

74LS20是74系列的一款双列直插14个引脚的二-四输入的集成与非门,其引脚如图2-17所示。CD4023是40××系列的三-三输入集成与非门,其引脚结构如图2-18所示。

图2-17 74LS20的引脚排列

图2-18 CD4023的引脚排列

在应用集成逻辑门时,对多余不用的输入端需要做适当处理。理论上,数字逻辑器件的输入端如果悬空不接,相当于接高电平,但实际使用时应避免悬空,因为会引入干扰信号。一般的处理方法如下。

①与门、与非门因其对低电平信号敏感,当有输入端为低电平时,其他输入端的信号将不起作用,故多余不用的输入端通常接电源(高电平)或与其他已用的输入端短接。

②或门、或非门因其对高电平信号敏感,当有输入端为高电平时,其他输入端的信号将不起作用,故多余不用的输入端通常接地(低电平)或与其他已用的输入端短接。

(7)异或门。

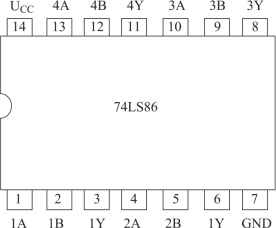

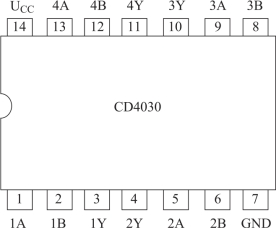

74LS86是74系列的一款双列直插14个引脚的二-四输入异或门,其引脚如图2-19所示。CD4030是40××系列的四-二输入异或门,其引脚结构如图2-20所示。

图2-19 74LS86的引脚排列

图2-20 CD4030的引脚排列

2.3.4 基本SR锁存器

锁存器是一种能记忆电路原来状态、具有存储功能的逻辑器件。锁存器是时序逻辑电路[6]必不可少的器件。

与锁存器功能相近的是触发器,两者的区别是:锁存器以电平信号驱动,而触发器则以脉冲信号边沿驱动。常见的锁存器有基本SR锁存器和D锁存器,关于D锁存器和触发器的内容将在项目7中介绍。

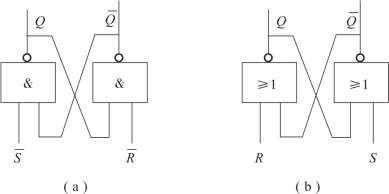

根据触发电平不同,基本SR锁存器可分为高电平有效SR锁存器和低电平有效SR锁存器两种。其中,低电平有效SR锁存器由两个与非门交叉连接构成,高电平有效SR锁存器由两个或非门交叉连接构成,如图2-21(a)和图2-21(b)所示。

微课 基本SR锁存器认知

图2-21 基本SR锁存器

(a)低电平有效;(b)高电平有效

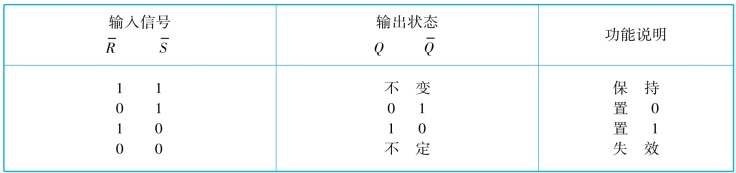

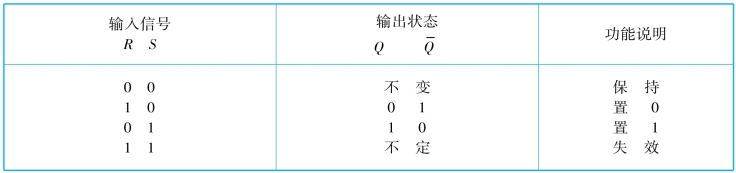

基本SR锁存器有S、R两个输入端和两个互补的输出端Q和![]() 。其中S端为置位端、R端为复位端。两种类型的SR锁存器的逻辑功能如表2-6和表2-7所示。

。其中S端为置位端、R端为复位端。两种类型的SR锁存器的逻辑功能如表2-6和表2-7所示。

表2-6 低电平有效的SR锁存器

表2-7 高电平有效的SR锁存器

由基本SR锁存器的功能可知,当其置位端和复位端同时输入有效信号时,触发器的状态将无法确定,完全由构成触发器的逻辑门的导通速度快慢决定,因此,实际应用中是不允许出现这种状态的。故对于基本SR锁存器,需加约束条件:SR=0,即不允许S、R同时为1或![]() 同时为0。

同时为0。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。