1.A/D转换芯片主要性能指标

1)分辨率是使A/D转换输出数码变动一个LSB(最低有效位)时的模拟信号的最小变化量。在一个n位的A/D中,分辨率等于最大允许的模拟量除以2n。A/D的分辨率与输出数字位数有直接关系,一般用A/D的位数表示其分辨率。

2)转换时间是A/D从启动转换到转换结束所需的时间为转换时间。这个指标表示A/D的采样速度,即A/D在每秒钟内所完成的转换次数。

3)转换误差是A/D转换结果的实际值与真实值之间的偏差,用最低有效位数LSB或满度值的百分比表示。转换误差包括量化误差(因量化单位有限所造成的误差)、偏移误差(零输入信号时输出信号的数值)、量程误差(转换器在满度时的误差)、非线性误差(转换器特性偏离直线的程度)等。

在选择A/D时,分辨率和转换时间是首要考虑的指标,因为这两个指标直接影响仪器的测量、控制和响应速度。选用高分辨率和高转换速度的A/D,可以提高仪器的精度和指标,但仪器的成本也提高。另外,在确定分辨率指标时,应留有余量,因为放大器、多路开关、采样/保持等也会引入误差。

2.多路切换采样与同步采样

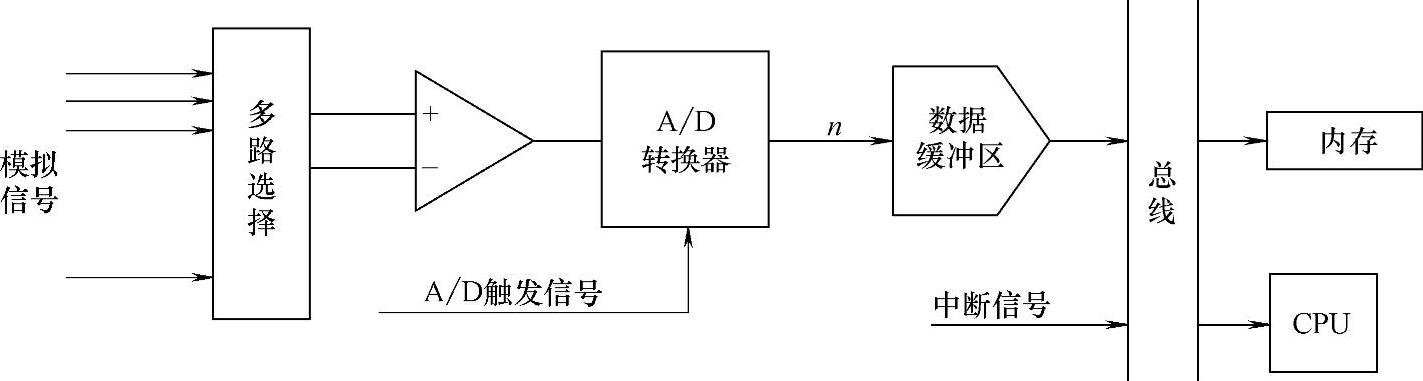

在数据采集系统中,往往要对多个物理量进行采集,即所谓多路巡回检测,这可通过多路模拟开关来实现。多路模拟开关可以分时选通来自多个输入通道的某一信号,在物理量变化比较缓慢、变化周期在数十至数百毫秒之间的情况下,可以使用普通的数十微秒A/D转换器从容地分时处理这些信号。但当信号频率较高时,使用多路模拟开关后,对A/D的转换速率要求也随之上升。在数据采样率超过40~50kHz时,一般不再使用分时的多路开关技术,而采用同步A/D采样技术。图4-25是多路切换采样结构,它只采用一个A/D芯片,通过多路转换开关实现不同通道的切换转换。图4-26是多路同步采样结构,它采用多个A/D芯片,不同通道采用同一时钟,保证不同通道的采样时间相同,实现信号的同步采样。

图4-25 多路切换采样结构

图4-26 多路同步采样结构

3.触发(Trigger)

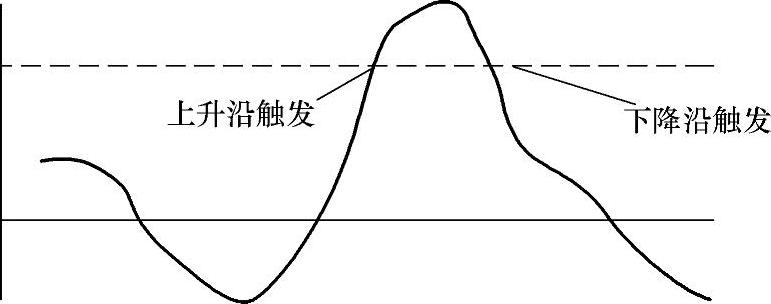

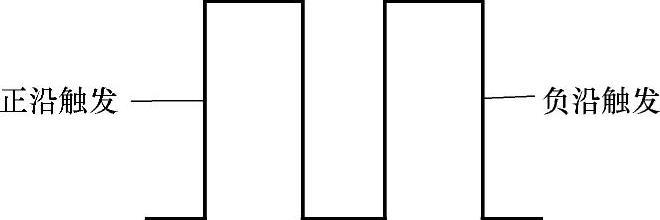

触发是启动、停止采集事件的方法。触发可分为软件触发和硬件触发,软件触发适用于用户需要对所有采集事件进行明确控制或时间要求不甚严格的场合。硬件触发适用于采集事件需要与外部装置严格同步或高速、瞬态采集的场合。触发有模拟触发和数字触发两种方式,如图4-27和图4-28所示。按触发时间的不同,有如图4-29所示的延时触发、预触发、中触发、后触发等方式。

4.数据传送的基本方式

数据采集系统实现模拟量到数字量的转换,然后由CPU进行数据处理,数字接口实现转换结果到CPU内存的传送。一般采用下面三种传送方法。

(https://www.xing528.com)

(https://www.xing528.com)

图4-27 模拟触发

图4-28 数字触发

图4-29 不同时刻的触发方式

(1)查询方式 这种传送方式是异步的,CPU通过查询A/D状态位实现数据传送。握手过程如下:CPU向输出端口发出写指令,触发一次A/D转换;通过输入端口读一个查询标志位,如果该标志位为0,则循环等待,直到该标志位为1;通过输入端口将A/D转换的数据读入,完成一次转换过程。重复这个过程可以进行连续转换。

一般该标志位由A/D芯片硬件实现,A/D转换结束设置标志位,CPU通过查询该标志位,读取转换结果,读取后应清除。

查询方式接口简单,可以随时读取变换数据,也可以插入一定的延时子程序来完成周期性的连续变换,都是较常用的方法。但是由于要占用CPU时间进行查询,所以采样速度较低,而且采样周期定时精度低。

(2)中断方式 计算机系统设有中断处理能力,可以将CPU从大量的查询工作解脱出来。由硬件或CPU启动A/D转换,利用A/D转换结束标志申请中断,中断响应以后调用中断处理程序将数据读进内存。

PC机一次中断响应时间为十几微秒,如果中断处理程序执行时间再占用十几微秒,利用中断读取一个数据的时间粗略计算大约为几十微秒,因此,中断方式数据传送的最高速度大约是几十千赫。

如果利用双RAM,每个RAM写满后再申请中断,CPU读取该RAM,同时A/D转换器写另一RAM,这种方式可以提高几倍传送速度,但接口电路要复杂得多,更好的选择是采用DMA方式。

(3)DMA方式 用DMA方式可实现高速数据传送,高档数据采集系统一般采用这种数据传送方式。DMA数据传送可以实现外设同内存的数据直接传送,由DMA控制器提供目标地址和总线控制,DMA传送接口由专用DMA控制器实现,硬件接口更复杂,占用CPU资源,必须软硬件配合。

(4)存储器缓存方式 在超高速的数据采集系统中,数据的采集速率大于微机系统总线的最高传送速率,这种情况下必须在采集系统中加入存储器作缓存。将一组数据先采集并存储在缓存中,然后再成批向主机传送。

最简单的缓存器是只设计一个FIFO存储区,启动一个采集过程存储一组数据在该存储区中,然后申请系统总线将该存储区内容倒入主机内存中,然后再启动一个采集过程,重复上述操作。这种结构支持只需要一组或两组数据之间有较大的停顿的应用场合。

另一种缓存器结构是设计两个存储区,交替使用,第一组数据存入第一存储区,第二组数据采集开始后,第一存储区向主机内存倒入数据,新采集的数据存入第二存储区,启动第三组数据采集开始时,第一存储区已空,新的数据存入第一存储区,第二存储区的数据此时正倒入主机内存,两个存储区交替地收发。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。