(1)基本组成

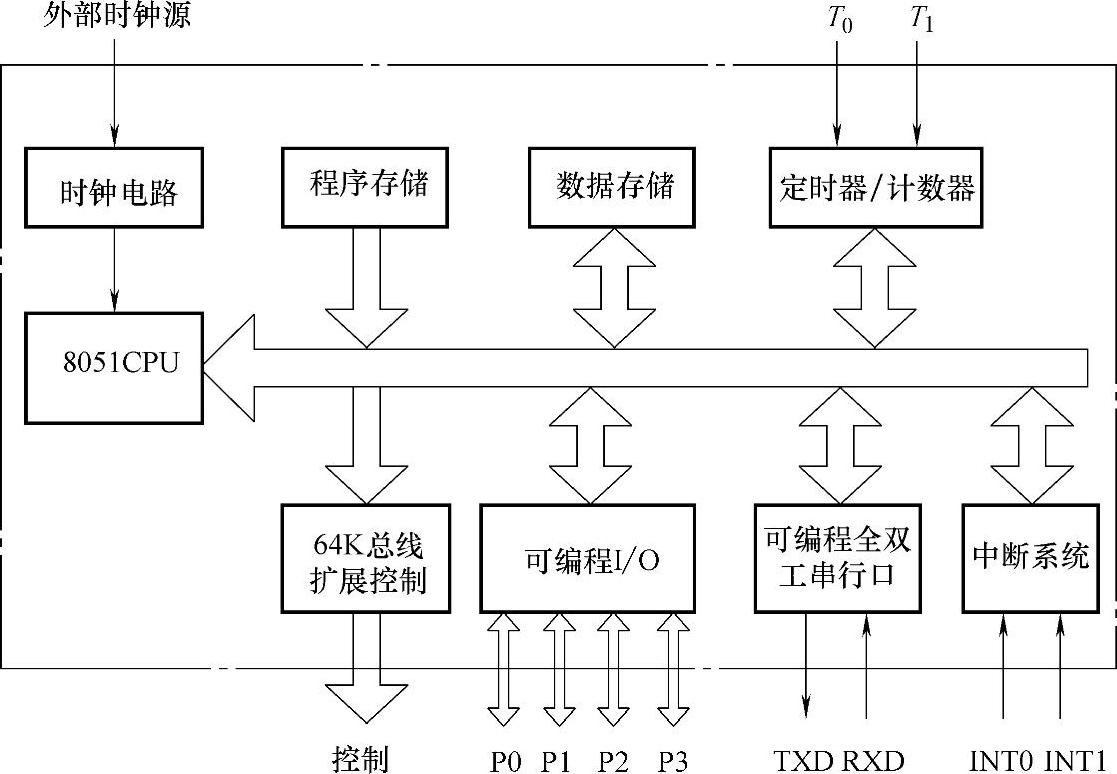

8051单片机功能结构示意如图5-39所示。

8051单片机包括中央处理器、程序存储器(ROM)、数据存储器(RAM)、定时器/计数器、并行接口、串行接口和中断系统等几大单元。

图5-39 8051单片机功能结构示意图

中央处理器(CPU)是整个单片机的核心部件,是8位数据宽度的处理器,能处理8位二进制数据或代码。CPU负责控制、指挥和调度整个单元系统协调的工作,完成运算和控制输入输出功能等操作。

数据存储器(RAM)有128个8位用户数据存储单元和128个专用寄存器单元,它们是统一编址的,其中专用寄存器只能用于存放控制指令数据,用户只能访问,而不能用于存放用户数据。所以,用户能使用的RAM只有128个,可存放读写的数据、运算的中间结果或用户定义的字形表。

程序存储器(ROM)共有4096个8位掩膜ROM,用于存放用户程序、原始数据或表格。

定时器/计数器是两个16位的可编程序定时器/计数器,以实现定时或计数产生中断用于控制程序转向。

并行输入输出(I/O)接口是4组8位I/O接口(P0、P1、P2或P3),用于外部数据的传输。

全双工串行接口有一个,用于与其他设备间的串行数据传送,该串行接口既可以用作异步通信收发器,也可以当同步移位器使用。

中断系统有两个外中断、两个定时器/计数器中断和一个串行中断,可满足不同的控制要求,并具有2级的优先级别选择。

时钟电路最高频率达12MHz,用于产生整个单片机运行的脉冲时序,但8051单片机要外置振荡电容。

以上各个部分通过片内8位数据总线DB(Data Bus)相连接。

需要特别指出的是,MCS-51系列单片机采用的是哈佛结构,程序存储器与数据存储器分开,而后续产品16位的MCS-96系列单片机则采用普林斯顿结构,程序存储器与数据存储器合二为一。

(2)引脚及功能

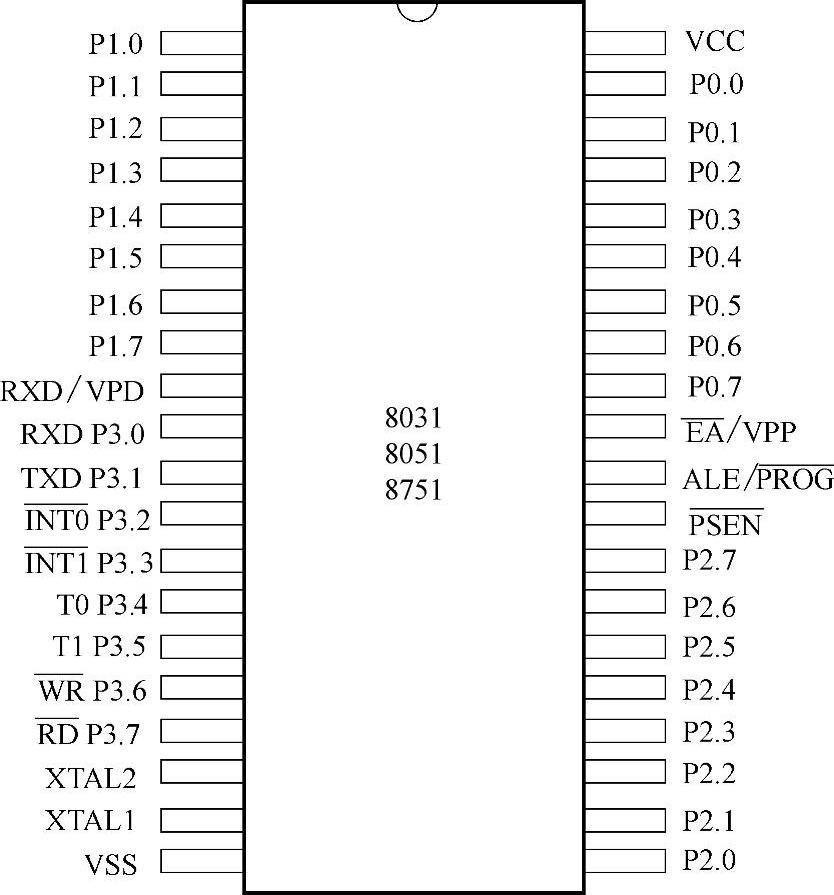

MCS-51系列单片机中各种芯片的引脚是互相兼容的,如8051、8751和8031均采用40脚双列直插封装(DIP)方式。当然,不同芯片之间的引脚功能也略有差异。8051单片机是高性能单片机,因为受到引脚数目的限制,所以有不少引脚具有第二功能,其中有些第二功能是8751芯片所专有的。MCS-51系列单片机引脚分布如图5-40所示。

各引脚功能简要说明如下。

1)电源及时钟电路引脚:

VCC(40脚)为电源端,VSS(20脚)为接地端。

XTAL1(19脚):接外部晶体和微调电容的一端。在芯片内它是振荡电路反相放大器的输入端。在采用外部时钟时,该引脚必须接地。

XTAL2(18脚):接外部晶体和微调电容的另一端。在8051芯片内它是振荡电路反相放大器的输出端,振荡电路的频率即晶体固有频率。若需采用外部时钟电路时,该引脚输入外部时钟脉冲。

图5-40 MCS-51单片机的引脚分布

2)控制信号引脚RST,ALE, 和

和 :

:

RST/VPD(9脚):RST是复位信号输入端,高电平有效。当此输入端保持两个机器周期的高电平时,就可以完成复位操作。RST引脚的第二功能是VPD,即备用电源的输入端。当主电源VCC发生故障,降低到低电平规定值以下时,将+5V电源自动接入RST端,为RAM提供备用电源,以保证存储在RAM中的信息不丢失,从而使复位后能继续正常运行。

(30脚):地址锁存允许信号端。当8051上电正常工作后,ALE引脚不断向外输出正脉冲信号,此频率为振荡器频率的1/6。CPU访问片外存储器时,ALE输出信号作为锁存低8位地址的控制信号。平时不访问片外存储器时,ALE端也以振荡频率的1/6固定输出正脉冲,因而ALE信号可以用作对外输出时钟或定时信号。此引脚的第二功能

(30脚):地址锁存允许信号端。当8051上电正常工作后,ALE引脚不断向外输出正脉冲信号,此频率为振荡器频率的1/6。CPU访问片外存储器时,ALE输出信号作为锁存低8位地址的控制信号。平时不访问片外存储器时,ALE端也以振荡频率的1/6固定输出正脉冲,因而ALE信号可以用作对外输出时钟或定时信号。此引脚的第二功能 在对片内带有4KBEPROM的8751编程写入时,作为编程脉冲输入端。

在对片内带有4KBEPROM的8751编程写入时,作为编程脉冲输入端。

(29脚):程序存储允许输出信号端。在访问片外程序存储器时,此端定时输出负脉冲,作为读取片外存储器的选通信号。

(29脚):程序存储允许输出信号端。在访问片外程序存储器时,此端定时输出负脉冲,作为读取片外存储器的选通信号。

(31脚):外部程序存储器地址允许输入端/固化编程电压输入端。当

(31脚):外部程序存储器地址允许输入端/固化编程电压输入端。当 引脚接高电平时,CPU只访问片内EPROM/ROM,并执行内部程序存储器中的指令,但当程序计数器的值超过OFFFH时,将自动转去执行外部程序存储器内的程序。当

引脚接高电平时,CPU只访问片内EPROM/ROM,并执行内部程序存储器中的指令,但当程序计数器的值超过OFFFH时,将自动转去执行外部程序存储器内的程序。当 引脚接低电平时,CPU只访问外部EPROM/ROM并执行外部程序存储器中的指令,不管是否有片内程序存储器。对于无片内ROM的8031或8032,需外接EPROM,此时必须将

引脚接低电平时,CPU只访问外部EPROM/ROM并执行外部程序存储器中的指令,不管是否有片内程序存储器。对于无片内ROM的8031或8032,需外接EPROM,此时必须将 引脚接地。

引脚接地。

3)I/O端口P0,P1,P2和P3:

P0(P0.0~P0.7):通道0,双向I/O端口。第二功能是在访问外部存储器时可分时用作低8位地址线和8位数据线,在编程和检验时(对8751)用于数据的输入和输出。

P1(P1.0~P1.7):通道1,双向I/O端口,在编程和检验时用于接收低位地址字节。

P2(P2.0~P2.7):通道2,双向I/O端口。第二功能是在访问外部存储器时,输出高8位地址,在编程和检验时,用于接收高位地址字节和控制信号。

P3(P3.0~P3.7):双向I/O端口,它除作为一般准双向I/O端口外,每个引脚还具有第二功能。

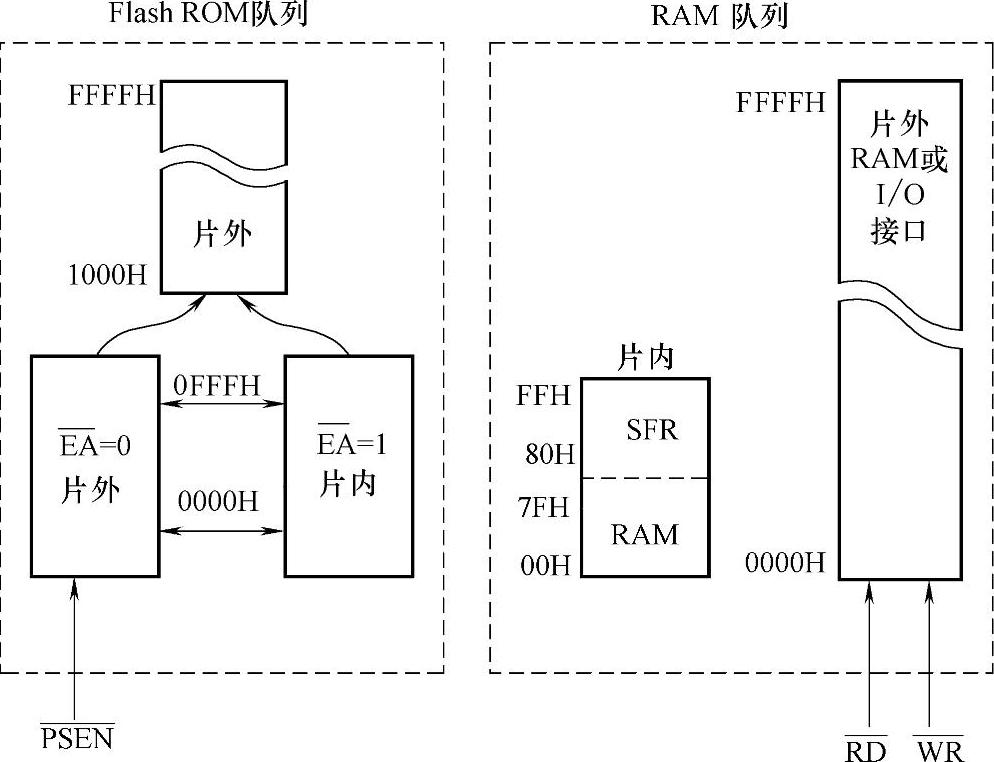

(3)存储器配置

8051片内有ROM(程序存储器,只读)和RAM(数据存储器,可读可写)两类,它们有各自独立的存储地址空间,与一般微型计算机的存储器配置方式不相同。

8051的存储器在物理结构上分为程序存储器空间和数据存储器空间,共有4个物理上相互独立的存储空间:片内程序存储器空间;片外程序存储器空间;片内数据存储器空间;片外数据存储器空间。这种程序存储器和数据存储器分开的结构形式,称为哈佛结构。但从用户使用角度来看,8051单片机存储器地址空间可以分为以下三类:

1)片内、片外统一编址0000H~FFFFH的64K程序存储器地址空间(16位地址,包括片内ROM和片外ROM)。

2)64K片外数据存储器地址空间,地址范围0000H~FFFFH。

3)256字节片内数据存储器地址空间(8位地址,包括128字节的片内RAM和特殊功能寄存器的地址空间)。8051存储器空间配置如图5-41所示。

①程序存储器地址空间。8051的程序存储器用于存放编好的程序和表格。8051芯片内具有4KB的ROM,8751芯片内具有4KB的EPROM,8031芯片内无程序存储器。MCS-51的片外最多能扩展64KB。片内、外的ROM是统一编址的,当 端保持高电平,8051的程序计数器PC在0000H~FFFFH地址范围内是执行片内ROM中的程序;当PC在1000H~FFFFH地址范围时,其自动执行片外程序存储器中的程序。当

端保持高电平,8051的程序计数器PC在0000H~FFFFH地址范围内是执行片内ROM中的程序;当PC在1000H~FFFFH地址范围时,其自动执行片外程序存储器中的程序。当 保持低电平时,只能寻址外部程序存储器,片外存储器可从0000H开始编址。

保持低电平时,只能寻址外部程序存储器,片外存储器可从0000H开始编址。

MCS-51的程序存储器中有7个单元具有特殊功能,其中0000H为MCS-51复位后PC的初始地址;0003H为外部中断0入口地址;000BH为定时器0溢出中断入口地址;0013H为外部中断1入口地址;001BH为定时器1溢出中断入口地址;0023H为串行口中断入口地址;002BH为定时器2溢出中断入口地址(8052所特有)。使用时通常在这些入口处都安放一条绝对跳转指令,使程序跳转到用户安排的中断程序起始地址,或者从0000H启动地址跳转到用户设计的初始程序入口处。

(https://www.xing528.com)

(https://www.xing528.com)

图5-41 8051存储器空间配置

②数据存储器地址空间。数据存储器用于存放运算中间结果、标志位、待调试的程序,以及用来暂存数据或缓冲等。数据存储器在物理上和逻辑上都分为两个地址空间:一个是片内256B的RAM;另一个是片外最大可扩充64KB的RAM。片外数据存储器与片内数据存储器空间的低地址部分(0000H~00FFH)是重叠的,8051有MOV和MOVX两种指令,用以区分片内、片外RAM空间。

片内数据存储区在物理上又可分为两个不同的区。

①00H~7FH单元:低128字节的片内RAM区,对其访问可采用直接寻址或间接寻址的方式。

在低128字节RAM中,00H~1FH共32个单元通常作为工作寄存器区,共分为4组,每组由8个单元组成通用寄存器,分别为R0~R7。每组寄存器均可选为CPU当前工作寄存器,通过PSW状态字中RS1、RS0的设置来改变CPU当前使用的工作寄存器。

②高128字节的RAM:特殊功能寄存器。

MCS-51中共有21个专用寄存器SFR,又称为特殊功能寄存器,这些寄存器离散地分布在片内RAM的高128字节中。

累加器ACC(EOH)是8051最常用、最繁忙的8位特殊功能寄存器,许多指令的操作数取自于ACC,许多运算的中间结果也存放于ACC。在指令系统中用A作为累加器ACC的助记符。

PSW是一个8位特殊功能寄存器,其各位包含了程序执行后的状态信息,供程序查询或判别用。

CY(PSW.7)是进位标志位。在执行加法(或减法)运算指令时,如果运算结果最高位(位7)向前有进位(或借位),CY位由硬件自动置1;如果运算结果最高位无进位(或借位),则CY清0。CY也是8051在进行位操作(布尔操作)时的位累加器,在指令中用C代替CY。

AC(PSW.6)是半进位标志位。当执行加法(或减法)操作时,如果运算结果(和或差)的低半字节(位3)向高半字节有半进位(或借位),则AC位将被硬件自动置1;否则AC位被自动清0。

F0(PSW.5)是用户标志位。用户可以根据自己的需要对F0位赋予一定的含义,由用户置位或复位,以作为软件标志。

RS0和RS1(PSW.3和PSW.4)是工作寄存器组选择控制位。这两位的值可决定选择哪一组工作寄存器为当前工作寄存器组。由用户用软件改变RS1和RS0值的组合,以切换选用的工作寄存器组。8051上电复位后,CPU自动选择第0组为当前工作寄存器组。

OV(PSW.2)是溢出标志位。当进行补码运算时,如有溢出,即当运算结果超出-128~+127的范围时,OV位由硬件自动置1;无溢出时,OV=0。

PSW.1为保留位。8051未用,8052作为F1用户标志位。

P(PSW.0)是奇偶校验标志位。每条指令执行完后,该位始终跟踪指示累加器A中1的个数。如结果A中有奇数个1,则P=1;否则P=0。常用于校验串行通信中的数据传送是否出错。

DPTR是一个16位的特殊功能寄存器,其高位字节寄存器用DPH表示(地址83H),低位字节寄存器用DPL表示(地址82H)。DPTR既可以作为一个16位寄存器来处理,也可以作为两个独立的8位寄存器DPH和DPL使用。

DPTR主要用以存放16位地址,以便对64KB片外RAM作间接寻址。

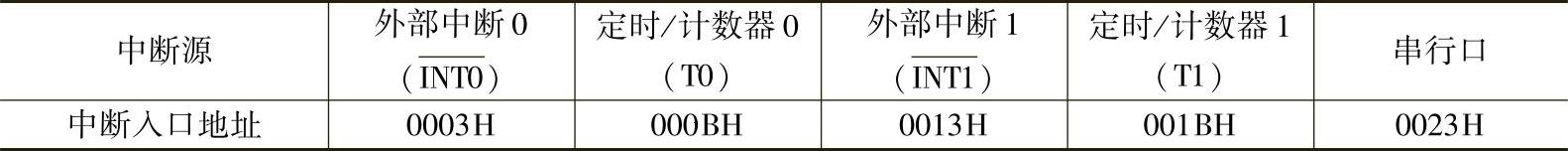

(4)中断技术

中断技术是计算机的一个重要技术,中断能力是衡量微型计算机能力的重要标志之一。51系列单片机的中断系统是8位单片机中功能较强的,可以提供5个中断源,具有两个中断优先级,可实现两级中断嵌套。

能发出中断请求信号的设备称为中断源,8051共有5个中断源,因此有5个中断入口地址,它是进入中断服务子程序的指路标。各中断源的中断入口地址是固定的,CPU响应任一中断源的中断请求后,PC的内容为该中断源的中断入口地址,5个中断源具体入口地址如表5-4所示。

表5-4 中断源具体入口地址

复位后各中断源属同一优先级——低优先级,在同一优先级中,5个中断源按上述自然优先级排列,其中INT0的自然优先级最高,串行口中断的最低。几个同一优先级的中断源同时申请中断时先响应自然优先级较高者。

(5)定时/计数功能及应用

51系列单片微机的定时/计数功能可以用作定时控制、延时及对外部计数脉冲进行计数。下面介绍8051定时/计数器的结构和工作原理。

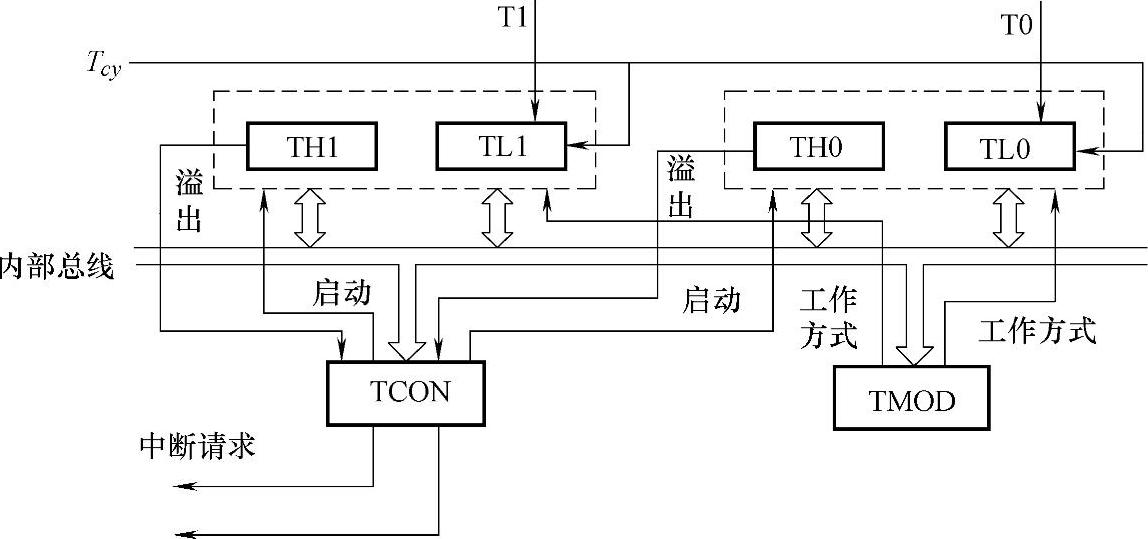

1)定时/计数器结构。8051单片机内有两个16位可编程定时/计数器。定时/计数器实质上就是一个加1计数器,其控制电路受软件控制、切换。16位的定时/计数器分别由两个8位专用寄存器组成,即:T0由TH0和TL0构成;T1由TH1和TL1构成。其访问地址依次为8AH~8DH,每个寄存器均可单独访问,这些寄存器是用于存放定时或计数初值的。此外,其内部还有一个8位的定时器方式寄存器TMOD和一个8位的定时控制寄存器TCON。这些寄存器之间是通过内部总线和控制逻辑电路连接起来的。TMOD主要是用于选定定时器的工作方式;TCON主要是用于控制定时器的启动和停止,此外TCON还可以保存T0、T1的溢出和中断标志。定时/计数器结构框图如图5-42所示。

图5-42 定时/计数器的结构框图

2)工作原理。

①计数脉冲提供方式:

a.置于计数方式时,计数脉冲从片外由P3.4(T0)或P3.5(T1)引入,下降沿触发计数器加1。

b.置于定时方式时,Ti由内部时钟频率定时,每一个机器周期使T0或T1加1计数。

②工作过程:Ti使用前先初始化编程,决定工作方式;再利用送数指令(MOV)将计数初值送入THi和TLi;之后用指令启动Ti开始计数。未计满数前溢出标志(TCON的TFi)为0。计满数溢出时,CPU自动将计数器清0,并自动将溢出标志TFi置1。

3)定时/计数器的控制。定时/计数器使用时要初始化编程,T0、T1使用前要用指令向TMOD写入工作方式字,向TCON写入命令字,向T0、T1写入计数初值。

①工作方式寄存器TMOD:用于设定工作方式(或称为模式)。

TMOD的高4位用来控制T1,低4位用来控制T0。以低4位为例说明如下。

GATE:启动计数方式控制位。GATE=0为软启动,即用指令SETBTR0即可使T0开始计数;GATE=1为硬启动,即除用指令SETBTR0外,还须置P3.2或P3.3管脚为高电平才能开始计数。

C/T:计数/定时方式控制位。C/T=0为定时方式;C/T=1为计数方式。

M1、M0:工作方式(模式)控制位。M1M0=00、01、10、11分别为工作方式0、1、2、3。各方式含义、特点及用途此处从略。

②控制及标志寄存器TCON:用于控制定时器的启、停、溢出标志以及外部中断触发方式。TCON可按位寻址。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。