在电子技术中定义共模抑制比为

![]()

式中 Ad——放大器对差动信号的放大倍数;

Ac——放大器对共模信号的放大倍数。

差动式放大器中,电路参数愈对称,则共模放大倍数愈小,共模抑制比愈高,电路参数愈不对称,共模抑制比愈小。

在设计测量放大电路时,除考虑参数尽量对称外,应了解串模噪声和共模噪声的来源,方可对症下药。

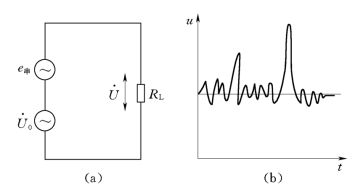

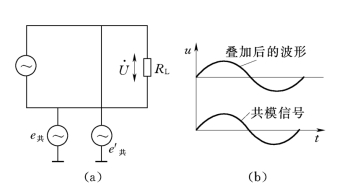

图12.1-3(a)串模信号e串的等效电路图,它是由接触电阻、电容和电感耦合干扰等产生,叠加在信号源上得图12.1-3(b)波形。图12.1-4(a)为共模信号e共的等效电路图,它是由信号源与接收回路之间产生的接地信号差所造成的。通常来源有:测量放大电路与其他电路共地,其他电路信号电流流过,因公共阻抗耦合,产生共模噪声;在公共地线上由于静电耦合和电磁耦合产生共模电压。共模信号与信号源叠加后的波形如图12.1-4(b)所示。

图12.1-3 串模信号的等效电路和波形图

(a)串模信号的等效电路图;(b)波形图

图12.1-4 共模信号的等效电路图和波形图

(a)共模信号的等效电路图;(b)波形图(https://www.xing528.com)

如果e共≠e′共,则共模信号转换成串模信号,在差分放大电路中,共模信号转换成差模信号才对电路产生影响。衡量一个电路的抗共模能力,可以用它抑制转化成串模信号的能力来表示。即

![]()

设计放大电路时,尽管注意了放大器外围器件的参数平衡和选择高CMRR的运算放大器。但是,实际差动放大器其正负两条信号通道上的阻抗参数不可能完全相等(或者说完全匹配),如电桥在测量时是不平衡的;运算放大电路在切换放大倍数时原参数匹配必然被改变;分布电容和导线等效电感的不平衡等等,都会使CMRR降低。

通常提高共模抑制比的方法有:

(1)正负两条信号通道上的元件特性和参数应尽可能一致。

(2)增大接地导线面积,缩短导线长,减小接地公共电阻。模拟电路和数字电路的接地要分开,需共地时,最好只有一个公共节点,减少一方电流在另一方电路中的流动。

(3)采用有效的屏蔽措施,减少电容耦合和电感耦合的干扰;采用隔离电源,减少50Hz的工频干扰。

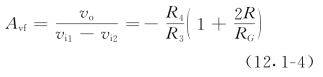

(4)采用三运放电路和集成仪表放大器。通常放大电路的前置级都是采用一个高输入阻抗放大器,尽管选择CMRR很高,但配置外围器件后,测量电路的CMRR并不一定高。采用图12.1-5所示三运放电路可以有效地提高CMRR和输入阻抗。其电压放大倍数为

图12.1-5 三运放电路

式中 改变RG就可以改变Avf值,且RG接在A1和A2的反向输入端之间,不改变电路的对称性。如果A1和A2对称,且各电阻值的匹配误差为±0.001%,则CM RR可达100dB以上。而对称的同相放大器,具有相同的输入电阻,其值可达到几百MΩ以上。

由于集成仪表放大器的前置放大电路都是精确匹配三运放形式,又集成了多路转换、增益控制、自稳零电路、滤波电路等,应该是设计电路时的理想选择。如AMP-02,AMP-03,AD365,APS24等。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。