RAM主要由存储矩阵、地址译码器和读/写控制电路3部分组成,其框图如图12.3.1所示。

图12.3.1 RAM的基本结构框图

1.地址译码器

地址译码器一般都分成行地址译码器和列地址译码器两部分。行地址译码器根据输入地址代码的A0~Ai使某一条行选线有效,列地址译码器根据输入地址代码的Ai+1~An-1使某一条列选线有效,由它们共同从存储矩阵中选定存储单元,使这些被选中的单元与读/写电路和I/O(输入/输出端)接通,以便对这些单元进行读/写操作。

2.读/写控制电路

读/写控制电路用于对电路的工作状态进行控制。![]() 称为片选信号。当

称为片选信号。当![]() 时,RAM工作;

时,RAM工作;![]() 时,所有I/O端均为高阻状态,不能对RAM进行读/写操作。

时,所有I/O端均为高阻状态,不能对RAM进行读/写操作。![]() 称为读/写控制信号。

称为读/写控制信号。![]() 时,执行读操作,将存储单元中的信息送到I/O端上;当

时,执行读操作,将存储单元中的信息送到I/O端上;当![]() 时,执行写操作,加到I/O端上的数据被写入存储单元中。

时,执行写操作,加到I/O端上的数据被写入存储单元中。

3.存储单元

存储矩阵由许多存储单元排列组成,RAM的存储单元分为静态和动态两种。

(1)静态存储单元。

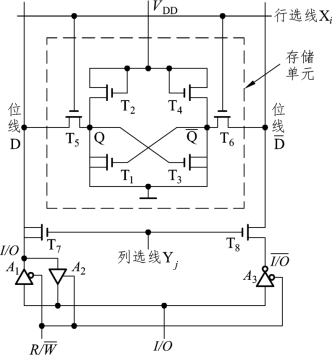

图12.3.2是8个NMOS组成的静态存储单元。其中,T1、T2构成的反相器与T3、T4构成的反相器交叉耦合组成基本RS触发器,可存储一位二进制信息。T5和T6是行选通管,受行选线Xi控制。当Xi为高电平时,T5和T6导通,RS触发器的输出Q和![]() 分别与位线D和

分别与位线D和![]() 相接。T7、T8是列选通管,受列选线Yj控制。当Yj为高电平时,T7和T8导通,位线D和

相接。T7、T8是列选通管,受列选线Yj控制。当Yj为高电平时,T7和T8导通,位线D和![]() 上分别和输入输出线I/O和

上分别和输入输出线I/O和![]() 相接。故当行地址译码器和列地址译码器选中该单元时,RS触发器的输出Q和

相接。故当行地址译码器和列地址译码器选中该单元时,RS触发器的输出Q和![]() 和输入输出线I/O和

和输入输出线I/O和![]() 相接。

相接。

进行读操作时,![]() ,所以三态门A1、A3为高阻状态,A2为工作状态,则RS触发器的输出Q被读到输入输出线I/O线上。(https://www.xing528.com)

,所以三态门A1、A3为高阻状态,A2为工作状态,则RS触发器的输出Q被读到输入输出线I/O线上。(https://www.xing528.com)

进行写操作时,![]() ,所以三态门A1、A3为工作状态,A2为高阻状态;将写入的信息加在I/O线上,经反相后

,所以三态门A1、A3为工作状态,A2为高阻状态;将写入的信息加在I/O线上,经反相后![]() 线上有其相反的信息,信息经T5、T6、T7和T8加到触发器的Q和

线上有其相反的信息,信息经T5、T6、T7和T8加到触发器的Q和![]() 端,从而使触发器触发,即信息被写入。

端,从而使触发器触发,即信息被写入。

图12.3.2 NMOS静态存储单元

由此可见,静态存储器中数据由触发器记忆,所以只要不断电,数据就能永远保存。但是由于一个存储单元要8个管子,所以静态存储器功耗较大,集成度不高。

(2)动态存储单元。

动态RAM的存储矩阵由动态MOS存储单元组成。动态MOS存储单元有单管、三管和四管等几种结构形式。

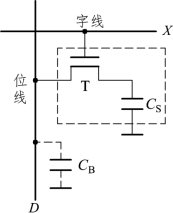

图12.3.3所示为单管动态MOS存储单元的电路结构图。存储单元由一个NMOS管T和一个电容CS组成,它是利用电容CS来存储信息,电容上存有电荷时作为1状态,没有电荷时作为0状态。

在进行写操作时,字线给出高电平,使T管导通,位线上的数据便经过T被存入电容CS中。

在进行读操作时,字线同样给出高电平,使T管导通。这时电容CS经T管向位线上的电容CB提供电荷,使位线获得读出的信号电平。

单管动态MOS存储单元电路是所有存储单元中电路结构最简单的一种。但由于电容SC的容量很小,而漏电流又不可能绝对等于0,所以电荷保存的时间有限。为了避免存储信息的丢失,必须定时地给电容补充电荷。通常把这种操作称为“刷新”或“再生”,因此动态RAM内部要有刷新控制电路,其操作也比静态RAM复杂。尽管如此,由于动态RAM存储单元的结构能做得非常简单,所用元件少,功耗低,所以目前已成为大容量RAM的主流产品。

图12.3.3 单管动态MOS存储单元

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。