寄存器是计算机和其他数字系统中用来存储代码或数据的逻辑部件。集成寄存器产品种类也较大,按输入输出方式分,有串行输入串行输出、并行输入串行输出、串行输入并行输出、并行输入并行输出4种;按移位方向分为单向(左移、右移)和双向移位寄存器;按寄存器状态字长分为4位、8位等;按输入输出顺序分为先入先出、先入后出等。

1.集成寄存器功能介绍

(1)8位寄存器74HCT374。

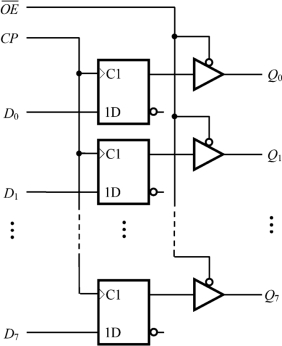

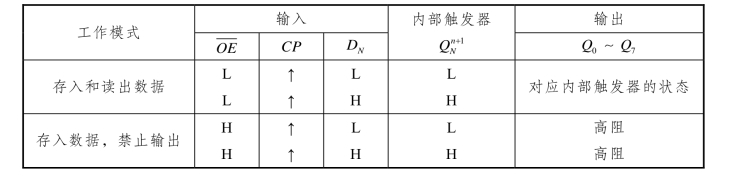

由8个D触发器构成的8位寄存器74HCT374的逻辑图如图11.5.1所示。图中,D0~D7为8位数据输入端,在CP脉冲上升沿作用下,D0~D7端的数据同时存入相应触发器。当输出使能控制信号![]() 时,触发器存储的数据通过三态门输出端Q0~Q7并行输出。74HCT374的功能表如表11.5.1所示。

时,触发器存储的数据通过三态门输出端Q0~Q7并行输出。74HCT374的功能表如表11.5.1所示。

图11.5.1 74HCT374的逻辑图

表11.5.1 74HCT374的功能表

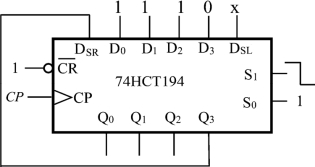

(2)双向移位寄存器74HCT194。

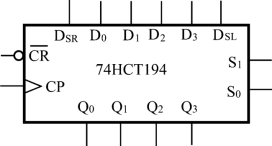

双向移位寄存器74HCT194的逻辑符号如图11.5.2所示,其中![]() 为清零输入端,CP为时钟脉冲输入端,S1、S0为工作状态控制输入端,D0~D3为并行数据输入端,DSR右移串行数据输入端,DSL左移串行数据输入端,Q0~Q3为并行数据输出端。

为清零输入端,CP为时钟脉冲输入端,S1、S0为工作状态控制输入端,D0~D3为并行数据输入端,DSR右移串行数据输入端,DSL左移串行数据输入端,Q0~Q3为并行数据输出端。

图11.5.2 74HCT194的逻辑符号

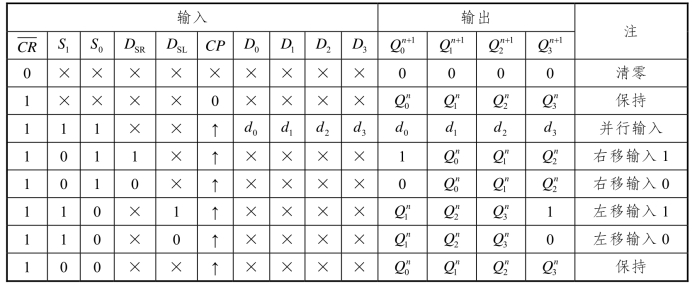

74HCT194的功能表如表11.5.2所示。由表可知,74HCT194有以下功能:

① 清零功能:当![]() 时,双向移位寄存器异步清零。(https://www.xing528.com)

时,双向移位寄存器异步清零。(https://www.xing528.com)

② 保持功能:当![]() ,CP=0或S1=S0=0时,双向移位寄存器保持状态不变。

,CP=0或S1=S0=0时,双向移位寄存器保持状态不变。

③ 并行送数功能:当![]() ,S1=S0=1,CP=↑时,将加在D0~D3的数码送入寄存器Q0~Q3中。

,S1=S0=1,CP=↑时,将加在D0~D3的数码送入寄存器Q0~Q3中。

④ 右移串行送数功能:当![]() ,S1=0=S0=1,CP=↑时,将DSR的值移至Q0端,Q0原来的值移至Q1端,Q1原来的值移至Q2端,Q2原来的值移至Q3端。

,S1=0=S0=1,CP=↑时,将DSR的值移至Q0端,Q0原来的值移至Q1端,Q1原来的值移至Q2端,Q2原来的值移至Q3端。

⑤ 左移串行送数功能:当![]() ,S1=1=S0=0,CP=↑时,将DSL的值移至Q3端,Q3原来的值移至Q2端,Q2原来的值移至Q1端,Q1原来的值移至Q0端。

,S1=1=S0=0,CP=↑时,将DSL的值移至Q3端,Q3原来的值移至Q2端,Q2原来的值移至Q1端,Q1原来的值移至Q0端。

表11.5.2 74HCT194的功能表

2.寄存器的应用

寄存器的应用很广,在运算电路中可以用移位寄存器和加法器共同完成乘法、除法等运算功能;在通信电路中可以用移位寄存器将串行码转换成并行码,或将并行码转换成串行码;此外,还可以用移位寄存器构成移位寄存器型计数器和顺序码脉冲发生器等电路。

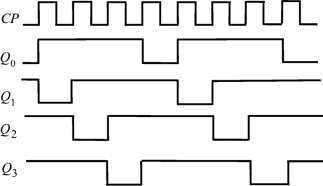

例11.5.1 分析图11.5.3所示电路的逻辑功能。

图11.5.3 例11.5.1的逻辑图

解:开始工作时,S1=1,S0=1,74HCT194的功能为并行送数,所以电路的初始状态为Q0Q1Q2Q3=D0D1D2D3=1110。接下来,S1=0,S0=1,74HCT194的功能为右移串行送数,由于DSR=Q3,所以,Q0原来的值移至Q1端,Q1原来的值移至Q2端,Q2原来的值移至Q3端,DSR(即Q3原来的值)的值移至Q0端。所以CP端输入第一个上升沿后,输出Q0Q1Q2Q3=0111;第二个上升沿后,输出Q0Q1Q2Q3=0011;第三个上升沿后,输出Q0Q1Q2Q3=1101;第四个上升沿后,输出Q0Q1Q2Q3=1110,以此循环工作。由此可作出该电路的时序图,如图11.5.4所示。由该图可知,该电路的特点是输出端上的状态按一定时间、一定顺序轮流输出0,所以该电路称为环形计数器(或脉冲配器)。

图11.5.4 例11.5.1的时序图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。