从前面的分析可以看出,软件无线电思想的一个重要特点就是将A/D采样过程尽量靠近射频模拟前端。为了减少模拟环境,实现一次混频的结构,就需要在较高的中频对信号进行数字化,这就要求A/D器件具有较高的工作带宽和较高的采样频率。同时为了减小模拟前端的增益压力,还要求A/D有较低的分层电平和较大的动态范围。UOSDR中A/D相关的参数选择原则是:

(1)A/D采样率的选择:A/D采样率的选择对于整个系统的参数设计十分重要。由采用一次混频、高中频带通采样的接收机结构可知,经过一次混频相干解调后回波信号为一个固定中频的窄带信号,为此信号进行中频带通采样可以大大降低系统对A/D采样率的要求。A/D的采样选择一般遵循以下原则:

①根据带通采样定理,采样率至少为信号带宽的两倍;

②由3.2.11节的分析可知,要想获得较高的信噪比,就需要通过适当提高系统采样率来实现;

③A/D采样的速率过高的话,会在进行中频数字处理时为了满足整个系统高速并行运行而消耗过多的FPGA硬件资源,最终使设计在一个FPGA中无法实现;

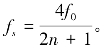

④要满足式(4-9)的要求: (https://www.xing528.com)

(https://www.xing528.com)

(2)A/D模拟输入带宽的选择,也就是A/D器件的模拟输入带宽至少要大于模拟中频信号的最大带宽。

(3)A/D最小分层电平的选择,即A/D分辨率的选择。A/D器件的分辨率越高,所需的输入信号幅度越小,则对模拟前端总增益量的要求就越小,同时使得接收机的三阶节点可以做得更高。A/D的分辨率选择一般主要取决于系统要求的动态范围。对于UOSDR系统,我们将接收机的动态范围定位70dB,则根据3.2.11节的分析可知,只有当A/D位数达到14位时才能满足要求。

综合上面的各种原因,UOSDR系统选用了ADI公司的AD9245模数转换芯片,其分辨率达到14位,而最高采样速率可达120MSPS,模拟差分输入带宽为500MHz,完全可以满足系统要求。

(4)A/D输出接口的选择:XC3S2000是个高速并行的逻辑,而AD9245的数据接口为14位并行接口,数据为二进制补码格式,这些都为后续FPGA编程带来了方便。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。