【摘要】:在现代雷达数字接收系统中,正交数字中频处理器已经成为不可缺少的重要组成部分。这里的中频处理器又叫数字下变频。我们在根据FPGA硬件特性,将CORDIC算法引入DDC设计中,可以看到它不仅可以快速地完成数字正交检波,而且无须混频,即省去了生成I/Q两路数据的两个乘法器,从而大大降低了ROM资源的使用。

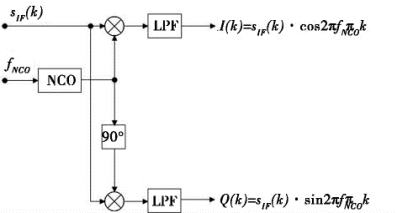

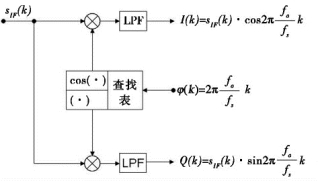

在现代雷达数字接收系统中,正交数字中频处理器已经成为不可缺少的重要组成部分。这里的中频处理器又叫数字下变频(DDC)。DDC由数字混频器(Mixer)、数字本振(NCO)和低通滤波器(LPF)三部分构成,如图4-18所示。而NCO通常是基于查找表的DDS方式实现的,通过输入的相位数据来寻址查找表输出相应的正弦波幅值,如图4-19所示,然后与乘法器相乘而得到正交检波数据。经过低通抽取滤波器得到I/Q基带数据。

图4-18 数字下变频原理框图(https://www.xing528.com)

图4-19 基于LUT的数字下变频实现

为了满足高精度(n位)的要求,采用LUT结构的数字下变频器相应的就需要耗费大量的ROM资源(2n×n位)。我们在根据FPGA硬件特性,将CORDIC算法(Coordinate Rotation Digital Computer)引入DDC设计中,可以看到它不仅可以快速地完成数字正交检波,而且无须混频,即省去了生成I/Q两路数据的两个乘法器,从而大大降低了ROM资源的使用。同时也避免了使用多相滤波法时,I/Q数据的相差半个采样点的问题。这样多通道雷达接收系统的数字部分只需A/D和FPGA就可以完成,大大简化了系统硬件结构,使系统小型化便携式成为可能。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。