【摘要】:根据分析Xilinx公司Spartan-3系列FPGA中Block RAM的结构特点,我们可以设计合理的FIFO深度与数据位宽,节省系统资源。图3-29异步FIFO的顶层框图FIFO的设计要服务于A/D数据采集部分和USB传输部分。数据采集的流程如下:首先由USB发送系统复位信号srst清空FIFO,empty变为有效。当CY7C68013A发出rd_en后,FIFO根据clk时钟将数据放到dout总线上去,并将valid置为有效。UOSDR系统中使用的4096字的FIFO外部接口如图3-30所示。图3-30UOSDR的FIFO外部接口

根据分析Xilinx公司Spartan-3系列FPGA中Block RAM的结构特点,我们可以设计合理的FIFO深度与数据位宽,节省系统资源。Spartan-3系列XC3S2000芯片含有40个独立的块RAM,每个块RAM大小为18kbits,当没有奇偶位(数据位宽8位以下)时,块大小为16384bits,最大数据宽度为36bits。

Xilinx ISE提供IP CORE方式生成FIFO,它支持最大数据位宽256bits和最大存储深度64k个数据,可以选择块RAM或分布式RAM来实现。FIFO的顶层框图如图3-29所示。

图3-29 异步FIFO的顶层框图(https://www.xing528.com)

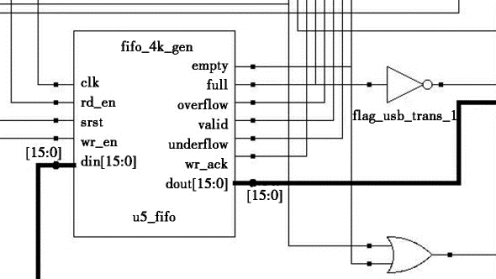

FIFO的设计要服务于A/D数据采集部分和USB传输部分。数据采集的流程如下:首先由USB发送系统复位信号srst清空FIFO,empty变为有效。在wr_en(或rd_en)的使能下,FIFO按照clk的速率,写入din总线上来自A/D(DDC)或FFT的数据,对应的每次成功写操作wr_ack都会变为有效。当数据达到4096个字时,full变为有效,经过反相器输出给CY7C68013A的传输中断,等待CY7C68013A的读动作。当CY7C68013A发出rd_en后,FIFO根据clk时钟将数据放到dout总线上去,并将valid置为有效。UOSDR系统中使用的4096字的FIFO外部接口如图3-30所示。

图3-30 UOSDR的FIFO外部接口

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。