这里的频率综合器模块设计主要包括时钟源和信号源设计。在现有条件下,主要有两种方案。

(1)DDS激励PLL方案

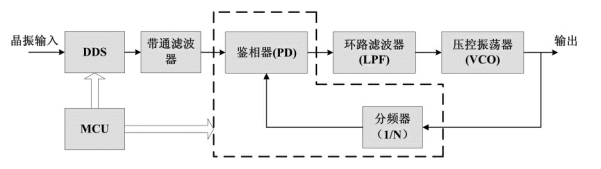

DDS的工作原理决定了它具有输出频率低、杂散较多的缺点,而PLL输出频率高,对杂散的抑制性能良好,所以采用结合PLL环路对DDS信号实现倍频调和跟踪滤波的技术,可以实现对频谱纯度和输出频率都要求较高的频率合成。通常采用的有内插式和倍频式两种方案,前者在设计上比较复杂,往往在设计中采用倍频的方式实现。用DDS的输出作为PLL的参考频率源输入,使得输出有较高的频率分辨率,而PLL作为一个可编程的倍频器,将DDS产生的信号倍频调到所需的频率范围。基本原理框图如图3-17所示。

图3-17 DDS激励PLL方案原理框图

这种结构可利用高的鉴相频率来提高PLL的切换速度,利用DDS的高分辨率来保证足够小的频率步进,同时PLL的带通特性还可以很好地抑制DDS输出频谱中的部分杂散。该方案实现了DDS和PLL的优势互补,兼顾了各个方面的性能,所以用此方案实现的频率源可以做到很高的频率、较快的频率切换速度、高的频率分辨率,同时也能很好地保证系统杂散和相位噪声性能。当环路达到锁定状态时,频率合成器的输出频率和频率分辨率分别为:

式中N为锁相环的分频比,K为DDS的频率控制字。

在该方案中系统的跳频过渡时间由PLL决定,环路滤波器的带宽是一个重要的参量,要想获得比较短的跳频过渡时间,环路带宽必须足够宽。相反,要想获得好的杂散指标,环路带宽必须足够窄。因此如何兼顾这些指标是系统设计时必须考虑的问题。(https://www.xing528.com)

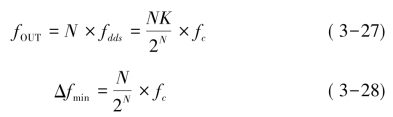

(2)PLL激励DDS方案

根据DDS的固有特点,其最大输出频率只能达到系统时钟的40%,可知,采用这种方案产生UHF频段的线性调频信号,必须有一款系统时钟足够高的DDS芯片。如图3-18所示,采用一块MCU来控制DDS和PLL,PLL通过倍频给DDS提供较高的参考时钟,使DDS能够方便的输出各频段的线性调频信号。由于DDS的工作机理,其杂散水平较差,虽然通过后级的带通滤波器能取出一部分,但信号质量仍然和第一种方案有较大差距。

图3-18 PLL激励DDS方案原理框图

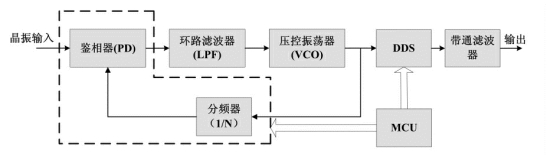

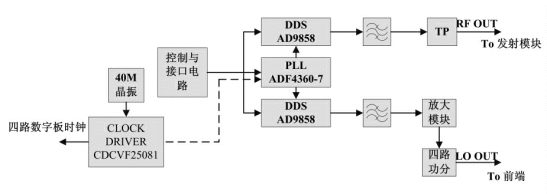

虽然采用第一种方案可以获得更好的信号质量,但是设计不够灵活,要产生不同频段的信号,必须更换外置起振电感,调试起来不太方便。所以,我们的UOSDR雷达最终选择的是PLL激励DDS的实现方案。如图3-19所示为UOSDR频率合成器硬件的结构框图。

图3-19 频率合成器硬件结构框图

为了保证雷达系统的同步性,频率合成器与数字板采用同样的时钟,将80MHz系统时钟晶振放在频综板上,经过时钟驱动芯片分五路,最多可以提供给四块数字板,一路作为锁相环的参考时钟,锁相环将80M的晶振倍频到960M,输出为差分信号,经过功分器分别分为两路,一路差分信号作为射频DDS芯片的系统时钟,一路作为本振DDS芯片的系统时钟。本振和射频采用相同的DDS芯片,可以保证系统的相干性,同时,当存在短期频率抖动的情况下,采用两片相同的芯片产生的线性调频信号也可以产生较为稳定的中频信号,完全可以满足高频地波雷达检测海洋回波相位的要求。射频DDS的输出先经过滤波器,然后经过开关输出;本振DDS的输出先经过滤波器后再经过放大模块,最后经过功分器分四路最多可提供给四块模拟前端板使用。放大模块的作用是保证本振电平达到模拟前端中的混频器所需的标准,具体增益可以根据实际情况调整。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。