2.6.2.1 天线系统及收发通道设计

对于天线系统而言,因为我们采用的是双基地雷达系统,所以收发天线是分置的。在收发端我们采用可以相互替换的Yagi八木天线。因为天线水平极化时,传播的信号在贴近地面时会在大地表面产生极化电流,极化电流因受大地阻抗影响产生热能而使电场信号迅速衰减,而垂直极化方式则不易产生极化电流,从而避免了能量的大幅衰减,所以实测中采用垂直极化的方式(测移动目标时,需要采用水平极化方式)。为了提高天线的增益和抗干扰能力,我们努力降低天线的旁瓣和后瓣电平。为了提高天线的收发效率,我们也要尽可能地提高天线的工作频带,使其易与接收机相匹配。天线系统的设计指标如表2-1所示。

表2-1 功放模块和天线系统设计指标

相比于探海雷达的大功率发射机,UOSDR系统无须很大的发射功率,发射功率仅需5W左右。在这里我们选用小信号功放模块和场效应管来实现我们的发射模块,构成我们的发射通道。通过信号源设计,产生300~315MHz的线性调频信号,其幅度约为-10dBm,因为我们的发射功率为37dBm(5W),所以我们的发射通道增益需大于47dB。单纯的小信号功放模块或者场效应管无法同时实现这种增益和输出功率要求,所以采用先通过小信号功放作为驱动级,然后场效应管作为最后的输出放大。结合信号发生器的实际情况,并且根据我们的实际需要,最终设计的功放指标如表2-1所示。

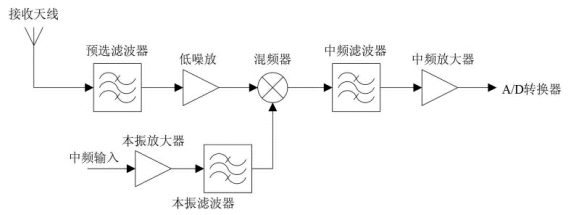

在高频雷达中,机外噪声和干扰远大于机内噪声,所以高频雷达的接收机以抗外部干扰为主要目标。而在UOSDR雷达接收机中,以降低机内噪声为主要目标,同时也要兼顾雷达接收机的灵敏度和好的选频特性。所以,在接收机设计中,首先要考虑的是接收机的形式。由于发射频率和本振频率很高而不好产生,所以为了降低我们的设计难度,我们选用一次混频,低中频采样的方案。中频的选取应考虑各种组合频率的干扰,实际中的中频信号为90MHz,也可以较好地抑制镜频干扰。接收机的工作框图如图2-7所示。

图2-7 UOSDR系统接收机框图

在UOSDR接收机中,混频前需要加低噪声放大器(LNA),因为混频器的噪声系数一般都比较大,而前端的滤波器一般为无源滤波器,有一定的损耗,如无LNA,则整个系统的噪声系数将很大。而在变频前引入具有一定增益的LNA,则可以减弱混频器和后面基带放大器的噪声对整机的影响,从而对提高灵敏度有利。但是LNA的增益不宜太高,因为混频器是非线性器件,进入它的信号太大,会产生很多的非线性失真。所以,LNA的增益一般不超过15dB。带通滤波器用来选择工作频带,可以放在LNA之前或之后。放在后面对降低系统噪声有利,放在前面可以对进入LNA的信号进行预选,滤除了很多带外信号,也就减少了由于LNA的非线性引起的各种互调失真干扰。

2.6.2.2 时钟源、PLL和频率综合器模块(https://www.xing528.com)

在UOSDR系统中采用80MHz的普通有源晶振作为整个系统的时钟源。虽然普通晶振的长期稳定度不高,但晶振的短期稳定度对系统来说更为重要。根据UOSDR系统的工作体制和实际的工作情况来看,这种廉价的时钟源能够基本满足要求。

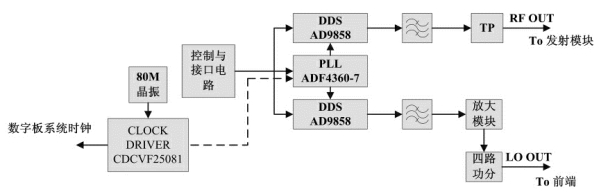

UOSDR系统采用ADI公司的两片AD9858 DDS芯片来进行UHF线性调频射频和本振信号设计。根据这款DDS芯片的频率有效范围为输入参考时钟的40%,则要参数300~350MHz的线性调频信号,必须给DDS信号提高750~875MHz的参考时钟。这里采用了ADI公司的ADF4360-7来产生960MHz,以此满足系统对时钟的要求。图2-8是UOSDR系统时钟源和信号源的结构框图。

图2-8 UOSDR系统的信号源和时钟源的结构框图

2.6.2.3 同步控制器设计

因为UOSDR雷达系统是一个全相参的脉冲多普勒雷达,保证整个收发通道相干工作就是同步控制器的首要任务。为了能让雷达全系统同步工作,同部控制器向雷达的各个分系统提供各种稳定、可靠的同步信号和状态信号等,所有系统所需时钟信号之间必须保证严格的时序关系,只有这样才能使雷达正常工作。各通道间通过同步控制器来协同工作,利用FPGA来实现雷达同步控制器在整机联试过程中时间关系的局部调整,实现实时可编程,缩短同步控制器的研制周期。

2.6.2.4 数据采集及数据处理系统模块

UOSDR雷达系统采用的是FMCW体制,利用回波信号的频率和相位信息来提取河流参数。当回波信号和接收机本振信号混频产生高中频信号,数据采集处理系统采集此信号并进行两次傅立叶变换,就可得到各个距离元上回波信号的频率和相位信息。在UOSDR雷达系统设计中,我们的数据采集系统是用ADC+FPGA+USB来实现的。

90MHz低中频40MHz带通采样之后的数据,存储在经过FPGA实现数字前端,产生I、Q两路数据,然后再进行数字抽取,得到低速率数据,再进行FFT实现第一次FFT的解距离过程,处理的数据在FPGA内部的FIFO中缓存,然后FPGA启动USB传输请求,将数据传入PC主机端存盘,并进行后续数据处理。

在试验中,我们将两次FFT都放在PC主机端进行,这样虽然增大了每个通道数据存储FIFO所占容量,但是在样机的前期调试中,可以减少综合工具的综合时间,而且可以得到最原始的数据,在出现问题的时候更容易定位问题。实际中,因为我们的采样率为40MHz,每个扫频周期为0.02s,数据位数为16位,在经过数字下变频抽取后,数据率降到了16kword/s,用USB2.0完全可以满足原始波形的实时传输。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。