【摘要】:并联谐振电路主要是指电感线圈与电容并联的谐振电路,如图5-2a所示。)6.并联谐振电路的特点谐振时,端电压与总电流同相。电感线圈与电容并联谐振电路适用于电源内阻RS和负载电阻RL较大的电路。

并联谐振电路主要是指电感线圈与电容并联的谐振电路,如图5-2a所示。

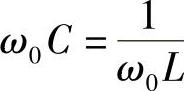

1.谐振条件

①

②

或者:在Q 1条件下,

1条件下,

图5-2 电感线圈与电容并联谐振电路

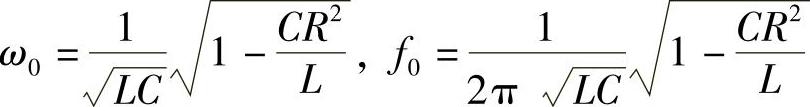

2.谐振频率

在Q 1条件下,

1条件下, ,

,

3.谐振阻抗

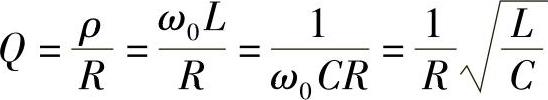

4.特性阻抗

5.品质因素

(电路的Q值就是电感线圈的Q值。)

(电路的Q值就是电感线圈的Q值。)

6.并联谐振电路的特点(https://www.xing528.com)

(1)谐振时,端电压与总电流同相。

(2)在Q 1条件下,谐振阻抗为最大值。若用电流源激励,则电路端电压为最大值。

1条件下,谐振阻抗为最大值。若用电流源激励,则电路端电压为最大值。

(3)谐振时,电感支路电流与电容支路电流近似相等,相位相反,且为外施电流 的Q倍,如图5-2b所示。

的Q倍,如图5-2b所示。

(4)若用电压源激励,谐振时,总电流最小。

7.并联谐振电路的频率特性

ω=ω0时,电路呈纯阻性;ω<ω0时,电路呈感性, 越前

越前 ;ω>ω0时,电路呈容性,

;ω>ω0时,电路呈容性, 滞后

滞后 。

。

电感线圈的直流电阻R越小,Q值越高,谐振曲线越尖锐。

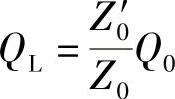

8.电源内阻RS和负载电阻RL对Q值的影响

等效谐振阻抗Z0′=RS∥RL∥Z0,使有载Q值下降。

电感线圈与电容并联谐振电路适用于电源内阻RS和负载电阻RL较大的电路。

9.复杂并联电路谐振条件

回路中各储能元件电抗值代数和为零。

10.部分接入法

将电源或负载接入双电感并联电路电感线圈中心抽头或接入双电容并联电路电容中心点的连接方法称为部分接入法。

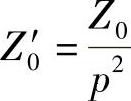

部分接入法具有阻抗变换功能, (p为接入系数),可减小电源内阻RS和负载电阻RL对谐振回路Q值的影响。

(p为接入系数),可减小电源内阻RS和负载电阻RL对谐振回路Q值的影响。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。