(1)PLC810PG是将有源功率因数校正器[APFC,以下简称为功率因数校正器(PFC)]和半桥LLC谐振变换器集成在一个芯片中,可大大简化外围电路设计。PFC控制器内部包含乘法器,校正后的功率因数可达0.92~0.99,电源效率可高于85%。

(2)它属于一种变频转换器,当工作频率升高时输出电压降低,工作频率降低时输出电压升高。因此,通过改变工作频率即可调节输出电压,实现稳压的目的。

(3)PFC的频率和相位与LLC严格保持同步,不仅能降低PFC输出电容中的纹波电流,还减小了电磁干扰。

(4)在额定负载条件下,所设计的PLC810PG的LLC典型工作频率f=100kHz,实际工作频率f′则随输入电压和负载而变化,调节范围是f′=(0.5~3)f=50~300kHz。

(5)PLC810PG中的PFC工作在连续导电模式(CCM)。半桥式LLC控制器采用零电压开关(ZVS)技术,使MOSFET在零电压时通、断,不仅减小了冲击电流,还降低了开关损耗,使电源效率得到显著提高。

(6)可通过电阻来设定LLC的最高工作频率,并可精确设定零电压开关(ZVS)变换器的死区时间,以减小MOSFET的损耗。(https://www.xing528.com)

(7)内部有比较完善的保护电路,包括软启动电路,欠电压、开路及过电压保护电路,LLC故障检测电路。

(8)PLC810PG适合构成32~60in[1]的大屏幕液晶电视机电源、150~600W高效率隔离式开关电源及大功率LED驱动电源。

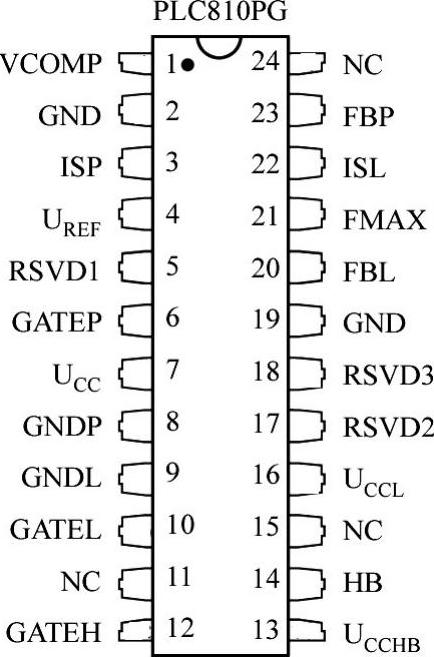

图1-1 PLC810PG的引脚排列

PLC810PG采用PDIP-24封装,引脚排列如图1-1所示。各引脚的功能如下:UCC、UCCL、UCCHB分别为弱信号模拟电路的电源端、LLC低压端驱动器的电源端和LLC高压端驱动器的电源端。UCC端接待机电源。在UCCL、UCCHB端与半桥引脚HB之间,应分别并联一只1μF的陶瓷退耦电容。GND为公共地。GNDP为PFC栅极驱动信号的返回端,GNDL为LLC低压端栅极驱动器的返回端,这三端应直接连印制电路板的GND。HB为半桥端,接至由两只MOSFET组成的半桥中点。ISP为PFC电感的电流检测端,ISL为LLC的高频变压器一次绕组电流检测端。GATEP为用来驱动PFC的MOSFET端。GATEH、GATEL分别为用于驱动LLC高端和低端的N沟道MOSFET功率管端。UREF为LLC反馈电路的基准电压端。FBP为PFC的反馈端,接PFC的取样电阻。FBL为LLC的反馈端,接LLC的取样电阻。LLC的工作频率f与反馈电流IFB成正比。VCOMP为内部PFC控制器乘法器的输入端,外接反馈环路的相位校正网络。在FMAX端与UREF端之间接设定电阻,用来设定LLC的最高工作频率fmax。RSVD1端应与UREF端连接,RSVD2、RSVD3端需接GND。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。