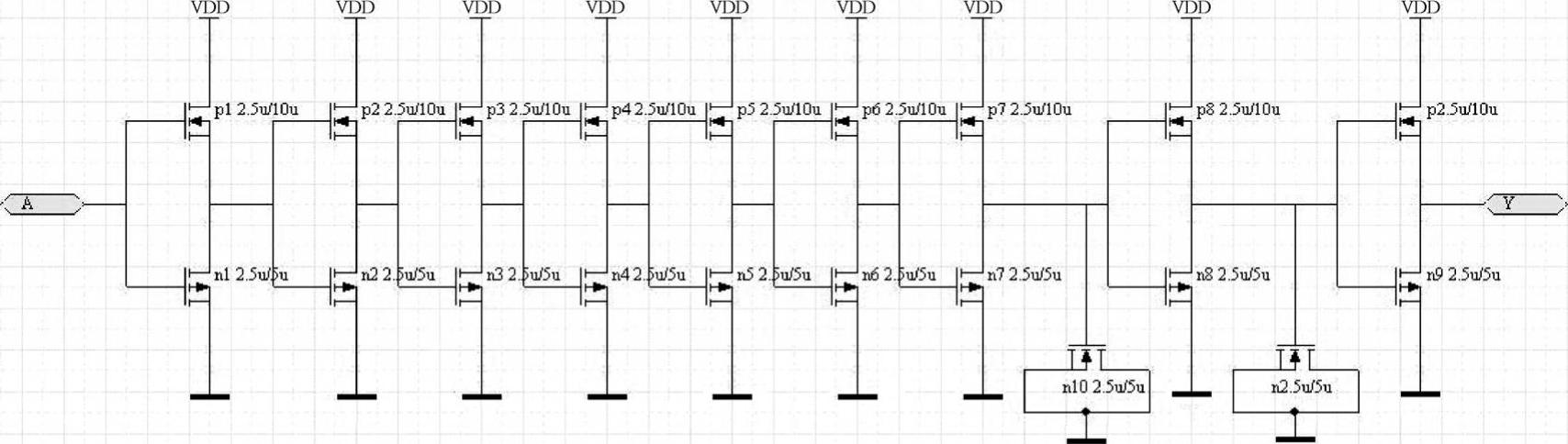

在D508项目数字部分的控制信号产生模块、延时产生模块和输出控制模块中都用到了一个延时单元,该延时单元由9个反相器和两个电容构成,输出反相。每个反相器中的MOS管都是倒比结构,目的是用于产生延时信号。每个反相器将产生10ns左右的延迟,9个将产生100ns左右的延迟。另外还利用电容的充放电特性来产生延时。延时单元逻辑结构如图5-6所示。

图5-6 延时单元逻辑结构图

在延时单元的版图设计过程中需要考虑一些寄生效应的影响,主要包括寄生电阻和寄生电容。

在版图中,多晶硅、有源区和金属走线都会产生寄生电阻,而这些寄生的电阻会使电压产生漂移,导致额外噪声的产生。设计时为尽量减小寄生电阻的影响,采用以下原则:减小多晶硅、有源区的长距离走线,尽量采用金属走线,因为相对来说金属层的单位电阻较小;另外,可以增加走线宽度。寄生电容同寄生电阻一样,在芯片中走线会不可避免的产生。寄生的电容耦合会使信号之间互相干扰。降低寄生电容影响的措施有:避免时钟线和信号线的重叠;两条信号线应该避免长距离平行,而信号线之间交叉对彼此的影响比两者平行要小;输入信号线和输出信号线应该避免交叉;对于易受干扰的信号线,在两侧加地线保护;模拟电路的数字部分需要严格隔离开。

当然金属走线也不是越宽越好,因为可能会导致天线效应。(https://www.xing528.com)

所谓天线效应是指长金属线(面积较大的金属线)在集成电路加工过程中会吸引大量的电荷(因为刻蚀金属工艺中是在强电场中进行的),如果该金属直接与MOS管栅极相连,可能会在栅极形成高电压,从而导致栅极氧化层击穿。因此在深亚微米CMOS工艺通常限制了这种几何图形的总面积,从而将栅极氧化层被破坏的可能性降低。如果必须要使用大面积的几个图形,可以用另外更高一层的金属割断本层的大面积金属的方法来解决。正是基于这个原因,一些加工线提供的规则命令文件中就专门针对铝层等的面积进行检查,超出一定的值就会报错,从而避免产生天线效应。

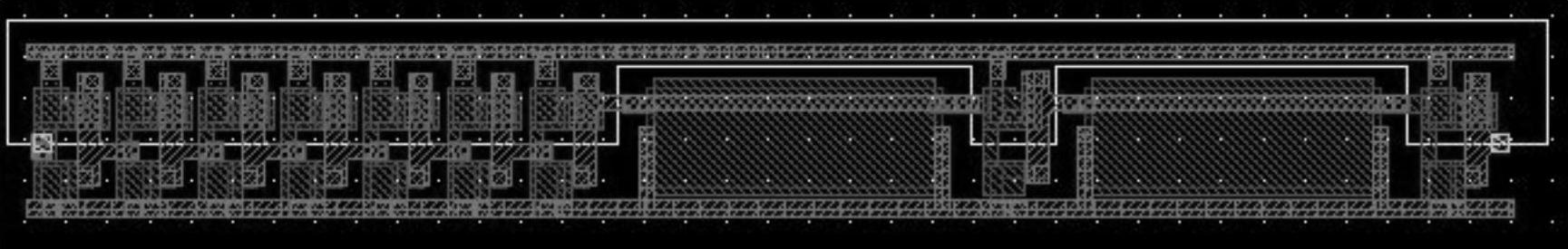

在图5-6所示的延时单元中,9个反相器要尽可能放置在一起,避免它们之间长距离的走线,从而可能导致延时时间的不确定性。因此在版图中把该单元做成一个标准单元(命名为z_inv9)形式参与自动布局布线,其高度跟其他标准单元一致,该延时单元最初的版图如图5-7所示。

图5-7 延时单元最初的版图

在布局布线之前,需要把在D508项目数字部分的控制信号产生模块、延时产生模块和输出控制模块中的9个反相器和两个电容构成的延时单元用一个标准单元z_inv9进行逻辑上的替换,从而保证布局布线工具可以使用图5-7所示的标准单元版图进行布局布线。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。