1.共用N阱原则

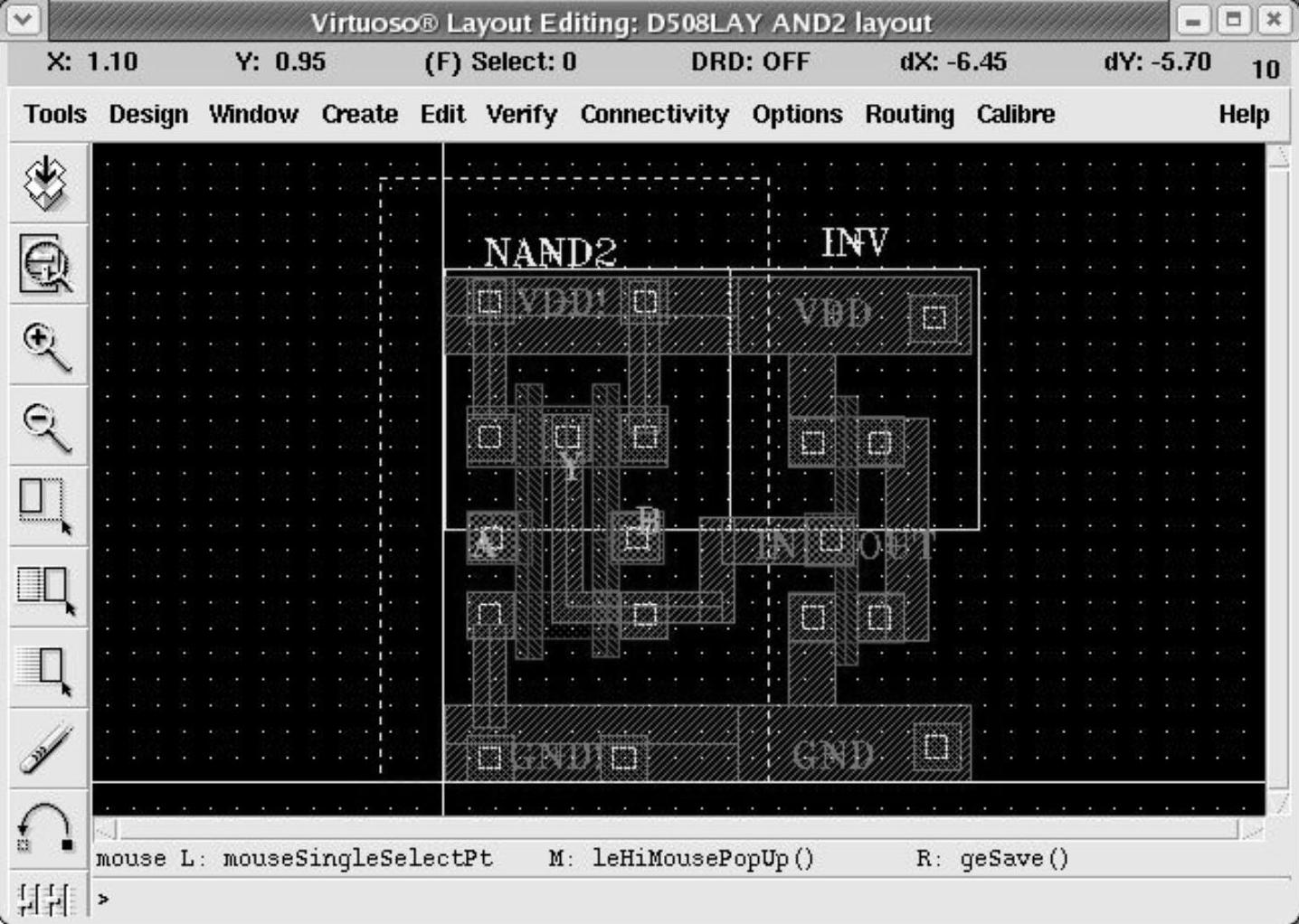

在表2-1中D508项目的设计规则中有一条是关于N阱间距的规则,大小为4.8μm,因此当一个标准单元和另一个标准单元紧挨在一起放置时,就需要考虑这个阱间距的规则,见图4-9的NAND2和INV两个单元上的N阱。

由于一个具体的设计中有很多种标准单元,如果每一个标准单元跟它左、右两边的单元都需要考虑这条规则,那么就会浪费大量芯片面积。

以上问题解决的方法是共用N阱,因为大部分数字电路中的PMOS器件和N阱一起都是连接到VDD上的,可以设计一个大的单个的N阱来节省空间,共用N阱缩小单元间距如图4-11所示。

在图4-11中,NAND2和INV两个单元共用了一个N阱,这两个单元之间就不需要考虑阱间距这个规则了,从而可以使得这两个单元可以靠得很紧。

在图4-11中,只是考虑了NAND2和INV两个单元,当数字模块中所有的单元都进行这样的考虑后,芯片面积的利用效率就大大提高了。

当不同的单元共用一个N阱时,那么原来的单元之间的阱间距规则就变成了单元之间的其他规则,如有源区间距规则、铝间距规则,通常这些规则都要比N阱的间距规则小得多,因此通过共用N阱可以使单元靠得更近些,从而节省芯片面积。

图4-11 共用N阱缩小单元间距

2.单元间隔原则

上面提到把相邻的单元紧挨一起放置,不需要另外连线就可以把电源、地线和N阱等相互对接起来,从而形成一长条标准单元的单元行。但是这样做有可能出现的问题是相邻单元内部的器件也会对接起来,从而造成这些器件不满足设计规则,但另一方面为了节省芯片面积,又不能使标准单元内部的器件距离该单元的边界太远,因此在标准单元建立的时候必须要考虑单元间隔原则。

目前普遍采用的单元间隔原则有两种,一种称为一半网格间隔原则,即让标准单元内部所有的连线都处于网格上,并且使相互对接单元的边沿落在网格线的中间,即处于半个网格的位置上,这样就能保证铝层相互之间正好能保持所需要的最小间距。由于单元可以在各个方向上进行对接,所以每个标准单元的上、下、左、右的每一边都应当落在半个网格位置上。另外一种称为一半设计规则间隔原则,即保证两个对接单元之间的某一条设计规则,如有源区间距或者铝层间距等在距离单元边界至少有一半的该设计规则的最小间距。以D508项目为例,设计规则规定两条铝线的间距是1.2μm,那么保证每个单元内部的铝线距离每个单元的边界为0.6μm,即最小间距的一半,那么两个单元放在一起时就能保证1.2μm的铝间距。如图4-8中网格距单元边界为0.6μm,因此只要保证单元内部的铝线保持跟网格齐边,就能保证两个单元对接的时候铝线之间有1.2μm的距离。

实际建立标准单元的时候并不是都能够满足上面提到的两种间隔原则的,如有时会发现该单元比半个网格还略宽一些,无法满足一半设计规则原则。在这种情况下,就需要把单元放大一个网格(比如某个单元宽度比3个pitch单元宽一点,但不到4个pitch宽度,这就必须用4个pitch单元作为该单元的宽度),让每一边都宽松一些,这样会造成面积上的一些浪费,这也是建立标准单元库必须要付出的代价。

3.布线通道原则

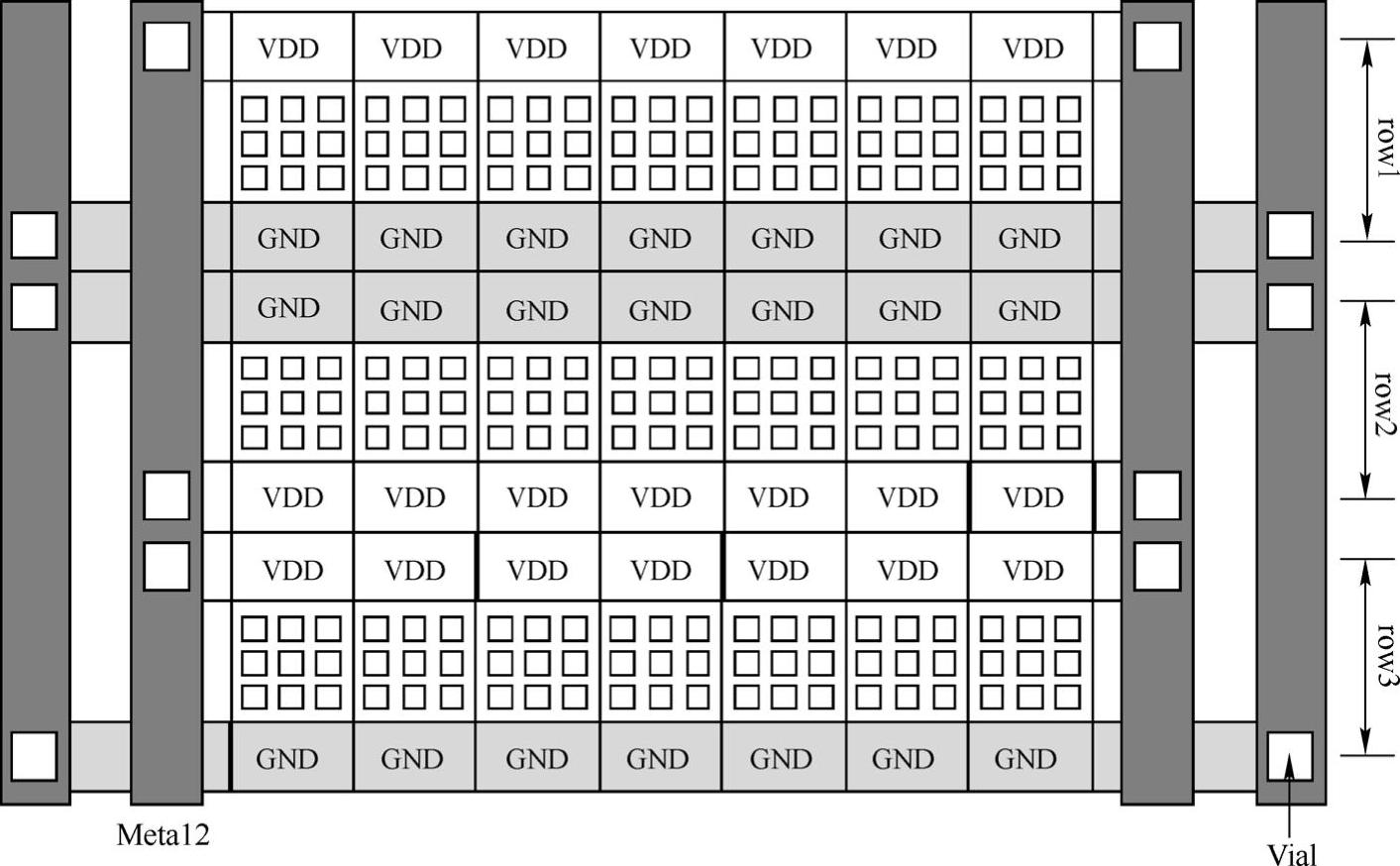

图4-12是一个两层铝布线的例子。

图4-12 两层铝布线的例子

在图4-12中,在每一个标准单元中都是VDD在上、GND在下;第一条标准单元行(row1)VDD在上、GND在下;但第二条标准单元行(row2)VDD在下、GND在上,即进行了上下翻转动作,目的是为了使GND跟第一条的GND可以紧挨在一起,共用一根地线;同样的第三条标准单元行(row3)VDD在上、GND在下,和第二条共用一根电源线;用二铝线把电源线、地线交错连接在一起,即VDD和GND分别在单元行的末端相互连接起来,这种方式通常称为“背靠背”布线。

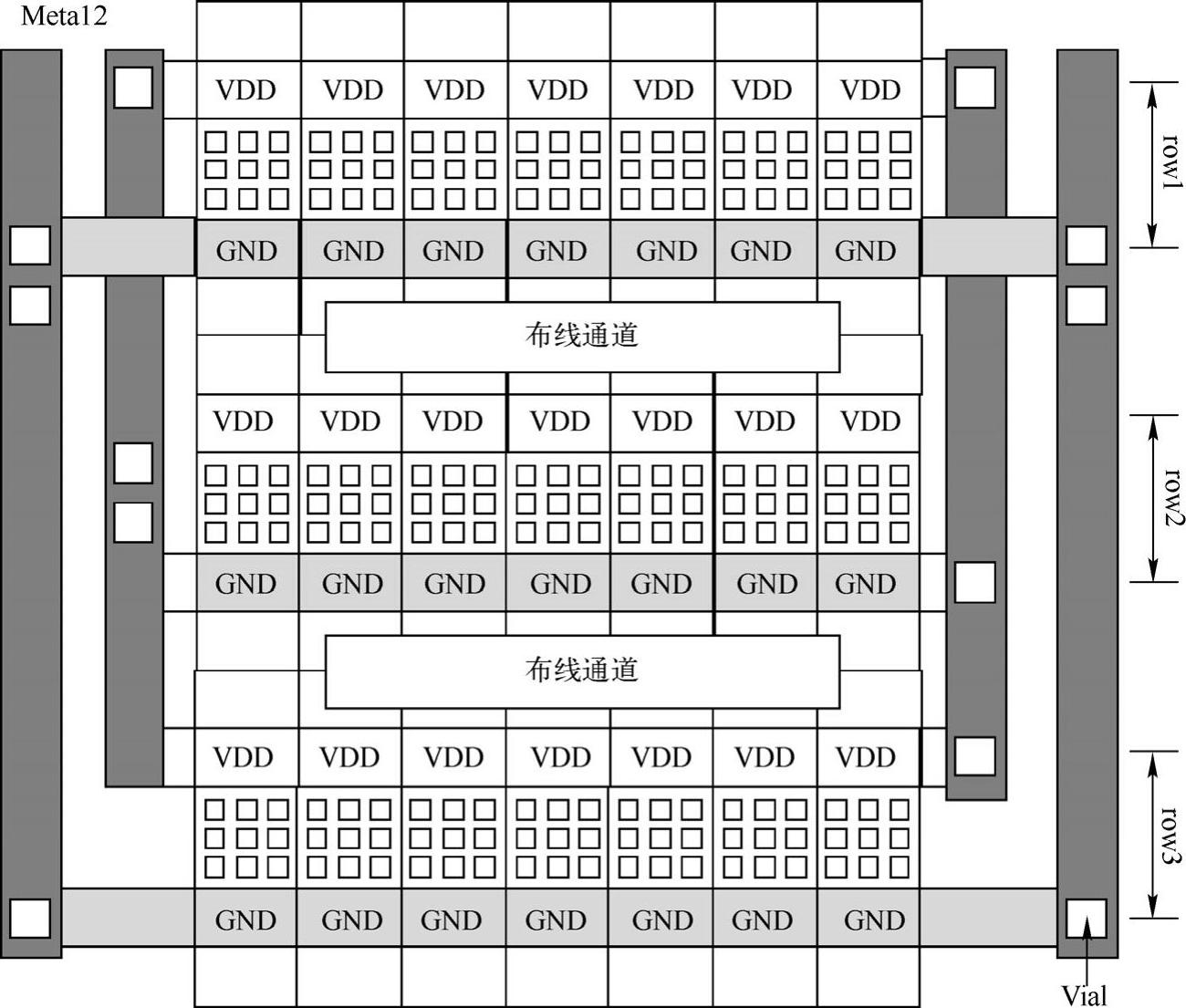

以上这种布线方式有时会遇到一些问题,比如对于有些触发器单元,由于建该单元时前、后两级的R端和S端没有在标准单元内部连接,需要在标准单元之外进行相连;另外还有可能有其他信号线的走线,但如果触发器内部没有空间可以进行走线。这时需要考虑标准单元库的布线通道原则,即在标准单元的上、下各留出一些空隙,也就是所谓的布线通道,如图4-13所示,以便以后在这些通道内进行其他走线。

把图4-13所示的预留了布线通道的标准单元排列成行和列,如图4-14所示,这样在标准单元的上、下各形成了一个长长的空间,等待进行某些铝层布线。另外有了这个布线通道,第二条单元行不再需要像图4-12中那样进行隔行翻转,因为电源和地线都已经被布线通道隔开了,即有了单元之间的这些通道,就可以让标准单元保持VDD在上和GND在下的原样。

图4-13 标准单元内预留布线通道

图4-14 预留了布线通道的标准单元排列成行和列

4.标准单元内端口的引出原则(https://www.xing528.com)

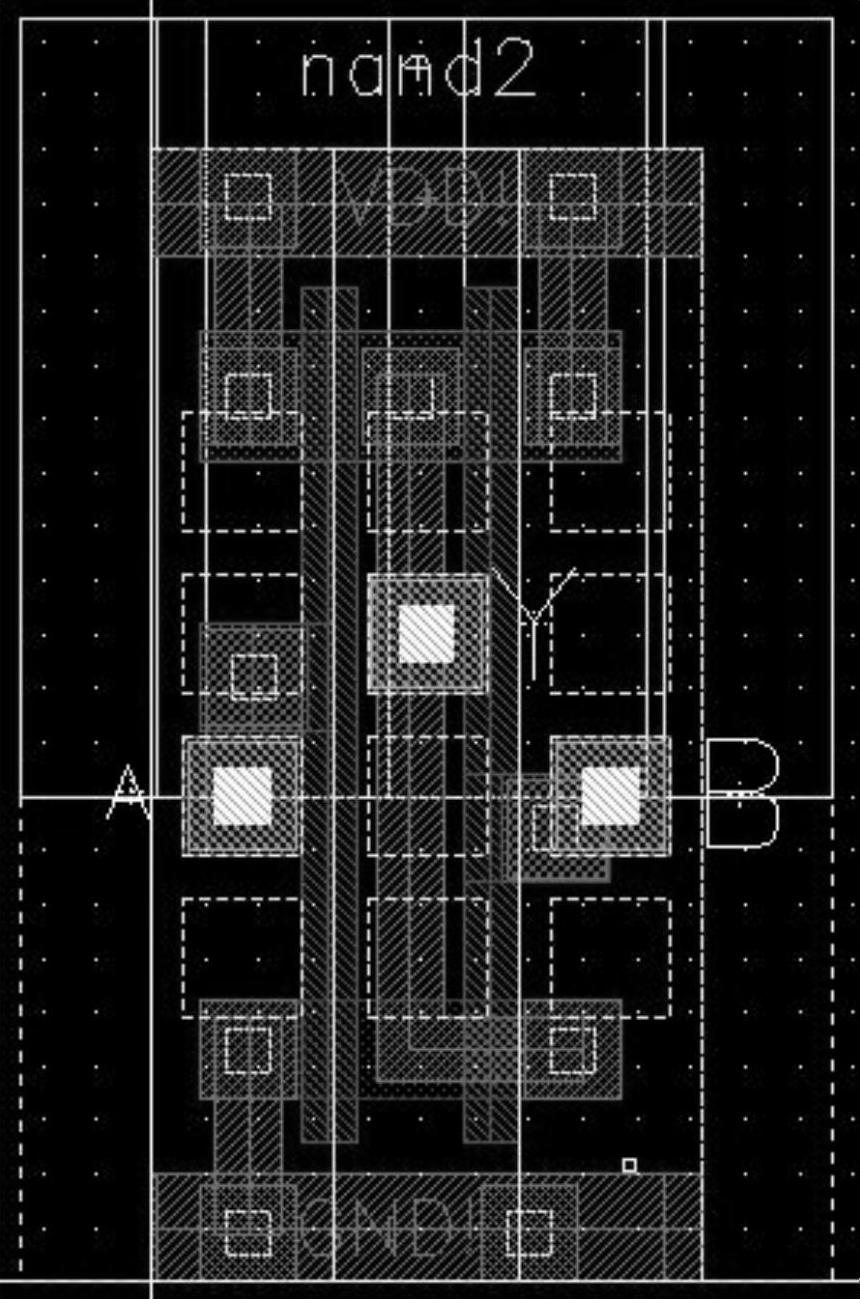

标准单元内的所有端口(pin)都需要引出,引出的方法有多种。图4-15示意的是通过通孔(via)引出的方法,图中白色的孔是通孔。

图4-15 通过通孔引出pin的方法

这种方法主要存在以下缺点:

1)会降低布线时优化走线的自由度。

2)会造成布线时逻辑上悬空的输出pin占用布线通道,如有些触发器的Q、QN端悬空。

3)会导致部分走线变得多余(如两个靠近单元边界的pin输入、输出相连时可直接用一铝走线连起来,如果一定要通过via引出,那就需要增加两个via)。

为了克服以上缺点,对于像D508那样采用两层布线的项目,通常都用二铝来引出。

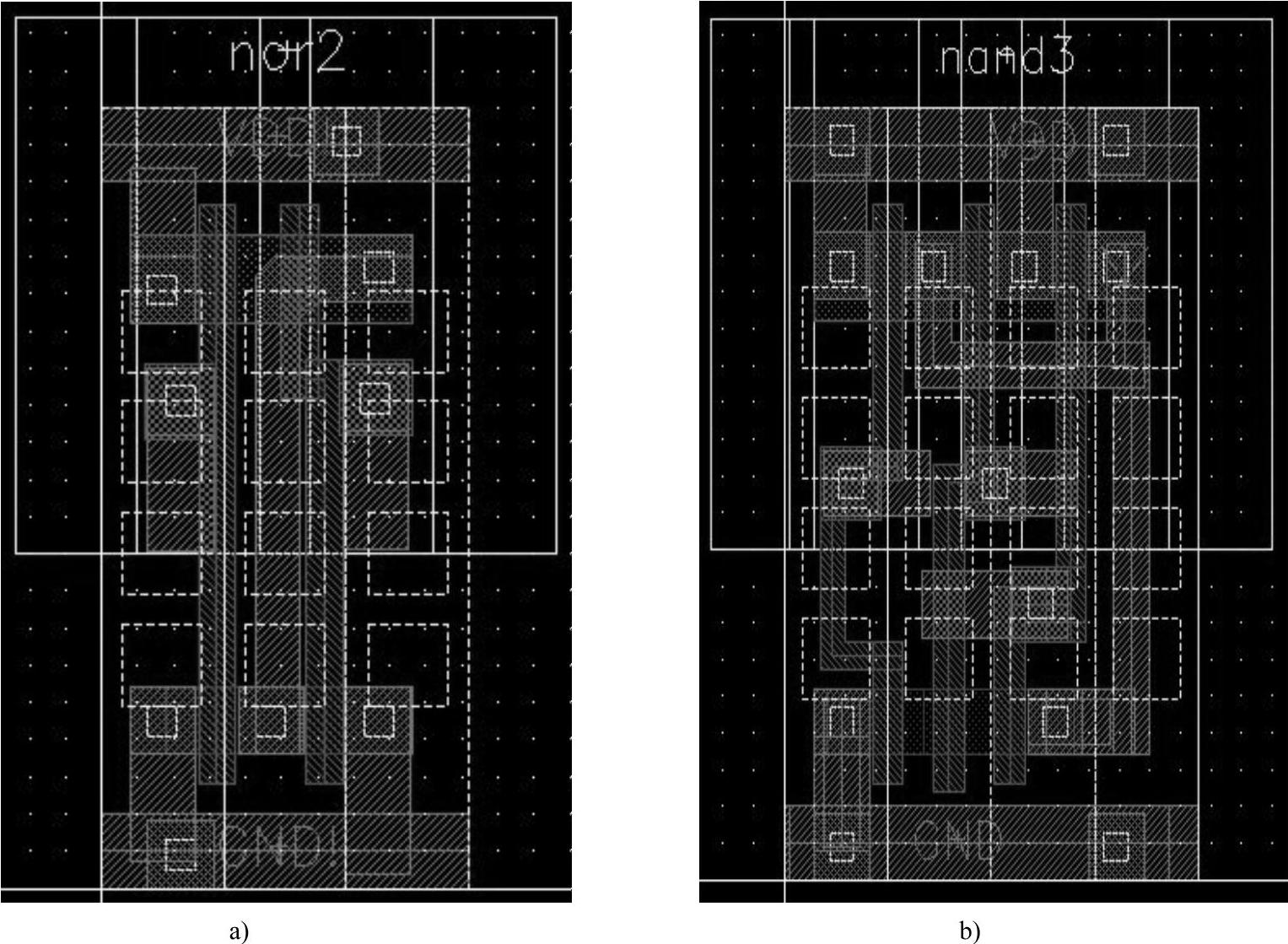

通过二铝引出也首先要基于比较合适的一铝引出端。一铝及接触孔的引出有两种不同的情况,分别如图4-16a、b所示。可以看到为了给输入、输出端口留出足够的空间放置接触孔,在建标准单元时总是把PMOS管和NMOS管均向电源线和地线两边靠,中间留出的空间给各个端口加接触孔。通常会给每一个端口保留两个布线孔的余量。

图4-16a是给端口留的布线余量在Y方向上,图4-16b是给端口留的布线余量在X方向上。

图4-16 不同方向留布线余量

a)Y方向留布线余量 b)X方向留布线余量

以上两种方法中哪一种布线性能更优越呢?在建标准单元时端口信息首先是从一铝开始引出的,然后在布线时产生via1,并通过二铝引出端口,而二铝走线的方向主要是在Y方向上,因此如图4-16a那样在Y方向上给via1留了余量,但实际利用率是不高的。而如图4-16b那样在X方向上留一定余量,这样对于某个节点可以在Y方向上引出位置有两个可选的地方,因此相比较而言应该把余量留在X方向上。

以上都是理想的情况,实际设计过程中会遇到一些比较特殊的情况,这时端口的引出就必须依据具体情况来定,比如对于一些内部走线较多的标准单元,没有足够的空间保留两个余量,那么对该pin的处理需要具体考虑。假如该pin靠近标准单元边界,那么可以采用一铝直接引出的方法;如果该pin处于单元的内部,则可以直接用via1引出。对于某些端口,如触发器的R端,由于受到单元高度的限制,两个R端内部不能直接相连,可以采用上面所说的每个端口单独引出,而在布线时在单元外布线通道自动连接的方法。对于此类在单元外连接单元内的端口的情况通常也不会产生类似时序匹配等的其他副作用,因为EDA工具在进行布线时总是会遵循就近原则,不会出现两个紧挨的连在一起的端口走了很大一圈的线再相连的情况。

另外在多层布线中,还要灵活地考虑端口的引出,因为有效布线资源越多,布线效率越高。比如在三层布线设计中,二铝先垂直走线,一铝和三铝先水平走线,因此二铝是约束最紧的层。由于这种情况垂直布线资源相对水平布线资源要少,所以尽量利用垂直走线资源。在标准单元设计中,必须使约束最紧的层布线资源最大化,具体来说,就是将垂直方向的端口交错开,这样可以提高布线的灵活性。

5.标准单元内衬底接触孔放置原则

一般每个标准单元内都要有衬底接触孔,否则在布线完成后还需要人工进行添加,会增加版图工作量。对电路性能要求较高的标准单元其衬底接触往往是一整条的。

因为标准单元的高度都是固定的,当遇到单元内MOS管宽长比比较大的情况时,可能无法添加一整条衬底接触,为了保证每个单元中有衬底接触,在建该单元时要遵循以下原则:在该单元边界的上、下、左、右两边保证各有半个衬底接触,这样在布线时两个单元放置在一起会形成一个完整的衬底接触。实际设计时是把一个完整的衬底接触孔放在单元内,只不过单元边界包该衬底接触孔为一半。

以上这种办法是针对标准单元内实在没有空的地方放置衬底接触,如果有,要尽量保证衬底接触不超出单元的边界,以便于布局布线工具的使用。

6.单元边界设计原则

上面多次提到标准单元建立时必须要设计单元边界。通常标准单元是以该单元的电源线和地线为边界的。EDA工具在布线时单元是按单元的边界依次排放的,而非图形的边界。

在图4-12所示的两层“背靠背”布线的例子中,如果不采用布线通道,那么在建单元时如果单元内电源线或地线的宽度为2μm,则单元边界的画法不能把铝完全包在里面,而应该包一半的电源线或地线宽度。如果采用单元边界全部包电源线或地线,则布线时会出现电源线或者地线为4μm的情况。

D508项目设计中,单元边界采用boundi这一层来画,如图4-8所示。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。