【摘要】:D508项目中涉及上、下拉电路的设计。上、下拉电路主要是针对电路中当输入信号悬空时,为使电路有一个稳定的输出而在电路中增加的一种结构,其中,上拉电路的输出恒为1,下拉电路的输出恒为0。下拉电路由下拉电阻和两级反相器构成,其结构如图3-13所示。所谓衬底噪声是指源、漏与衬底PN结正偏导通,使得衬底电位产生抖动偏差。在图3-14、图3-15所示的上、下拉版图结构中充分考虑了这一点。

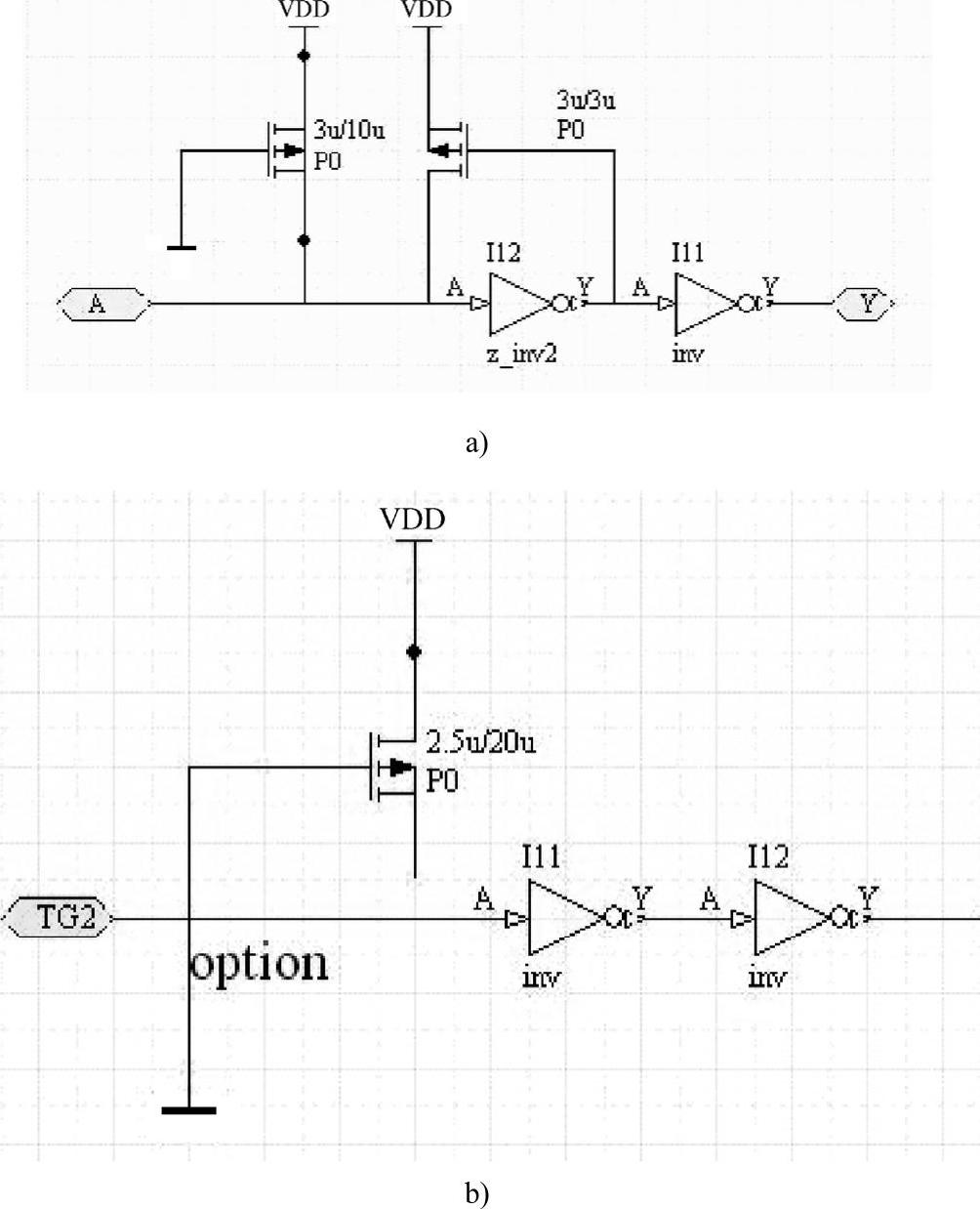

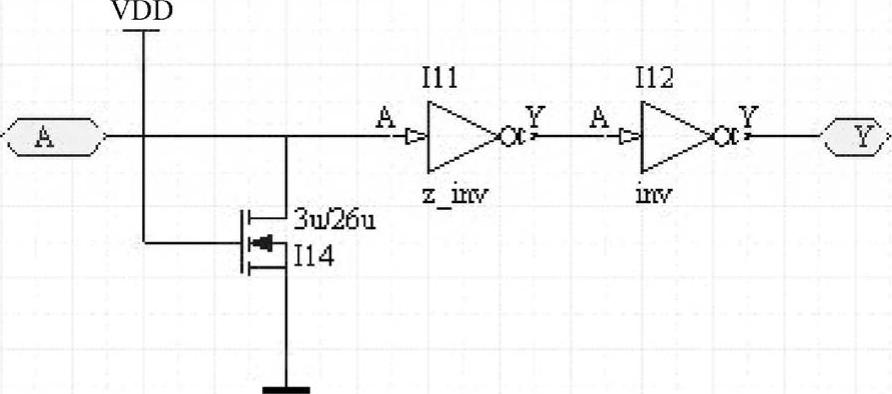

D508项目中涉及上、下拉电路的设计。上、下拉电路主要是针对电路中当输入信号悬空时,为使电路有一个稳定的输出而在电路中增加的一种结构,其中,上拉电路的输出恒为1,下拉电路的输出恒为0。D508项目中的上拉电路有两种形式,一种是一个上拉的PMOS管作为上拉电阻,然后另外一个PMOS管和一个反相器作为输入锁存,再另外加一个反相器组成,其结构如图3-12a所示;另一种形式是由上拉电阻(P型倒比管)和两级反相器构成,如图3-12b所示,其中作为上拉电阻的PMOS倒比管是一个可选项,即其漏极端可以连接到输入端,从而具有上拉功能;也可以悬空,使输入端不具备上拉功能,而这一选择的修改是可以通过改一块掩膜版(如二铝层)来实现的,这就是下一章中要详细讲述的掩膜选项。下拉电路由下拉电阻(N型倒比管)和两级反相器构成,其结构如图3-13所示。

图3-12 上拉电路结构图

a)上拉电路结构一 b)上拉电路结构二

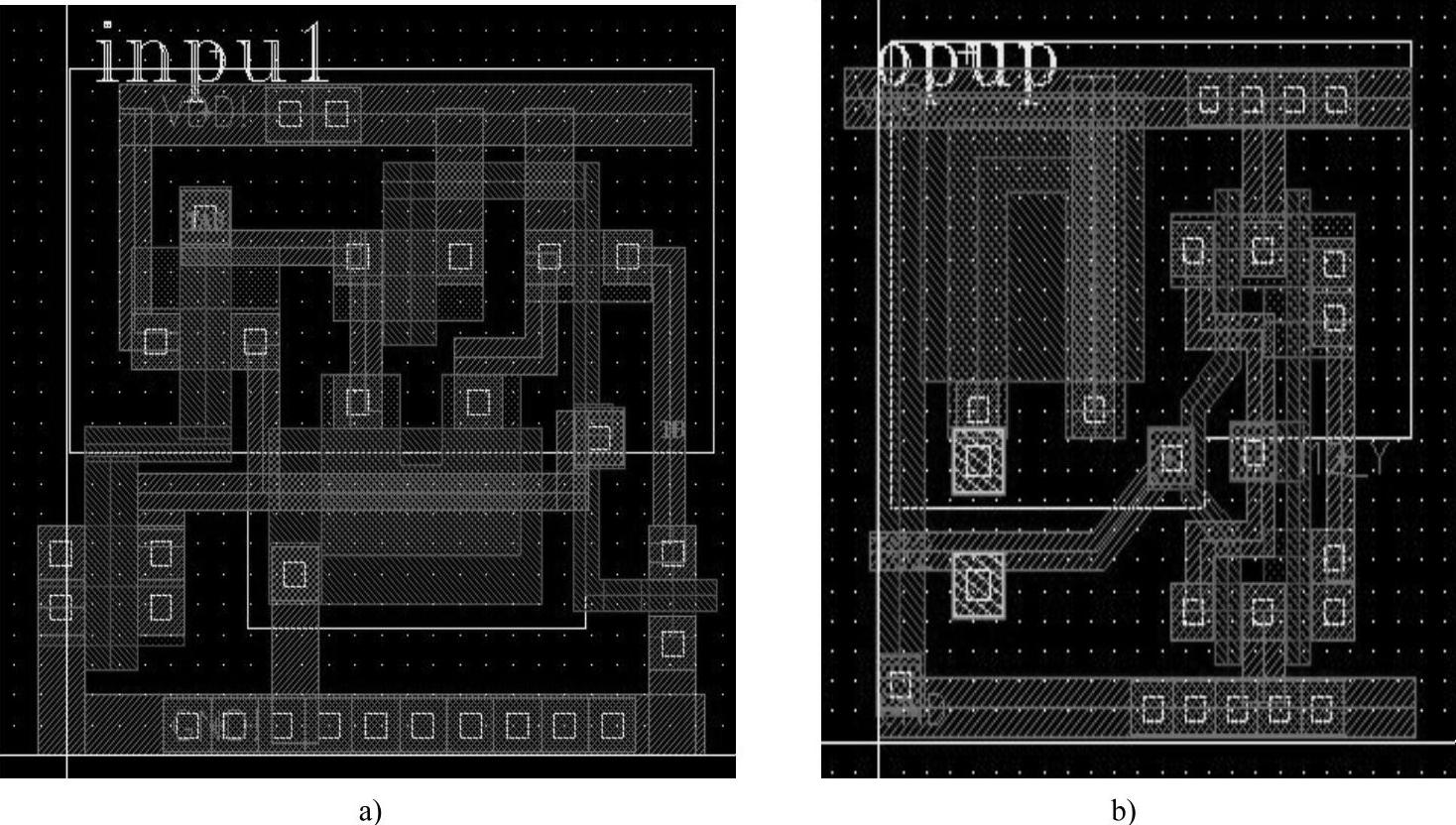

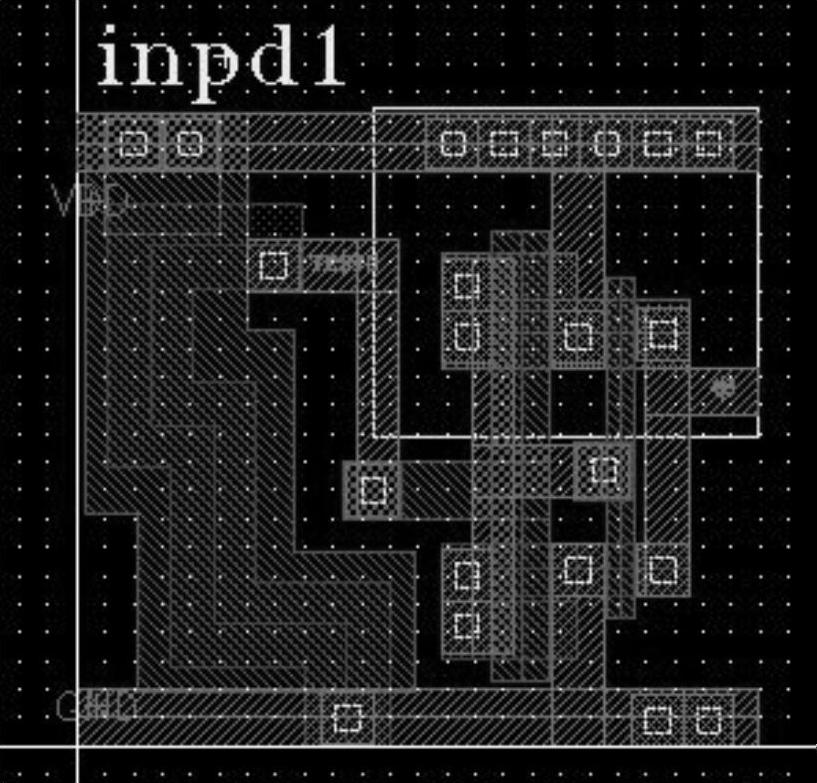

上、下拉电路的版图设计中要考虑衬底噪声的影响。所谓衬底噪声是指源、漏与衬底PN结正偏导通,使得衬底电位产生抖动偏差。解决方法是尽量把衬底与地的接触孔位置和该位置MOS管的衬底注入间的距离做到越小越好,因为这种距离的大小对衬底电位偏差影响非常大,同时还要求衬底接触孔的数量要足够多,保证衬底与电源的接触电阻较小。在图3-14、图3-15所示的上、下拉版图结构中充分考虑了这一点。

图3-13 下拉电路结构图(https://www.xing528.com)

图3-14 上拉电路结构版图

a)上拉电路结构1版图 b)上拉电路结构2版图

图3-15 下拉电路结构版图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。