采用跟以上传输门逻辑图输入和符号建立相同的方法,在D508SCH库中把D508项目所有的逻辑单元全部准备好。

1.单元逻辑图输入的经验总结

1)每一个单元都有Schematic、Symbol两个最重要的属性,逻辑图输入过程中要学会看提示,一旦发现错误马上修正;而触发器的CP/CN端口容易出现连接错误,务必要注意。

2)在进行单元逻辑图输入时要有嵌套的概念,也就是说稍微复杂一点的单元是基于简单的逻辑门基础上建立起来的,举个例子:触发器通常由传输门、与非门、或非门和MOS管组成,那么其中的传输门、与非门、或非门需要做成单元,而不再是单管。

3)单元名称、引脚名称一定要规范,建议与Candence中已有的单元相同,以便减小后续工作量,比如可以参照Cadence自带的Sample库;另外vdd、gnd、ipin、opin、iopin则建议从Cadence自带的Basic库中复制到用户自己输入逻辑图的目录中,然后再调用。

4)同样,数字单元中的三端器件pmos/nmos可先从Cadence自带的Sample库中复制到用户当前库;四端器件pmos4/nmos4可先从Cadence的Analoglib库中复制到用户当前库。

5)建单元时在逻辑编辑工具中把端口名称显示出来,以避免名称和所标符号不一致问题。

6)尽量使用已有库中的内容,如Sample库、Analoglib库、Basic库、用户自己建的库,这样可以节省逻辑单元输入的工作量,但需要注意的是,所调用的单元一定要放在用户自己的库里,可以先把其他库中的单元逻辑图复制到用户自己库中,下面具体介绍这种方法。

2.一种快速输入单元逻辑图的方法

以上建立D508项目单元逻辑图还有一个简单的办法是:把Sample库中有的单元逻辑图COPY到当前D508SCH库中,然后对该单元的逻辑图进行修改,包括端口等,这种方法可以避免像以上传输门逻辑图建立过程那样烦琐的步骤,下面以创建一个二输入端与门的单元逻辑图为例说明。

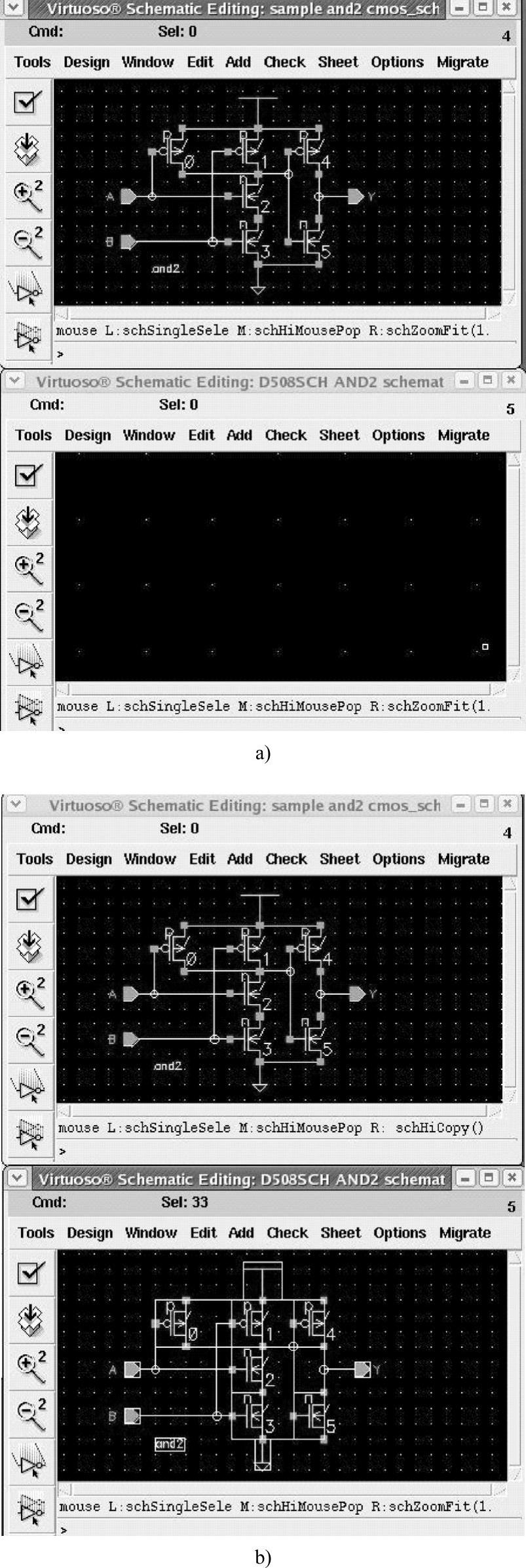

首先新建一个二输入端与门单元,方法如图2-7所示,单元名称为AND2;然后打开Sample库中的and2单元的Cmos_sch View(这个视图格式就是Schematic);把以上两个逻辑图编辑界面放在一起,如图2-27a所示。

然后把在Sample库中打开的and2单元编辑界面中的所有元器件都选上,单击“COPY”命令,把选上的内容放置到D508SCH库中正在编辑的AND2界面中,如图2-27b所示,这样就可以方便地建立AND2的逻辑图。用这种方法的前提是Sample库中有正在建立单元的逻辑图。上面举的传输门的例子在Sample库中只有符号图,无逻辑图,只能一步一步创建。

图2-27 采用COPY方式建立AND2逻辑图

a)步骤1 b)步骤2

3.单元的宽长比设置原则

每一个单元在建立逻辑图的过程中都要输入参数,以便后续做电路模拟和版图验证,就像图2-17中对器件进行参数设置一样,这是逻辑输入的一项重要工作。在单元参数中,MOS管的宽长比是最重要的参数,也是版图设计所必不可少的,因此这里重点介绍宽长比的设置。

关于宽长比的设置需要遵循一定的原则,这样才能为后续的版图验证打下基础。下面以一个二输入端与非门的例子来说明宽长比的设置原则。

(1)NAND2单元最常见宽长比的设置

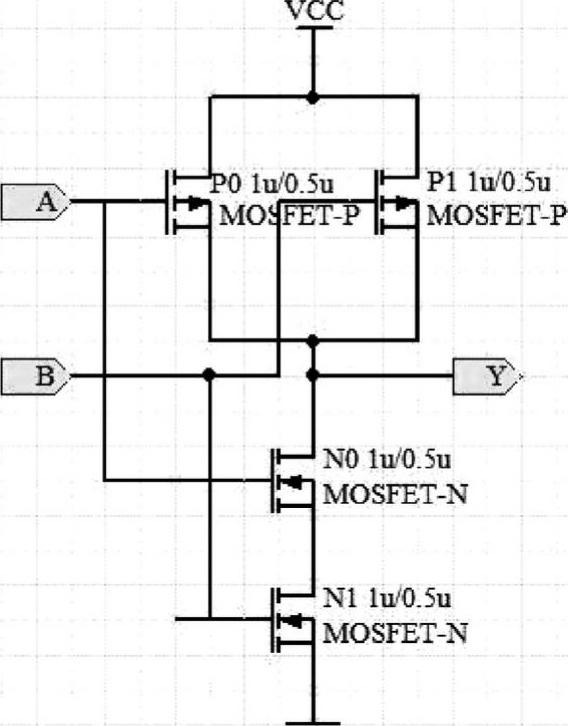

图2-28 准备做LVS的NAND2单元逻辑图

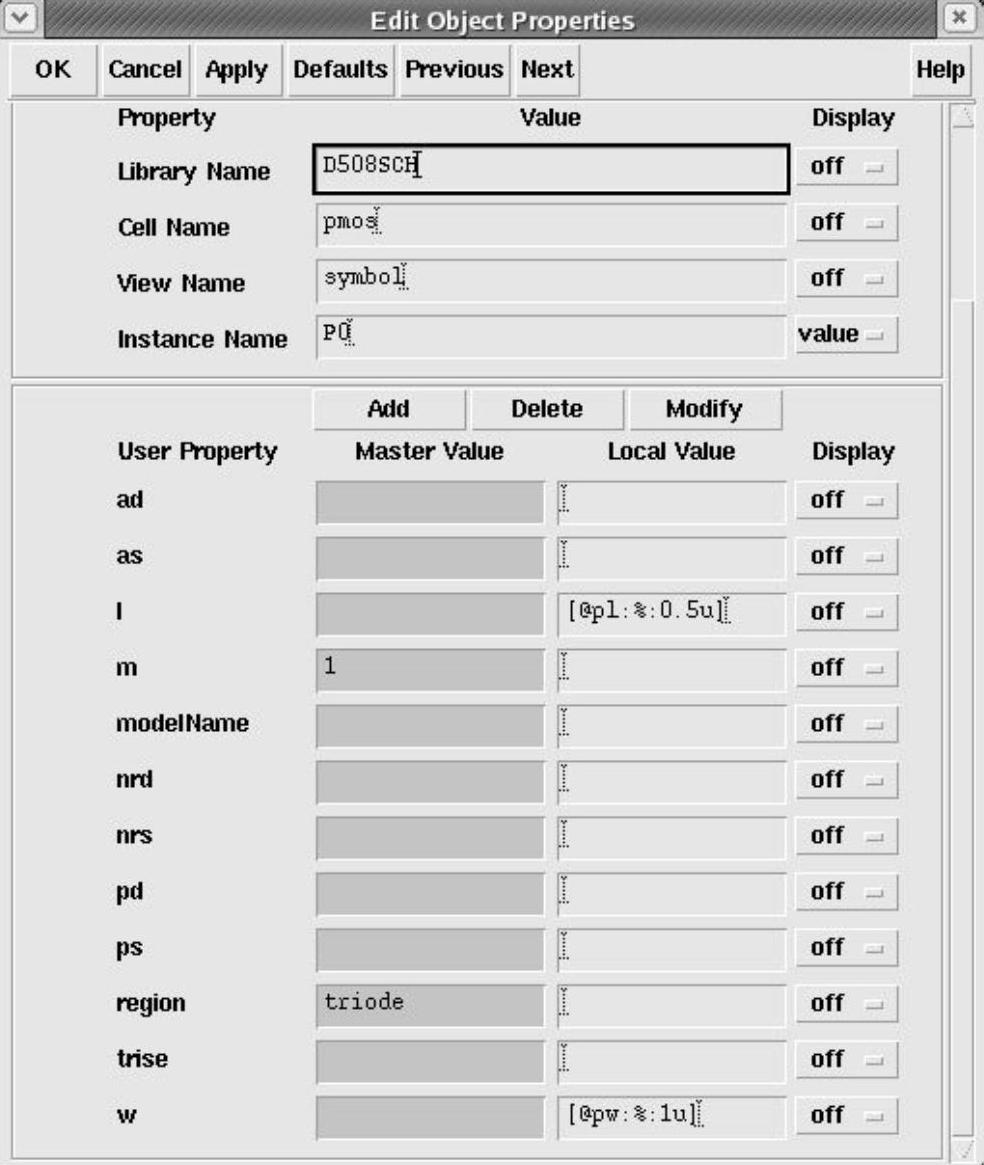

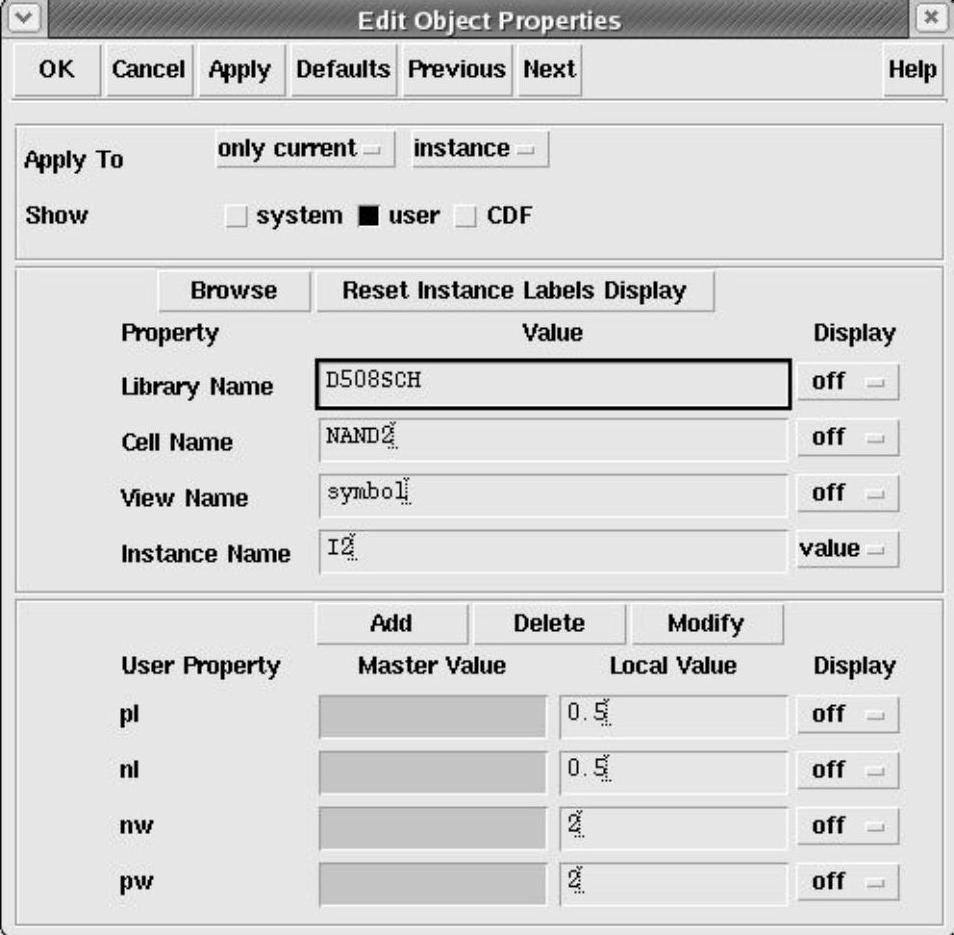

图2-28所示为准备做LVS的NAND单元逻辑图。是一个二输入端的与非门—NAND2,其中MOS管的宽长比设置如下:选中图中的pmos管(注:由于NAND2为数字单元,其中MOS管的衬底是接固定电位的,也就是说pmos管衬底接VCC或VDD,nmos管衬底接GND,因此不需要像2.1.2节中介绍传输门逻辑图输入那样采用四端器件,只要采用三端器件就可以了),然后选择Edit菜单中的Properties选项,选择Objects,弹出图2-29所示的NAND2单元宽长比的设置界面。

图2-29 NAND2单元宽长比的设置界面

注意:为满足电路设计的要求,一个电路中的NAND2单元通常有几种类型的宽长比,举个例子:图2-28中所设置的pmos管、nmos管均为1/0.5,还有2/0.5、3/0.8等其他几种类型,但这几种类型的宽长比中肯定有在电路中相对采用比较多的一种,假设1/0.5这种宽长比在D508项目中最多,也就是说D508项目中有很大一部分NAND2单元都采用了1/0.5这样的宽长比,那么这种宽长比就按图2-29的方式进行设置,而其他类型的宽长比再用下面介绍的另外的方式设置。

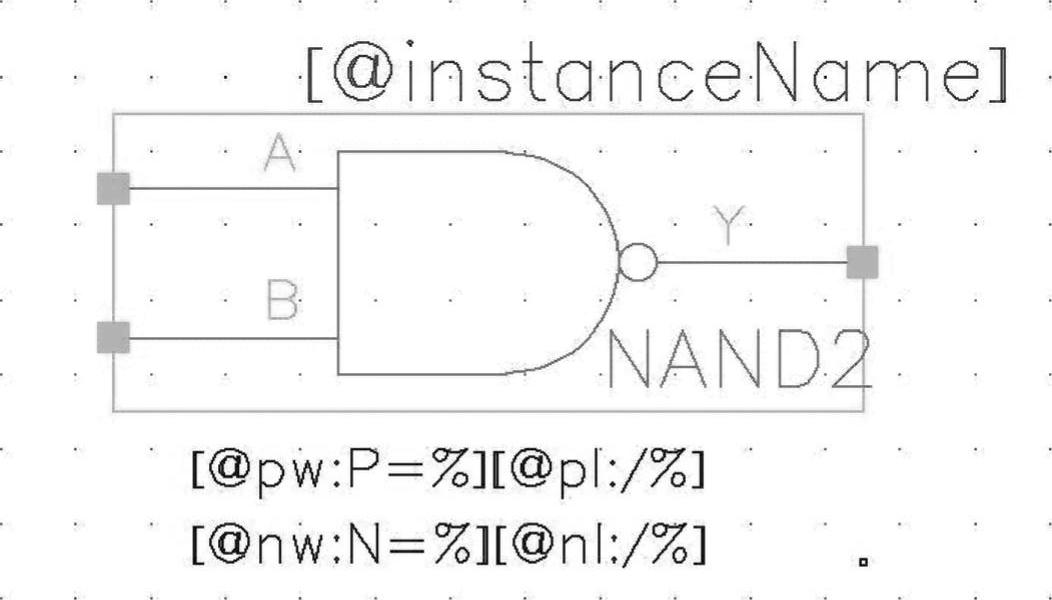

(2)NAND2单元符号图建立

为了使得后续工作能够顺利进行,NAND2这个单元的符号(symbol)建立的时候也是需要注意的,图2-30是一个标准的NAND2单元的符号图。

图2-30 一个标准的NAND2单元的符号图

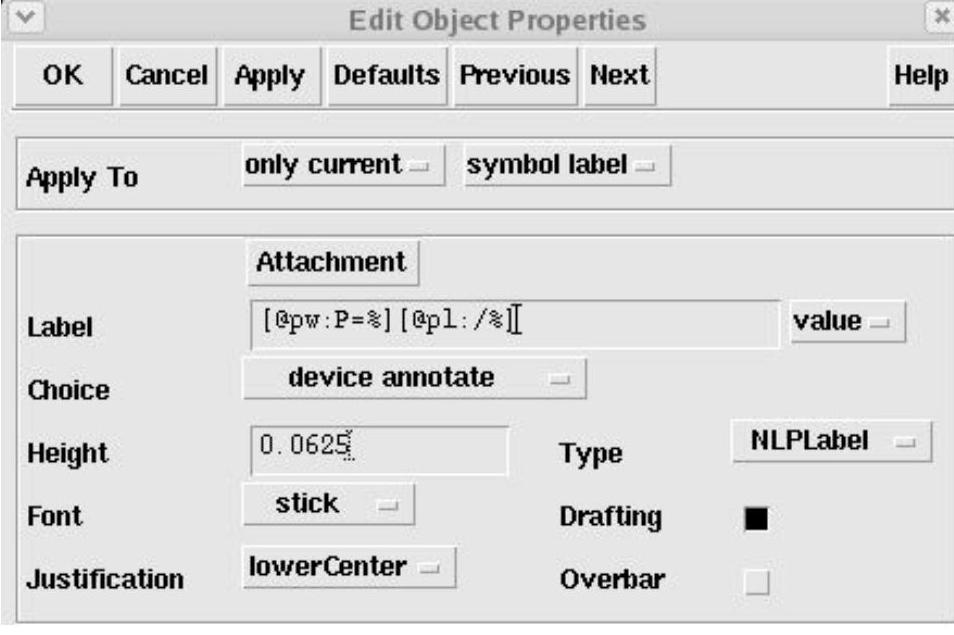

图2-30中方括号中两行是在建symbol的时候添加的label,注意选择类型为:device annotate,NAND2的符号图建立选项如图2-31所示,其中Choice一栏要选择device annotate。

图2-31 NAND2的符号图建立选项

(3)NAND2单元其他类型宽长比设置

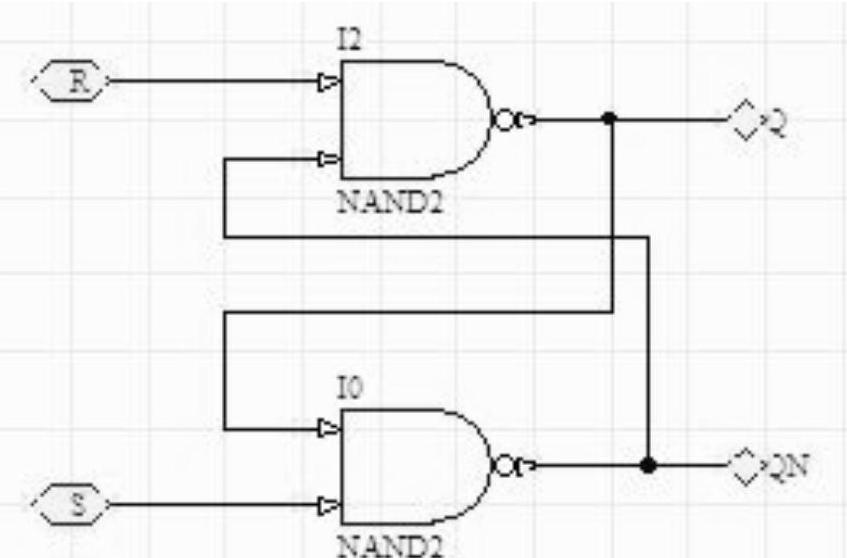

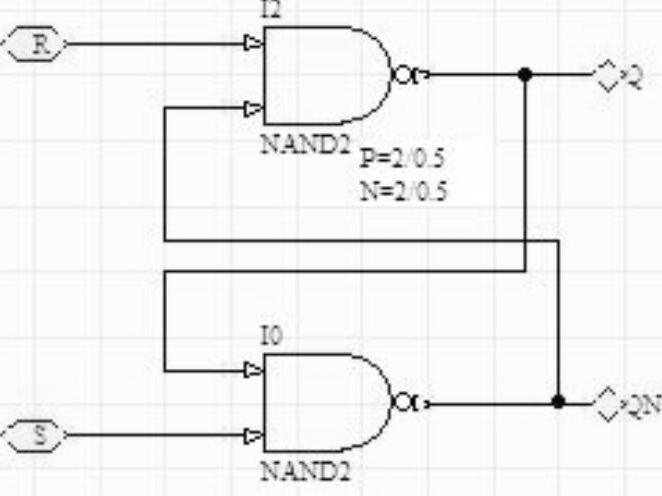

下面介绍NAND2其他类型的宽长比设置。D508项目中有一个锁存器LAT,它调用了两个NAND2单元,LAT的逻辑图如图2-32所示。

图2-32 LAT的逻辑图

在图2-32中,假设调用名称(Instance Name)为I0的这个NAND2的宽长比就是以上设置好的最常见的宽长比1/0.5,而另外一个调用名称为I2的NAND2单元的宽长比为2/0.5(该NAND2的两个pmos管和两个nmos管的宽长比均为2/0.5)。那么I0这个NAND2的宽长比就不需要设置,而宽长比为2/0.5的NAND2的宽长比可以按照以下方式设置。

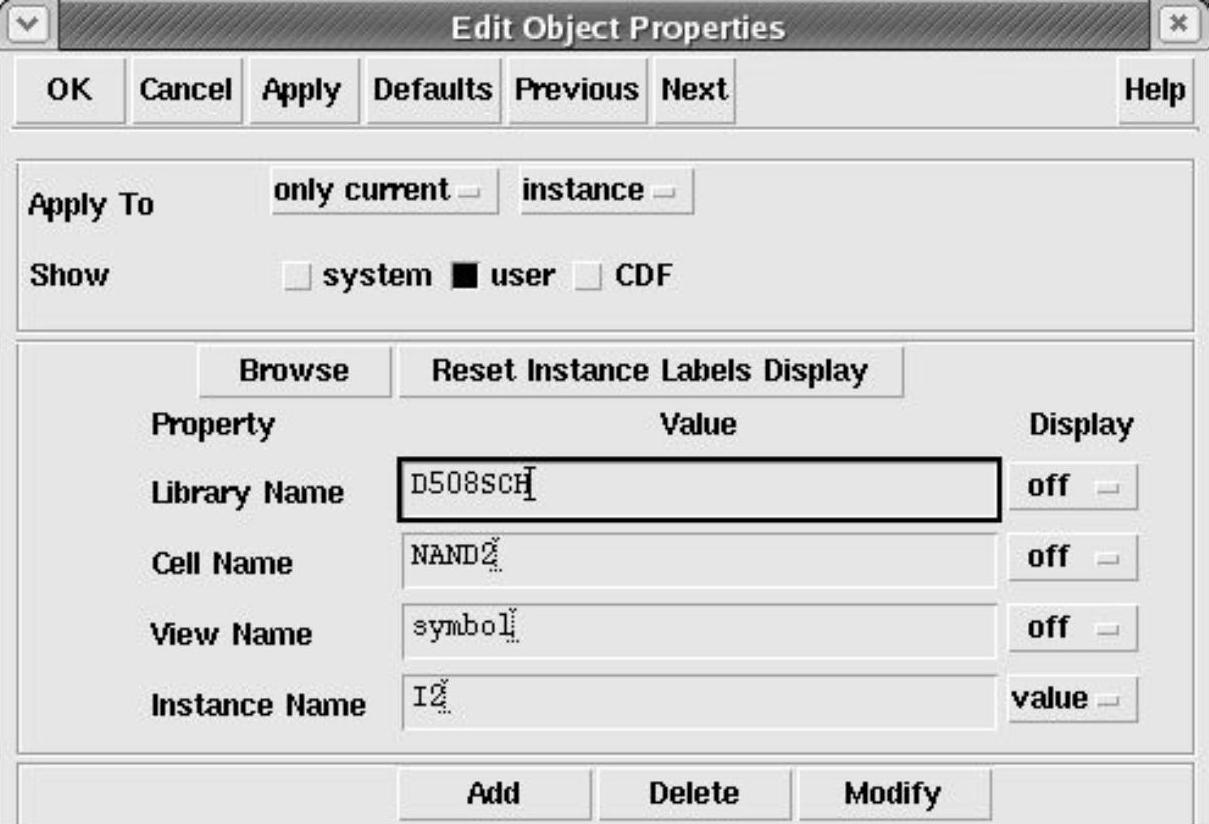

在图2-32中选择这个NAND2,然后选择Edit菜单中的Properties选项,选择Objects,弹出图2-33所示的锁存器LAT宽长比的设置界面。

图2-33 锁存器LAT宽长比的设置界面

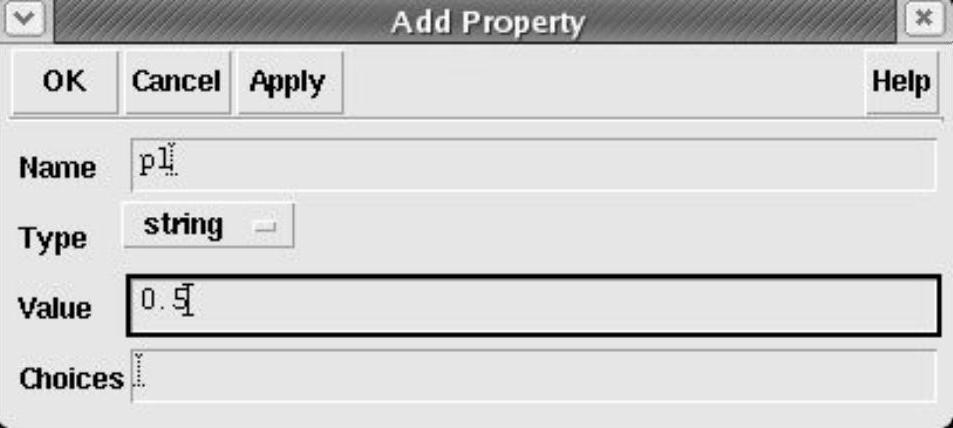

单击图2-33中的“ADD”按钮,弹出图2-34所示的界面,在其中的Name一栏填写pl,即pmos管的沟道长度L;在Value中填写0.5,即上面提到的宽长比为2/0.5的NAND2的沟长。

按此同样方法,分别设置pw、nl、nw等,完成后的这个NAND2宽长比设置结果如图2-35所示。

图2-34 LAT中NAND2宽长比的设置(https://www.xing528.com)

图2-35 LAT中NAND2宽长比设置完成

以上宽长比设置完成后的LAT的逻辑图如图2-36所示。

图2-36 宽长比设置完成的LAT逻辑图

从图2-36可以看出,I2这个NAND2的宽长比为2/0.5(pmos管、nmos管均为2/0.5),而I0这个NAND的宽长比没有显示,就表示这个NAND2的宽长比是默认的,也就是说是图2-29中所设置的最常见的宽长比1/0.5。

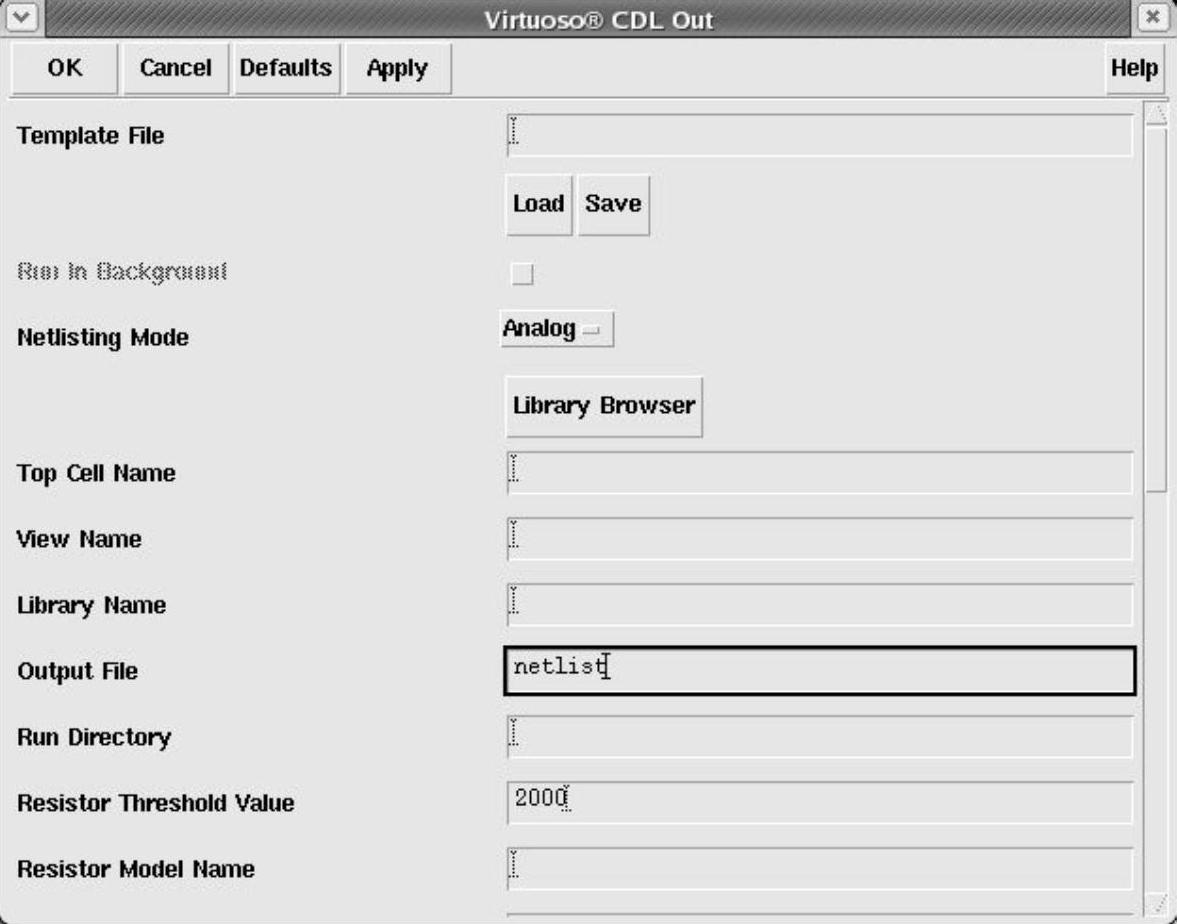

可以把图2-36中的LAT导出其CDL网表(CDL网表是Cadence系统中的电路数据格式),可以进一步看出这两个NAND2的宽长比的不同。方法是选择CIW界面File菜单中的Export选项,选择CDL格式,出现图2-37所示的CDL网表导出界面。

图中“TOP Cell Name”(顶层单元名)填写LAT;“View Name”(视图名称)填写schematic;“Library Name”(库名)填写D508SCH;“Output File”(输出文件)填写LAT.cdl指定路径为./netlist,其中“.”指的是工作目录,也是icfb启动的当前目录,即/home/angel/cds,在该目录下有一个netlist的子目录,用于存放产生的LAT.cdl文件。

图2-37 CDL网表导出界面

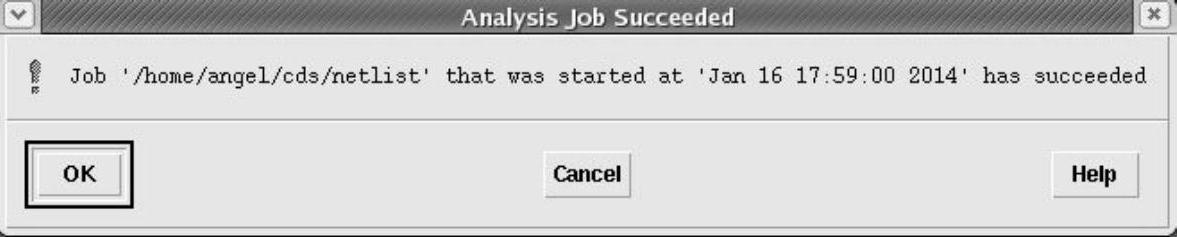

单击“OK”按钮后就会显示图2-38所示的CDL网表导出成功信息,同时在/home/angel/cds/netlist中产生了一个名为LAT.cdl的网表文件。

图2-38 CDL网表导出成功

注意1:有的时候由于Cadence工具版本等问题,以上导出CDL的过程中会出现不成功的情况,其中一个原因是网表导出模式问题;如果出现不成功的情形,把图2-37中的网表导出模式Netlisting mode再改成Digital,重新导出CDL,一般都可以解决问题。

注意2:导出CDL文件的选项中有Resistor Threshold Value(电阻的阈值)、Check Resistors、Check Capacitors、Check Diodes等内容需要填写,这些都是针对整个电路导出CDL网表的时候需要考虑的,因为整个电路中可能会有电阻、电容和二极管等特殊元器件,如遇到这些元器件,以上几个选项分别填写的内容是:1、value、value、area;这里举的NAND2例子是没有这些特殊元器件的,因此这些选项不用考虑。

注意3:如果在这一步中显示导出CDL失败(failed),那么在/home/angel/cds/netlist中会产生一个si.log文件,用文本编辑器Vi打开si.log,可以看到失败的原因,并做相应修改,然后重新导出CDL。

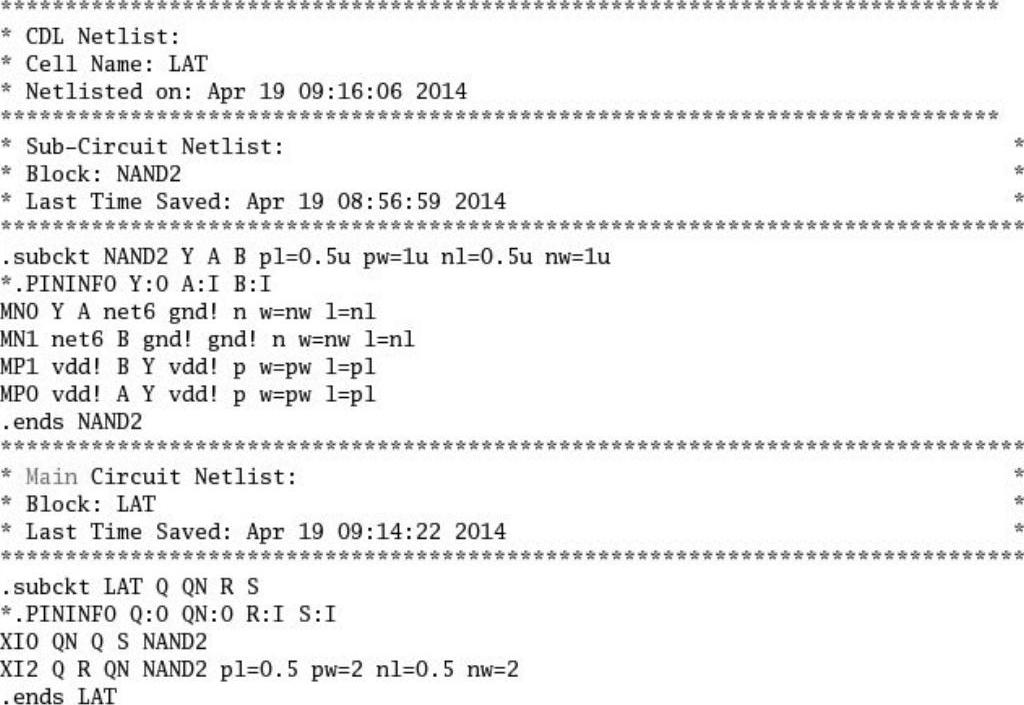

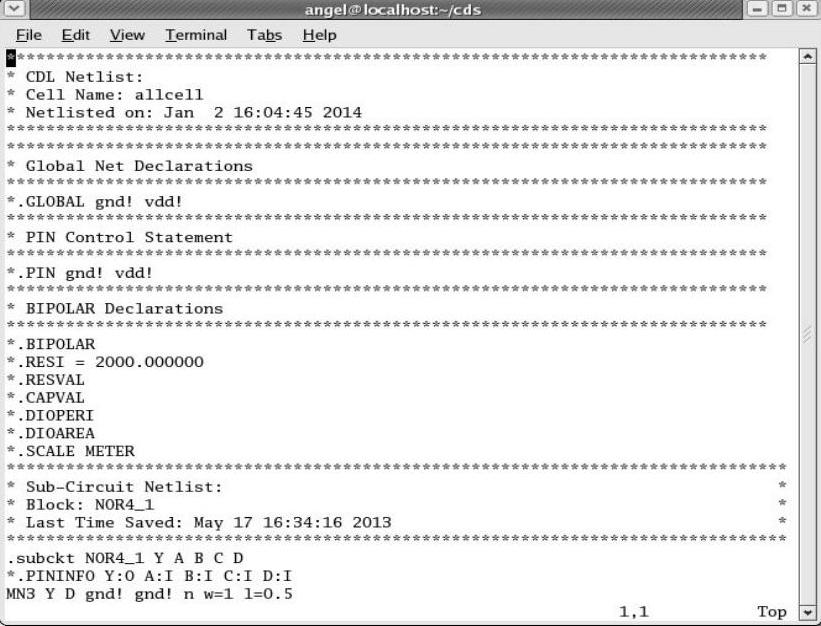

图2-39为以上操作步骤所产生的LAT的CDL网表。

图2-39 LAT的CDL网表

从图2-39中可以看到,I2这个NAND2的宽长比为2/0.5,而I0这个NAND2的宽长比采用的是子单元定义subckt NAND2中定义的默认的宽长比:1/0.5。通过以上方法就实现了D508项目中相同的NAND2单元、但不同的宽长比的设置工作。

注意:以上这种宽长比的设置方法在进行项目设计过程中一直会遇到,为避免后续设计过程中出现问题,一定要按照以上方式进行宽长比的设置。

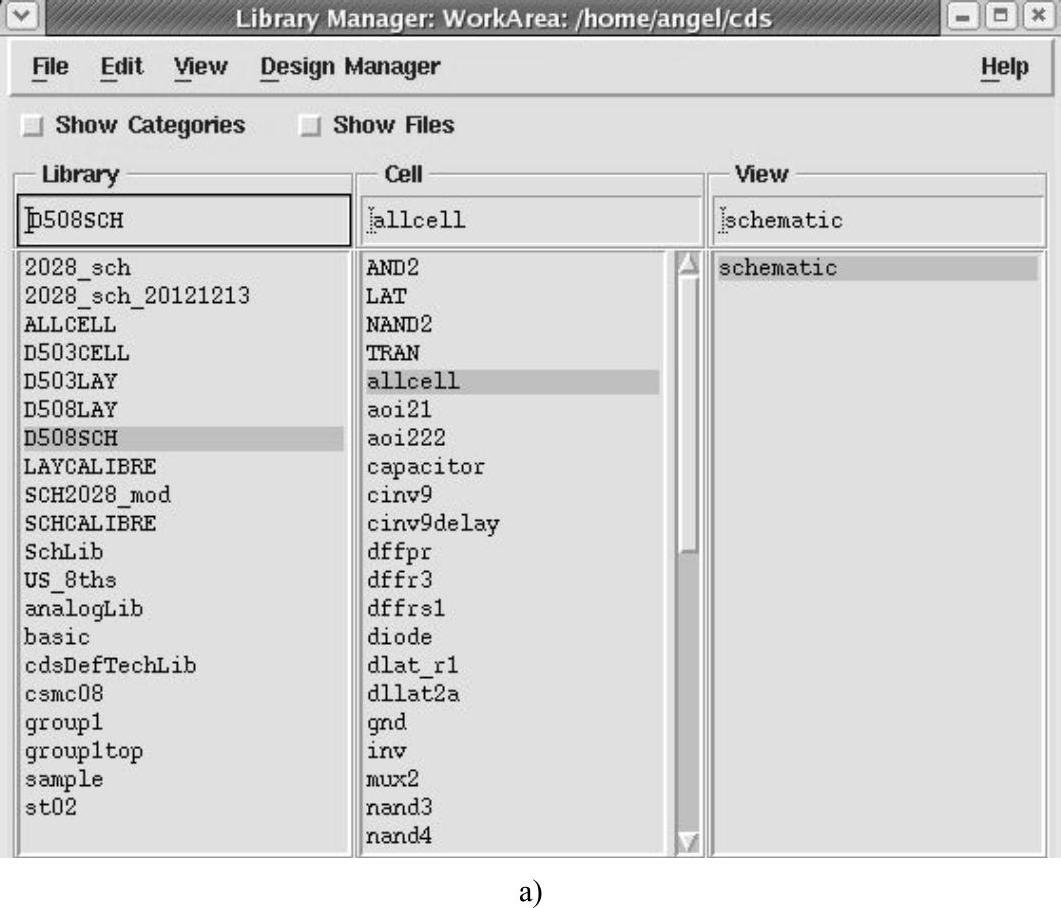

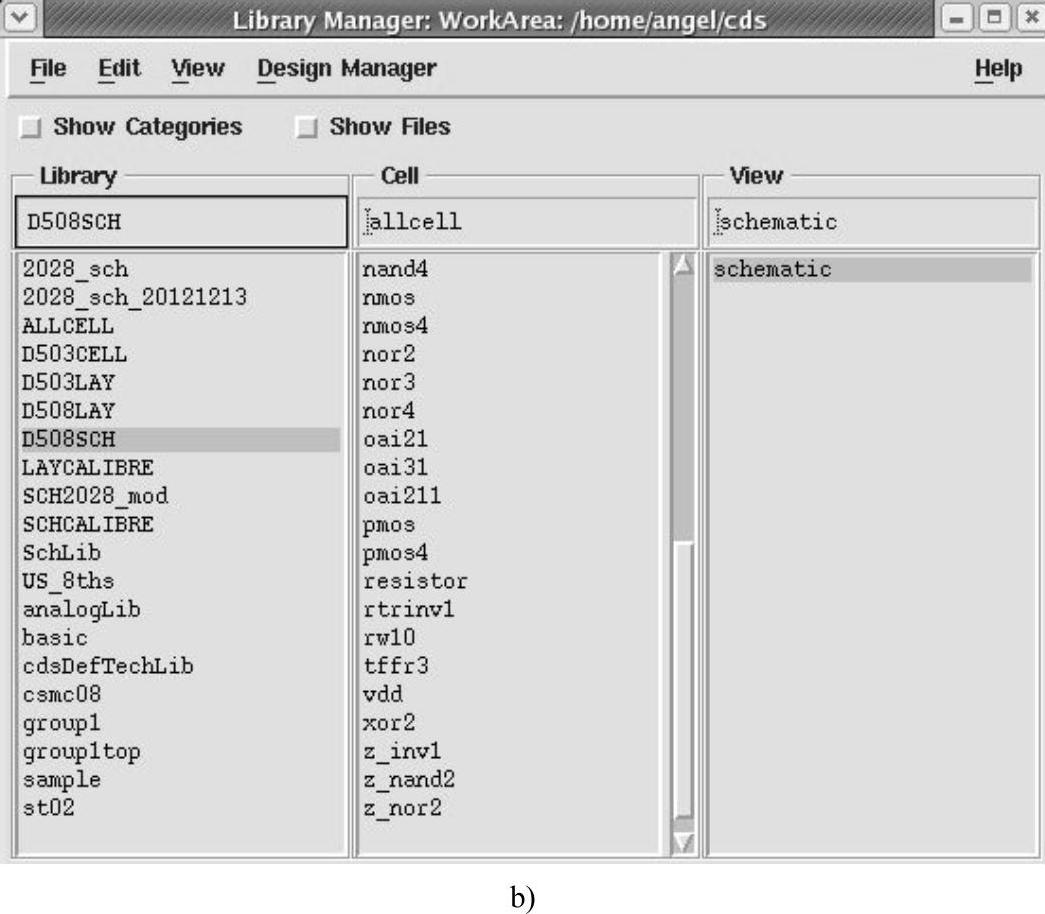

4.D508项目所有的单元

图2-40a、图2-40b显示了D508项目的所有单元列表,这些单元都分别在Cadence系统中完成了逻辑图的输入,都放在名为D508SCH的逻辑库中,其中pmos、nmos、diode、resistor、vdd、gnd等分别是从Cadence自带的sample库和basic库中复制过来的。

图2-40 D508项目的所有单元列表

图2-40 D508项目的所有单元列表(续)

a)列表1 b)列表2

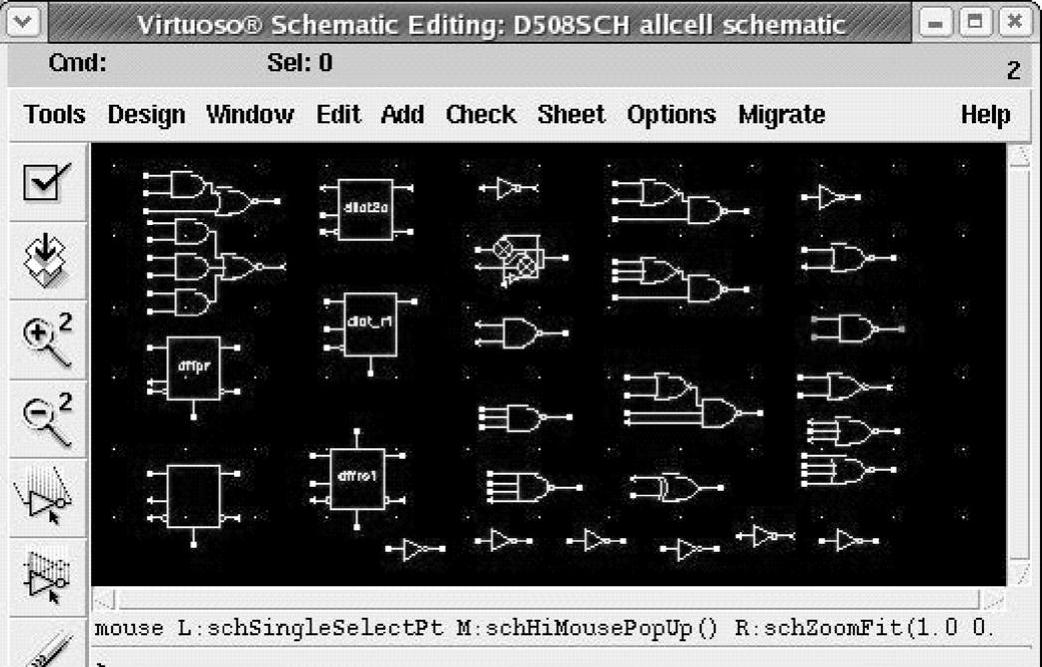

为了确保D508项目中的所有单元都在Cadence中建立了相应的逻辑图,可以在以上D508SCH库中再新建一个单元,取名为allcell,然后把图2-40a、图2-40b所示的跟D508项目相关的全部单元都放置在allcell中,如图2-41所示。这样做的好处有两个。

图2-41 包含D508项目所有单元的allcell

1)通过把在Cadence D508SCH库中所有单元都放置在allcell过程,可以检查所有单元是否都建立了相应的逻辑图,不至于遗漏。

2)可以确认以上所建的单元逻辑都调用了D508SCH这个库中的单元,而没有调用其他库中的单元。因为在后续数据处理的时候要确保单元调用的有效性,否则容易出错。

具体确认的过程如下所述。

首先采用图2-37所示的方法在Cadence中导出allcell单元的CDL文件;然后用Vi编辑器打开allcell.cdl文件,图2-42是allcell的部分CDL。

图2-42 allcell的部分CDL

从该文件中可以看出,allcell调用了D508SCH库中的单元都会在该文件中显示出来,例如图2-42中显示的NOR4_1单元,因此逐个检查这些单元,就可以判断是否有不属于D508SCH这个库的单元被allcell所调用,如果有,要把这个单元复制到D508SCH库中,以确保调用的有效性。

注意:由于allcell调用了很多单元,如果其中某一个单元在修改完成后没有保存,那么以上导出CDL的时候会出现错误,因此在allcell导出CDL之前需要对每一个作了修改但没有保存的单元都重新保存一下。如果每一个这样的单元都用逻辑图编辑工具打开,并且执行Check and Save命令,这样会比较麻烦,一个简单的办法是在打开了allcell逻辑图的编辑工具内,执行Check菜单下的Check Hierarchy选项,会弹出图2-43所示的嵌套关系检查界面。

图2-43 嵌套关系检查的界面

在图2-43中,Process选择every schematic;Referenced library通常选择do not check;Save schematics选择yes;单击“OK”按钮后,就可以把allcell所调用的所有子单元全部进行一遍Check and Save,从而一次性解决上面提到的底层单元修改时没有保存而造成顶层单元导出CDL时出现的问题。

以上建立allcell的方法也是为后续基于标准单元的版图设计做准备的,关于这部分内容将在第5章中作详细介绍。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。