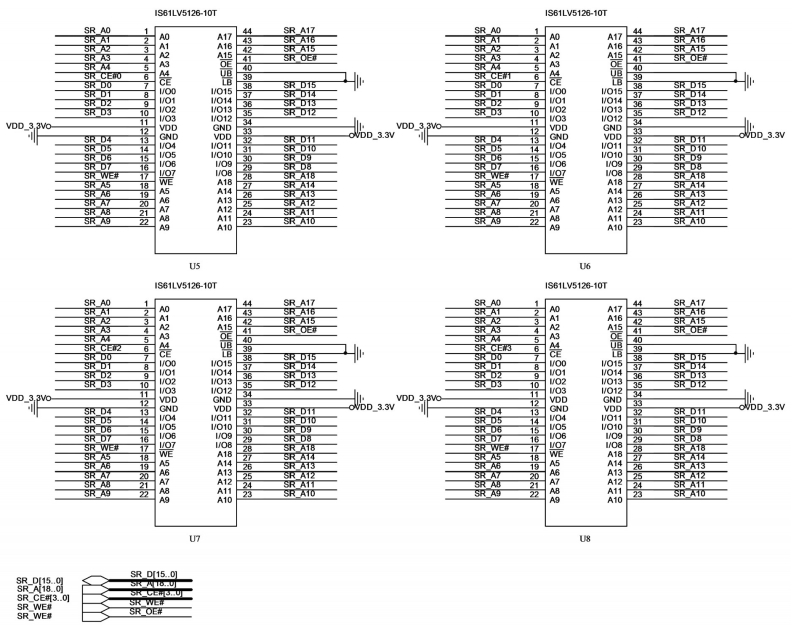

在FPGA内部进行串并转换后,每个采样点将转化为一个16位的二进制数据。PXI-11154每个通道的数据深度为512K,即每个通道都能够存储512K个采样点。当触发条件满足后,数据就会保存到存储器中,4个通道一共能存储2M个采样点。这些数据通过FPGA逻辑控制将被传送到SRAM(Static Random Access Memory)保存。SRAM的特点是工作速度快,容量较小。根据设计要求采集系统选用的SRAM是IS61LV51216-10T,它是一款具有高速存取速度(10ns),单片容量为8M位(存储单元阵列为512K×16bit),一次能够进行16位数据交换的高性能异步SRAM。一个通道配备一片SRAM。IS61LV51216主要由四部分组成:存储单元阵列、地址译码器、缓冲/驱动电路和控制电路。

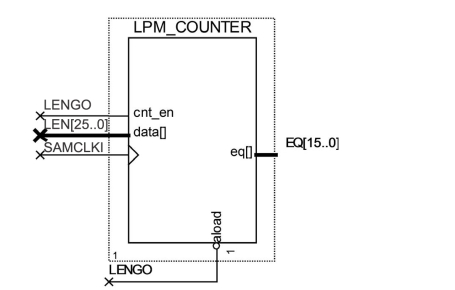

触发信号产生后,采集的信号就会源源不断地进入存储模块。在FPGA内部设计了一个计数器,每采集一个数据点计数器就自动加1,直到计数值与设置的采样长度相等时产生结束信号。如图3-18所示,计数使能端是LENGO,LEN[25.0]是设定的计数初始值,计数脉冲信号是SAMCLKI,它的时钟频率等于采样频率,这样就能够做到每采集一个数据就保存一个数据。PXI-11154有四个通道,以每采集一次会产生4个数据,由于PXI-11154是同步并行采集模块,计数器还是只计数一次。模块完成一次采样的时间(Sample Time)与采样长度(Sample Length)和采样频率(Sample Frequency)有关,采样长度不能超过数据存储深度。

![]()

式中Sample Time单位是秒(s),Sample Length单位是采样点(Sa),Sample Frequency单位是赫兹(Hz)。

图3-18 采集计数器逻辑电路图

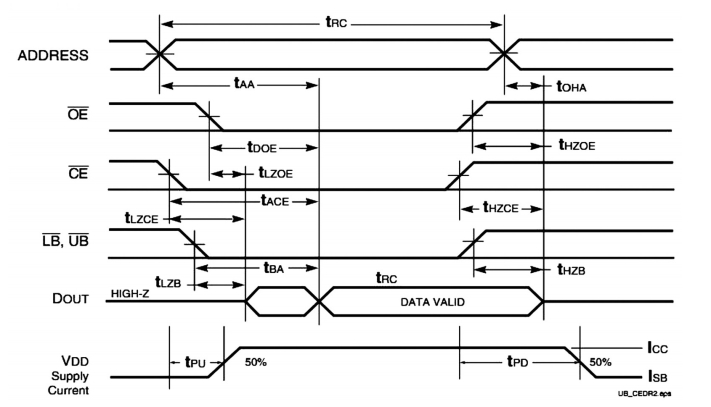

SRAM类似一个数据中转站。一方面保存输入信号的数据,另一方面计算机通过PXI总线将保存的数据取走。因此SRAM最重要的功能就是读/写数据。为保证读/写数据准确性设计逻辑电路时就必须严格遵守IS61LV51216的时序要求,满足其时间边界条件。

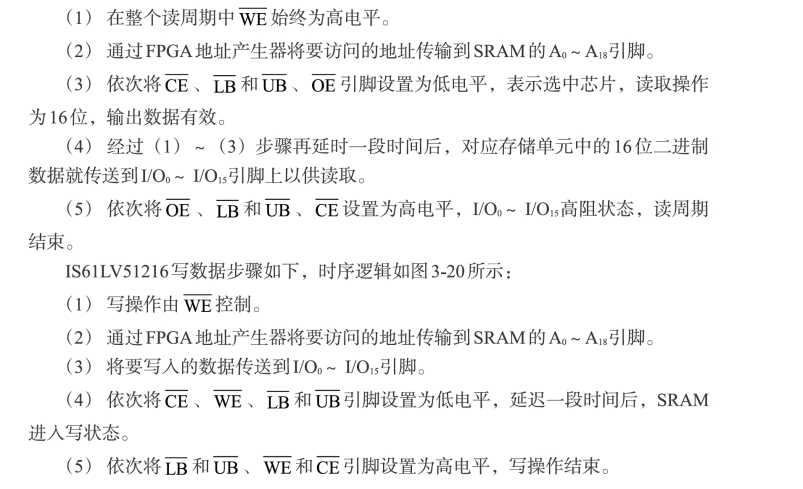

IS61LV51216读数据步骤如下,时序逻辑如图3-19所示:(https://www.xing528.com)

图3-19 IS61LV51216读数据时序图

图3-20 IS61LV51216写数据时序图

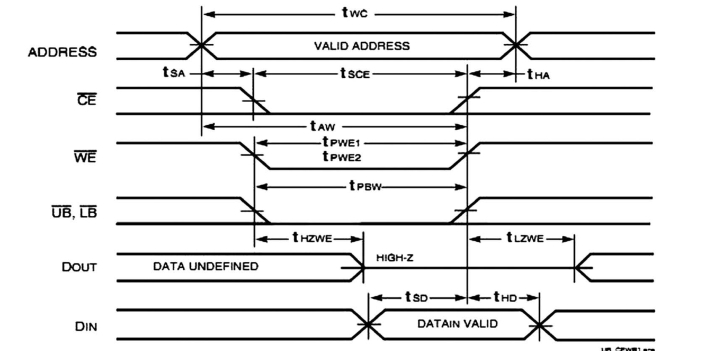

图3-21 存储单元原理图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。