1.AR-处理器模式

用户(User)模式:AR-处理器正常的程序执行状态。

快速中断(FIQ)模式:用于高速数据传输或通道处理。

外部中断(IRQ)模式:用于通用的中断处理。

管理(Supervisor)模式:操作系统使用的保护模式。

数据访问终止(Abort)模式:当数据或指令预取终止时进入该模式,可用于虚拟存储及存储保护。

系统(System)模式:运行具有特权的操作系统任务。

未定义指令中止(Undefined)模式:当未定义的指令执行时进入该模式,可用于支持硬件协处理器的软件仿真。

2.AR-微处理器的工作状态

AR-体系结构除了支持执行效率很高的32位AR-指令集以外,同时支持16位的Thumb指令集。AR-体系结构支持AR-、Thumb指令集。Thumb指令集是32位AR-指令集的一个子集,仅仅把常用的AR-指令压缩成16位的指令编码方式,这样可以实现更高的代码密度,但会损害系统性能,因为在指令的执行阶段,16位的指令被重新解码,以完成对等的32位指令所实现的功能。

与AR-指令集相比,Thumb指令集中的数据处理指令的操作数仍然是32位,指令地址也为32位,指令长度则为16位。在一般的情况下,Thumb指令与AR-指令的时间效率和空间效率关系为:

Thumb代码所需的存储空间约为AR-代码的60%~70%。

Thumb代码使用的指令数比AR-代码多约30%~40%。

若使用32位的存储器,AR-代码比Thumb代码快约40%。

若使用16位的存储器,Thumb代码比AR-代码快约40%~50%。

与AR-代码相比较,使用Thumb代码,存储器的功耗会降低约30%。

显然,AR-指令集和Thumb指令集各有其优点。若对系统的性能有较高要求,应使用32位的存储系统和AR-指令集;若对系统的成本及功耗有较高要求,则应使用16位的存储系统和Thumb指令集。

AR-微处理器的工作状态有两种,两种状态之间可以切换,但AR-微处理器在开始执行代码时,应该处于AR-状态。

进入Thumb状态:当操作数寄存器的状态位(位0)为1时,可以采用执行BX指令的方法,使微处理器从AR-状态切换到Thumb状态。此外,当处理器处于Thumb状态时发生异常(如IRQ、FIQ、Undef、Abort、SWI等),则异常处理返回时,自动切换到Thumb状态。

进入AR-状态:当操作数寄存器的状态位为0时,执行BX指令时可以使微处理器从Thumb状态切换到AR-状态。此外,在处理器进行异常处理时,把PC指针放入异常模式链接寄存器中,并从异常向量地址开始执行程序,也可以使处理器切换到AR-状态。

3.AR-寄存器

AR-微处理器共有37个32位寄存器,其中31个为通用寄存器,6个为状态寄存器。通用寄存器R14~R0、程序计数器PC、状态寄存器在任何时候都可以访问。其余的寄存器不能被同时访问,具体哪些寄存器可以编程取决于微处理器的工作状态及运行模式。

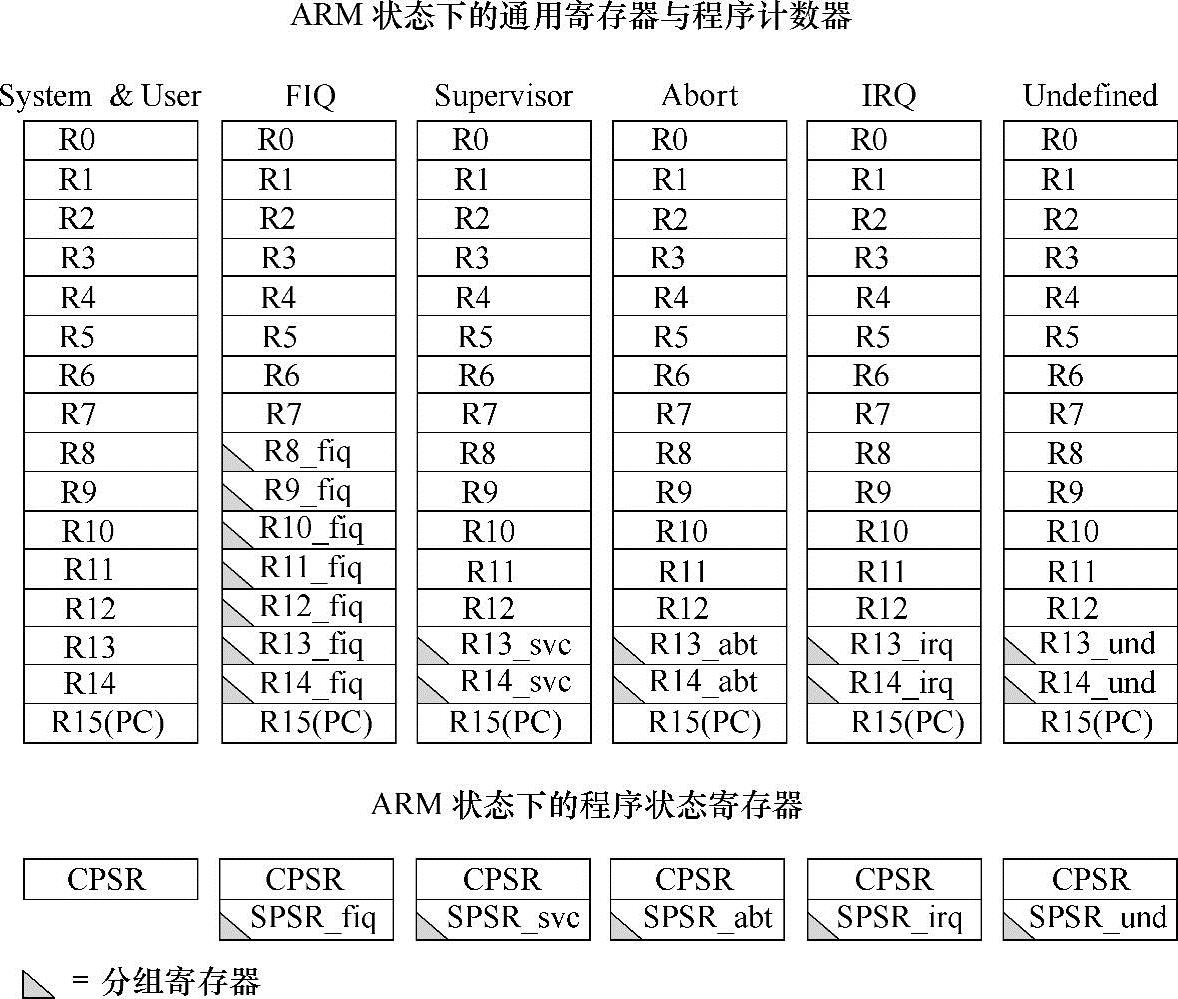

(1)AR-状态下的寄存器组织

1)通用寄存器。R0~R15为通用寄存器,分为三类:未分组寄存器R0~R7;分组寄存器R8~R14;程序计数器PC(R15)。

2)未分组寄存器R0~R7。未分组寄存器都映射到同一个物理寄存器。

3)分组寄存器R8~R14。分组寄存器每次所访问的物理寄存器不同,与处理器当前的运行模式有关,如图9-61所示。

图9-61 AR-状态下的寄存器组织

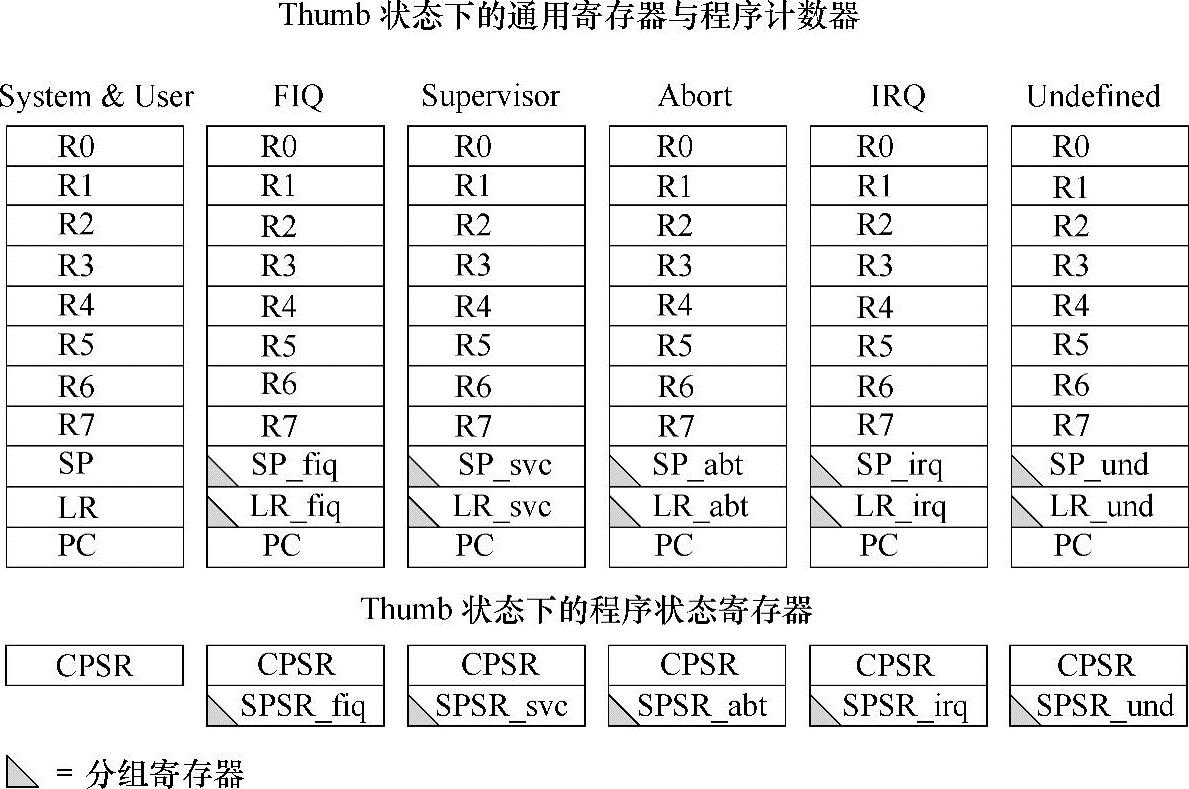

(2)Thumb状态下的寄存器组织 Thumb状态下的寄存器集是AR-状态下寄存器集的一个子集,如图9-62所示。程序可以直接访问8个通用寄存器R7~R0、程序计数器PC、堆栈指针SP、连接寄存器LR和CPSR。同时,在每一种特权模式下都有自己的SP、LR和SPSR。

图9-62 Thumb状态下的寄存器组织

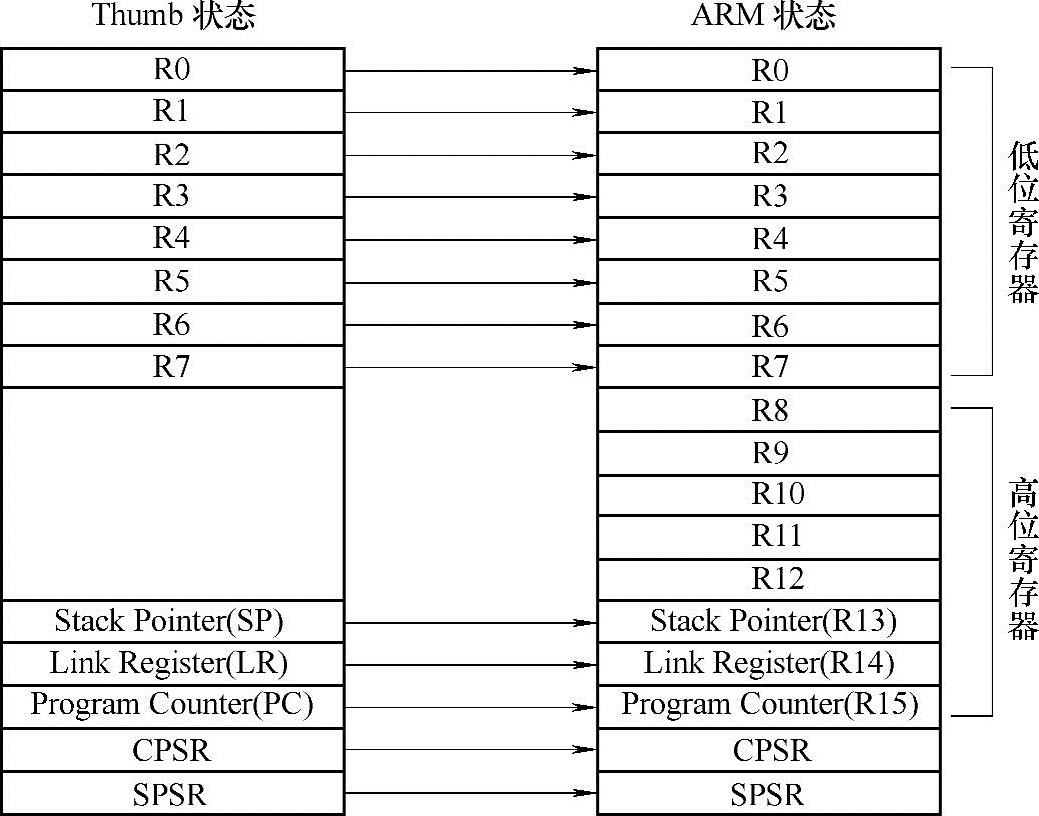

(3)AR-状态与Thumb状态下的寄存器组织的关系 AR-状态与Thumb状态下的寄存器组织的关系如图9-63所示。

图9-63 AR-状态与Thumb状态下的寄存器组织的关系

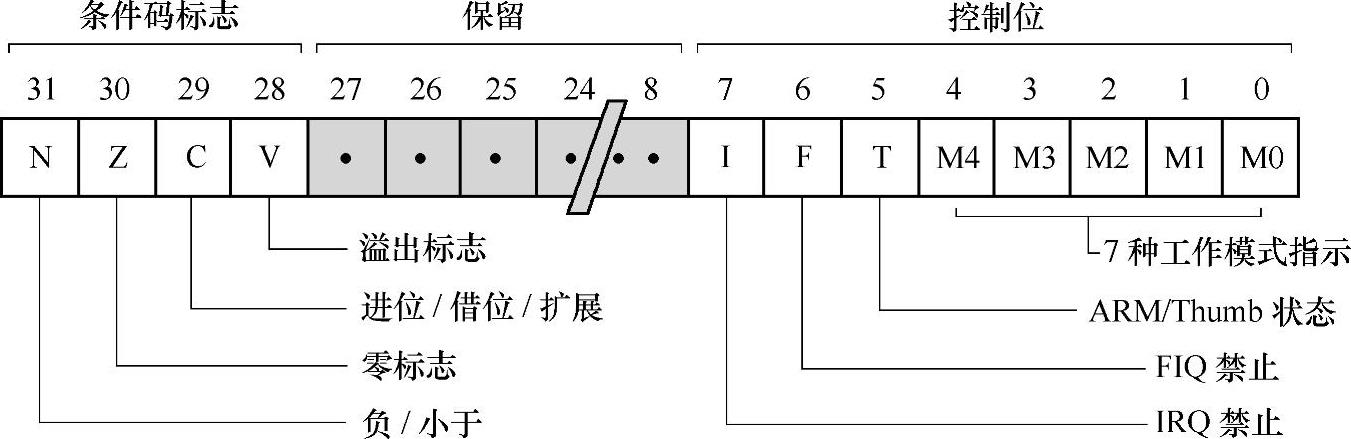

(4)程序状态寄存器 AR-体系结构包含一个当前程序状态寄存器(CPSR)和5个备份的程序状态寄存器(SPSRs)。程序状态寄存器的每一位的安排如图9-64所示。

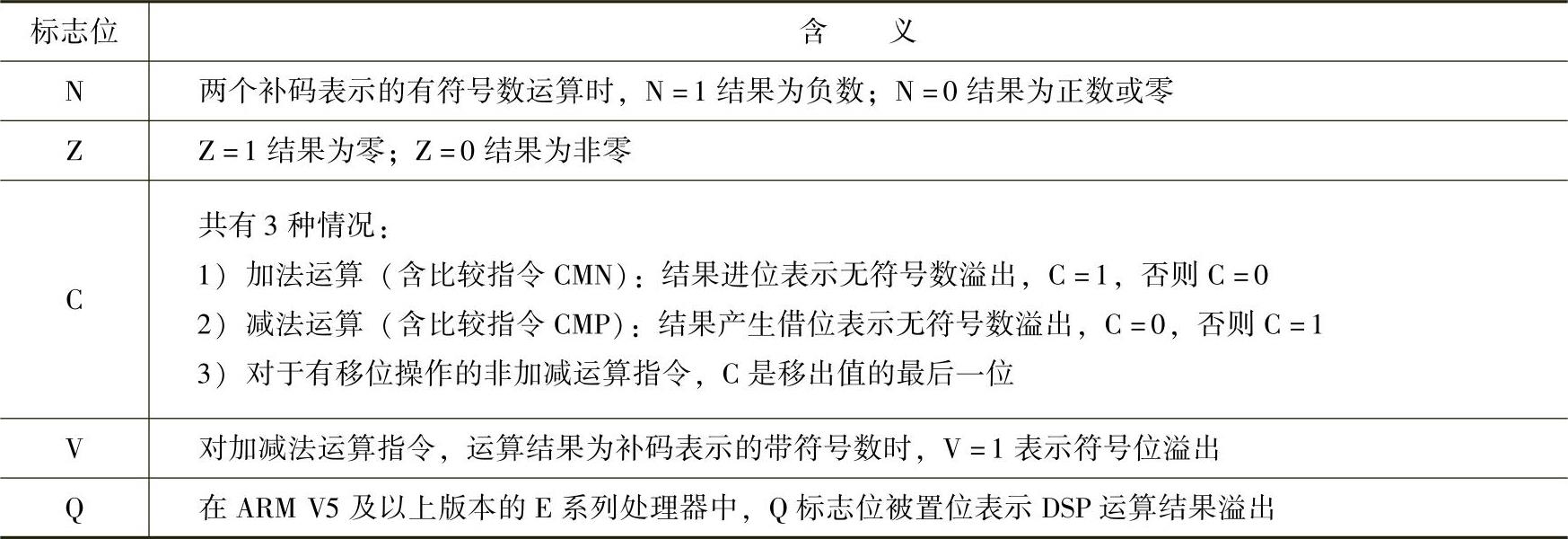

程序状态字条件码标志各位的含义如表9-68所示。

图9-64 程序状态寄存器格式

表9-68 条件码标志的具体含义

PSR的低8位称为控制位,发生异常时改变。处理器运行在特权模式时,这些位可被程序修改。

中断禁止位I、F:I=1表示禁止IRQ中断;F=1表示禁止FIQ中断。

T标志位:该位反映处理器的运行状态。对于AR-体系结构v5及以上的版本的T系列处理器,当该位为0时,运行于AR-状态,否则运行在Thumb状态。

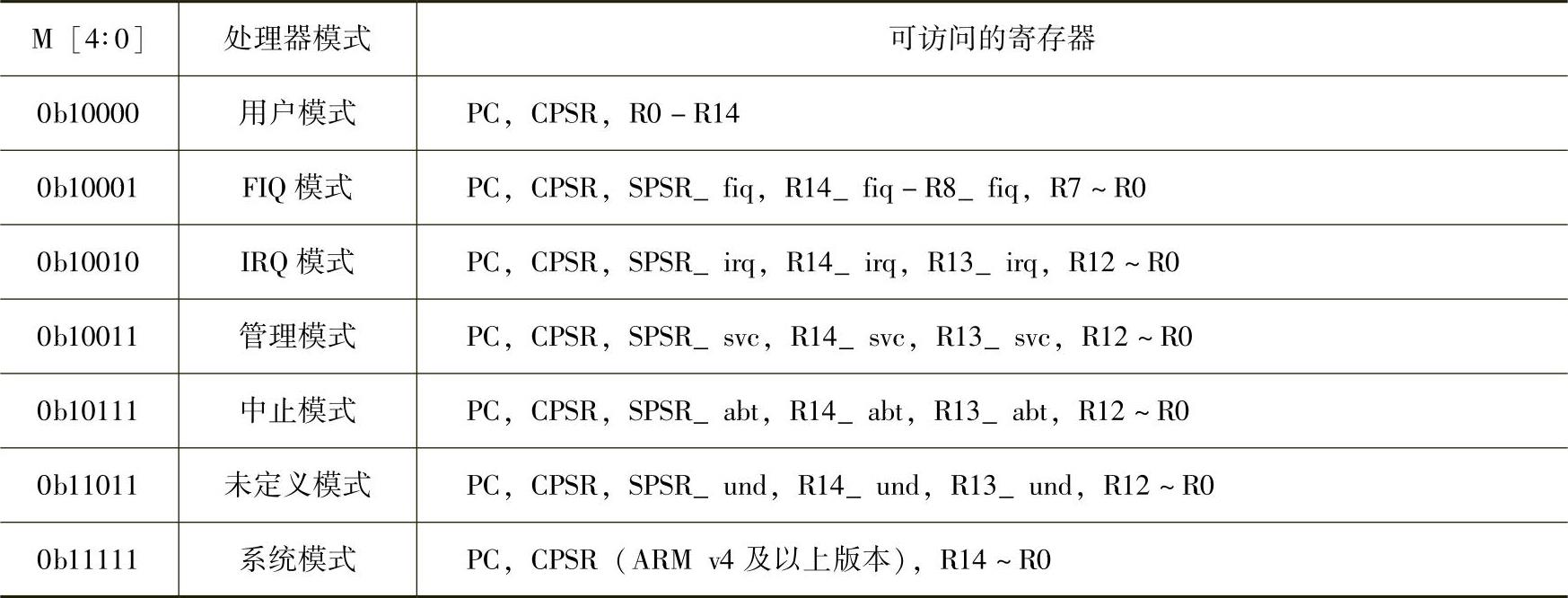

运行模式位-[4∶0]:这些位决定了处理器的运行模式,具体含义如表9-69所示。

表9-69 运行模式位M[4∶0]的具体含义

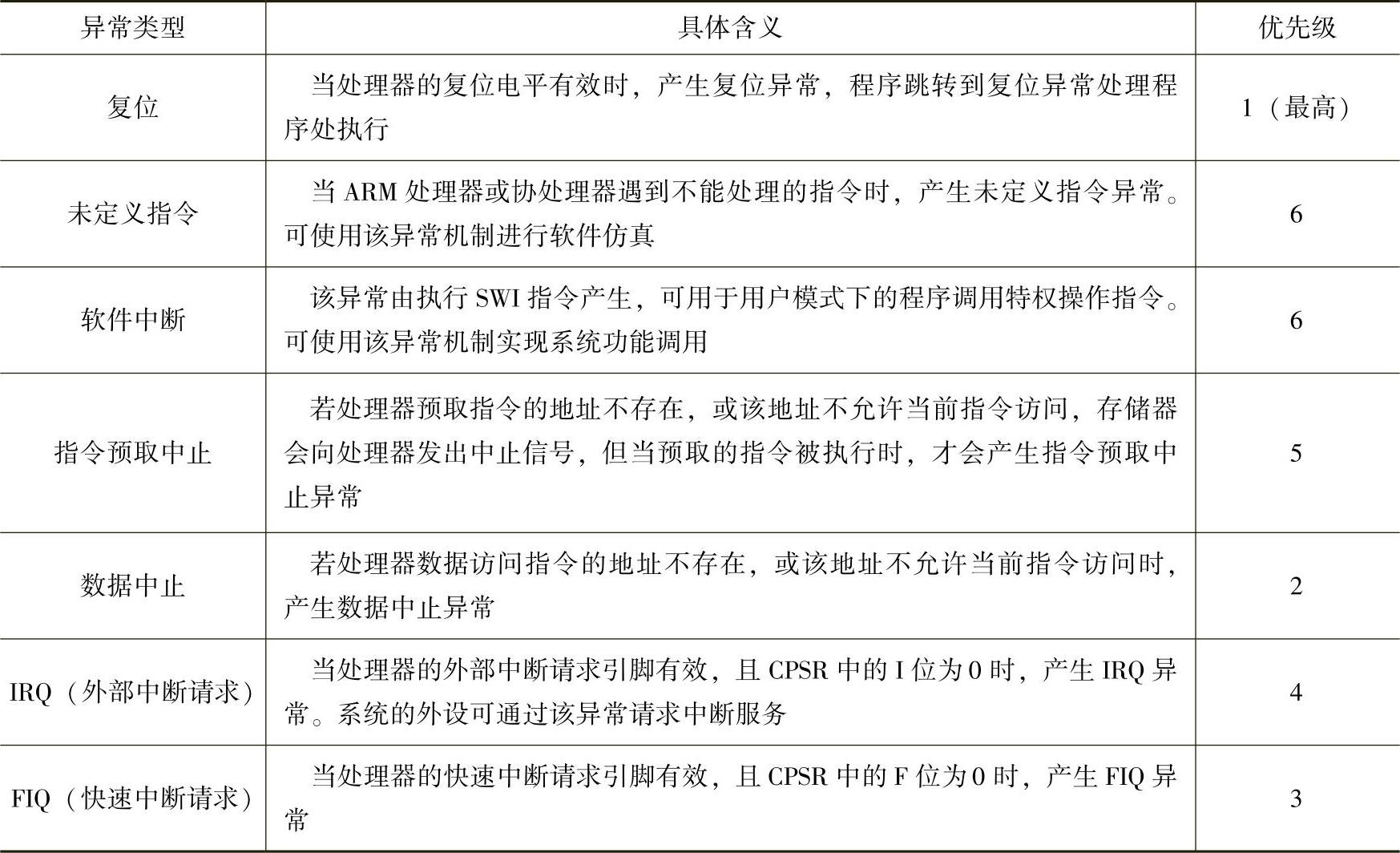

(5)异常(Exceptions) AR-体系结构所支持的异常及具体含义如表9-70所示。

表9-70 ARM体系结构所支持的异常(https://www.xing528.com)

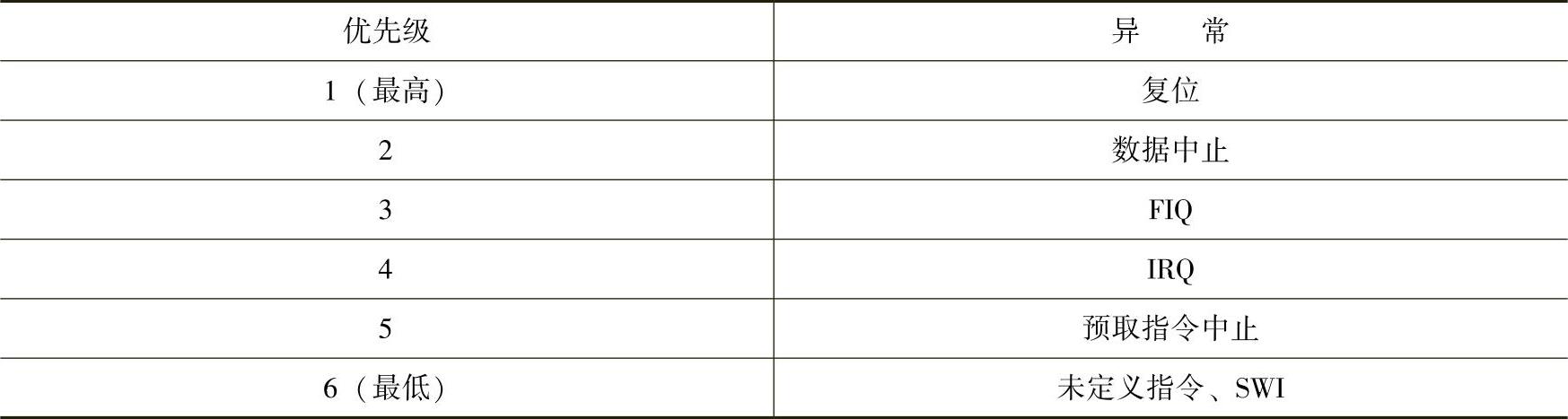

当多个异常同时发生时,系统根据固定的优先级决定异常的处理次序。异常优先级由高到低的排列次序如表9-71所示。

表9-71 异常优先级

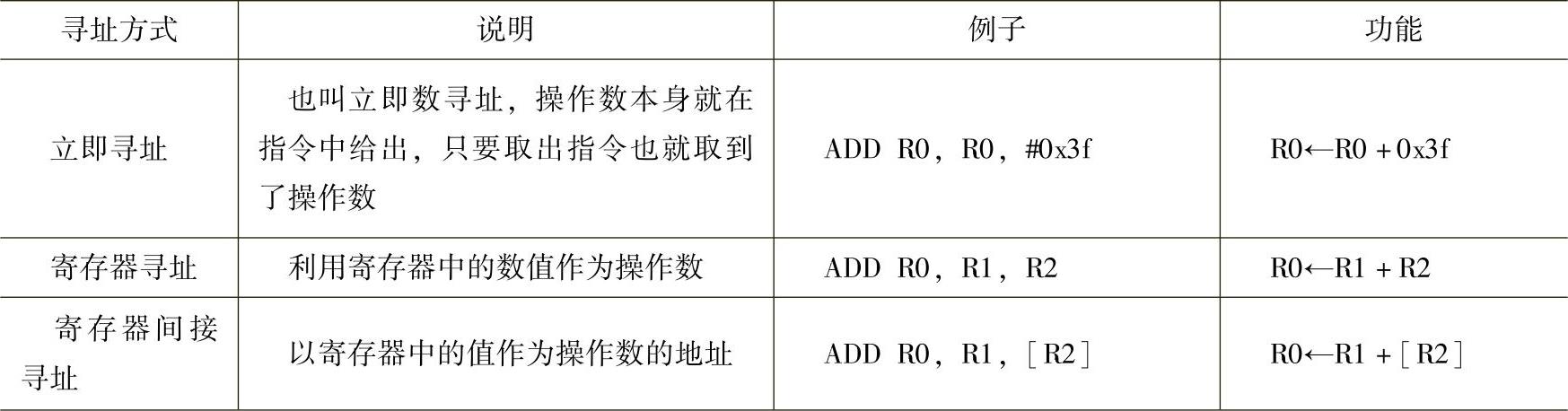

4.寻址方式

AR-寻址方式如表9-72所示。

表9-72 ARM寻址方式

(续)

5.指令集

(1)AR-指令的语法格式:

<opcode>{<cond>}{s}<rd>,<rn>{<operand2>}

opcode:指令助记符;cond:执行条件;S:是否影响CPSR寄存器的值;Rd:目标寄存器;Rn:第1个操作数的寄存器;operand2:第2个操作数。第2个操作数“operand2”可以有多种形式,例如:

1)#immed_8r——常数表达式,必须为8位常数循环右移偶数位的值。

2)Rm——寄存器方式。

3)Rm,shift——寄存器移位方式,移位方法如表9-73所示。

表9-73 移位方法

(2)AR-指令集 AR-指令集由数据处理指令、跳转指令、Load/Store指令、程序状态寄存器指令、协处理器指令和软件中断指令六大类构成。

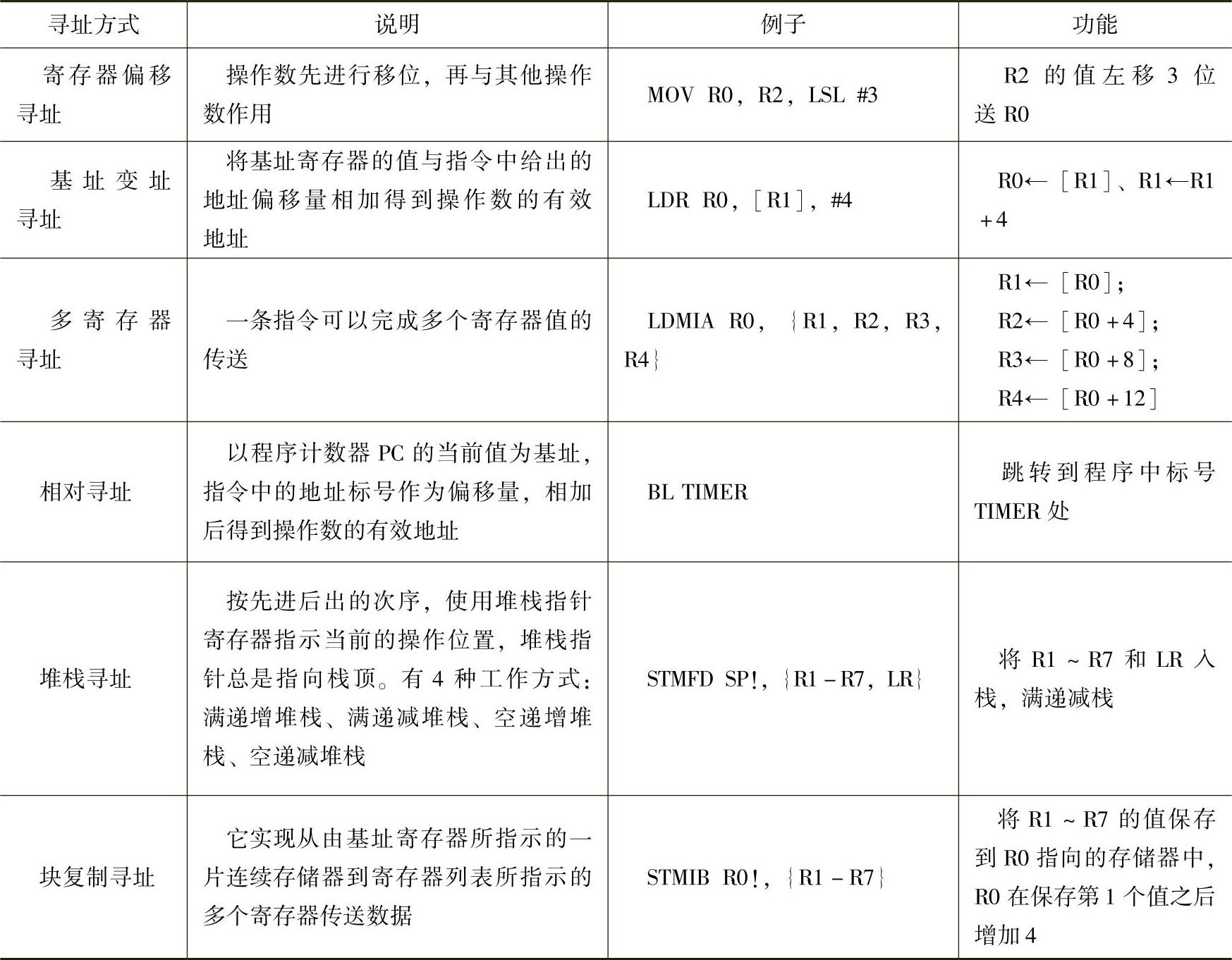

1)数据处理指令见表9-74。

表9-74 数据处理指令

(续)

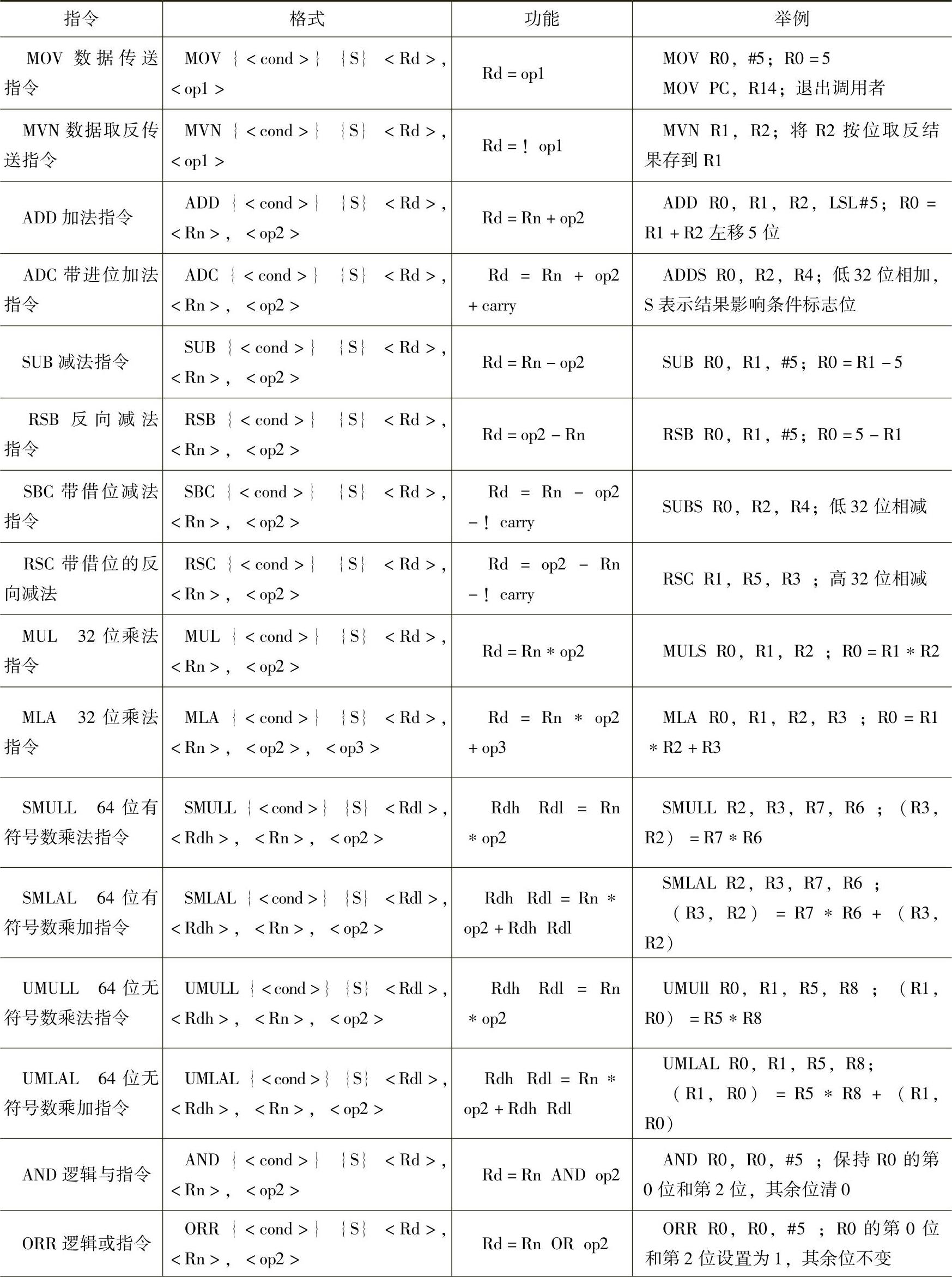

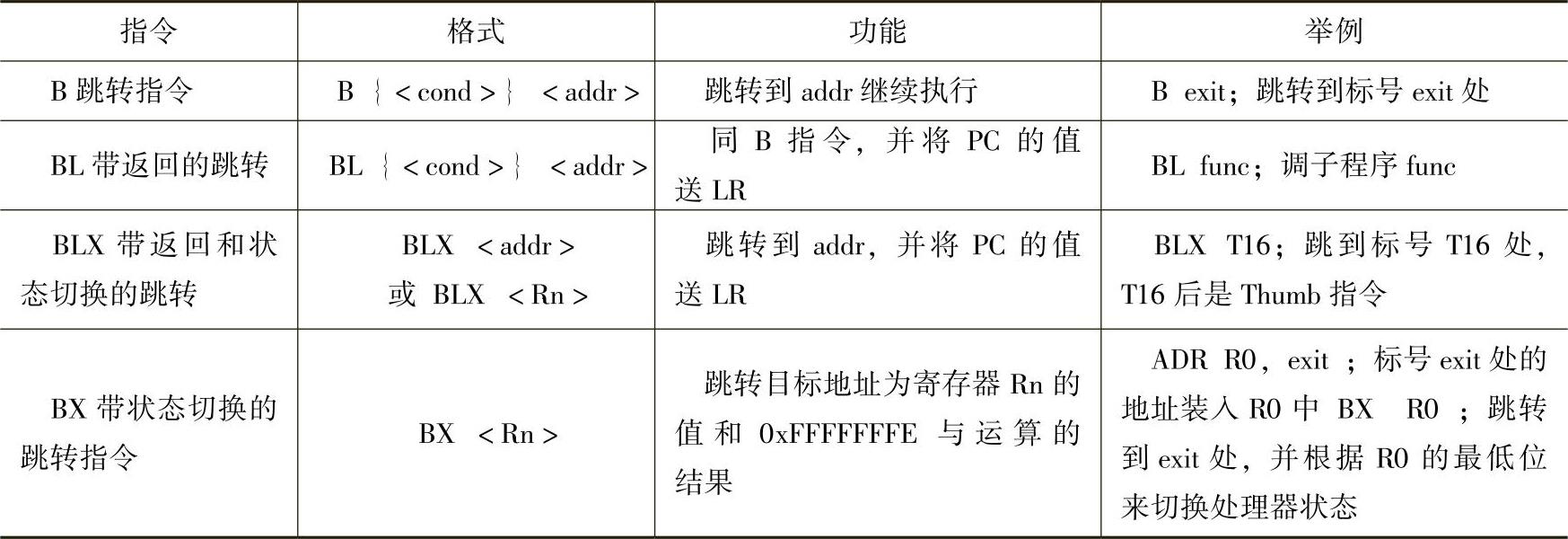

2)跳转指令见表9-75。

表9-75 跳转指令

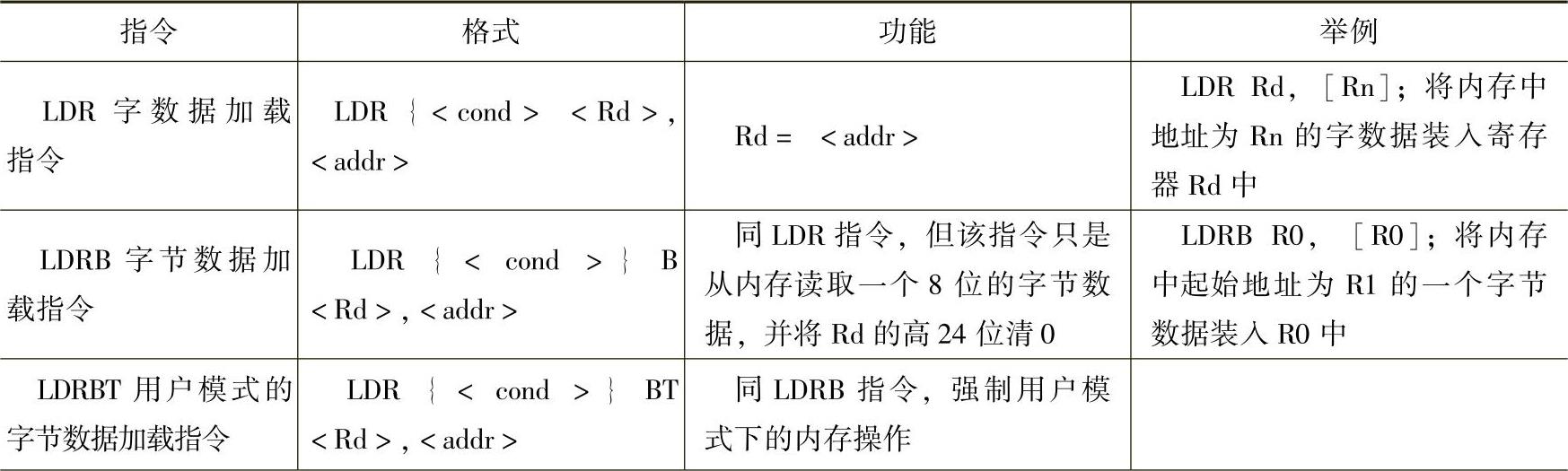

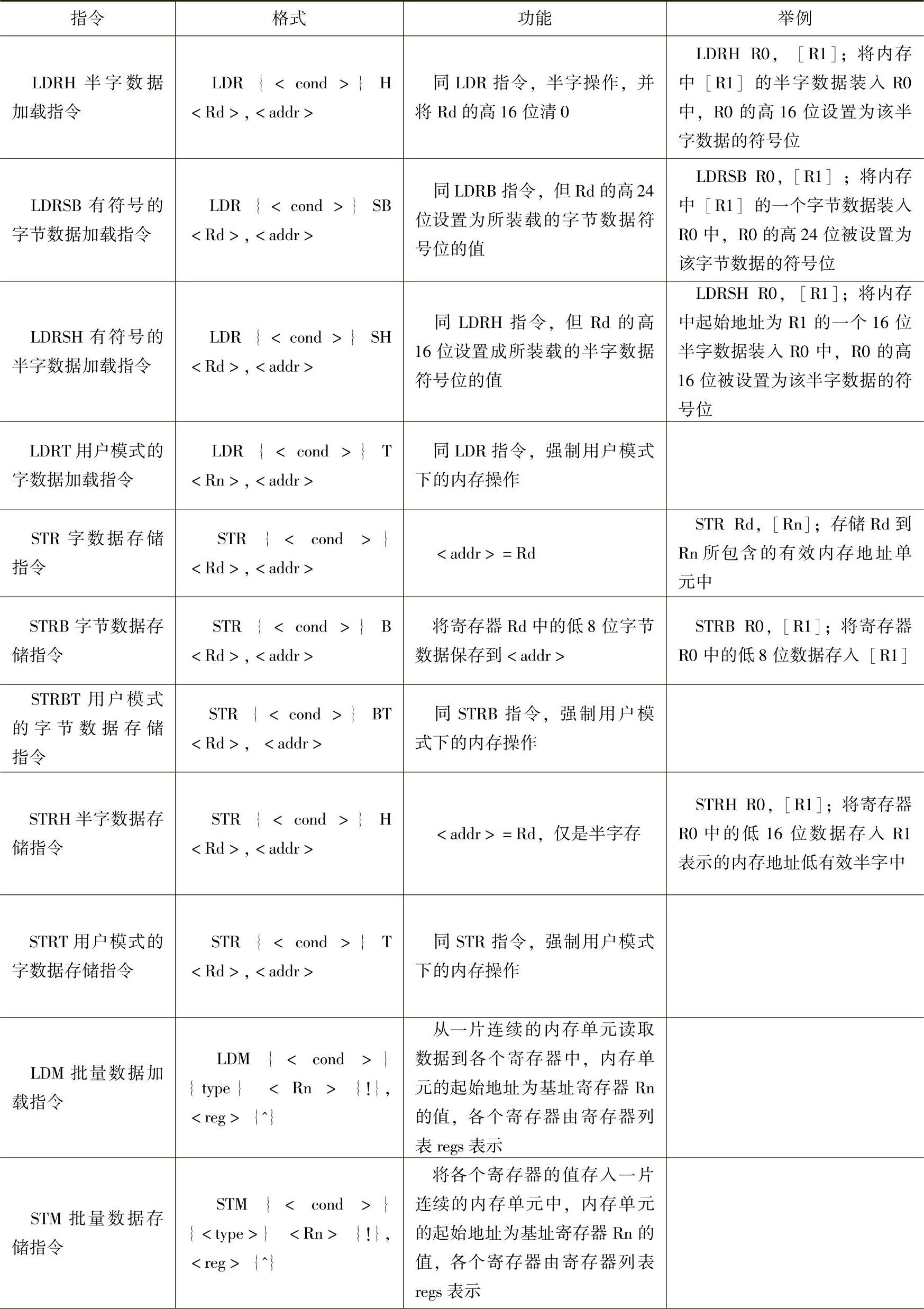

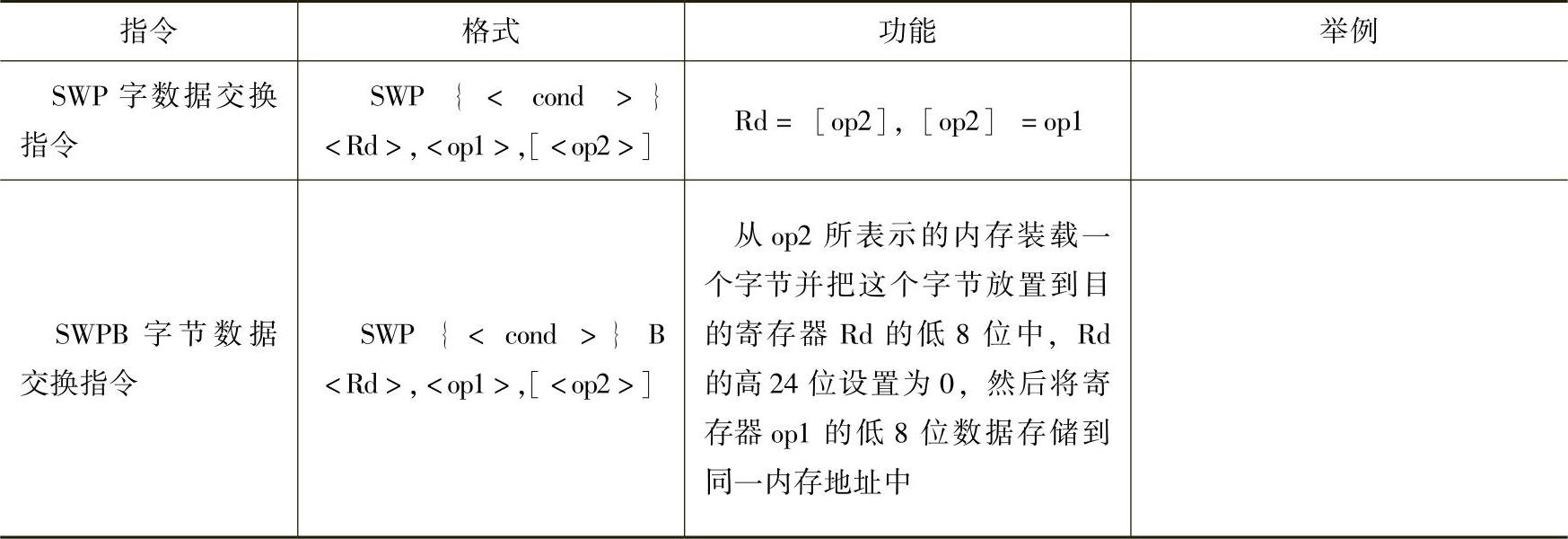

3)Load/Store指令见表9-76。

表9-76 Load/Store指令

(续)

(续)

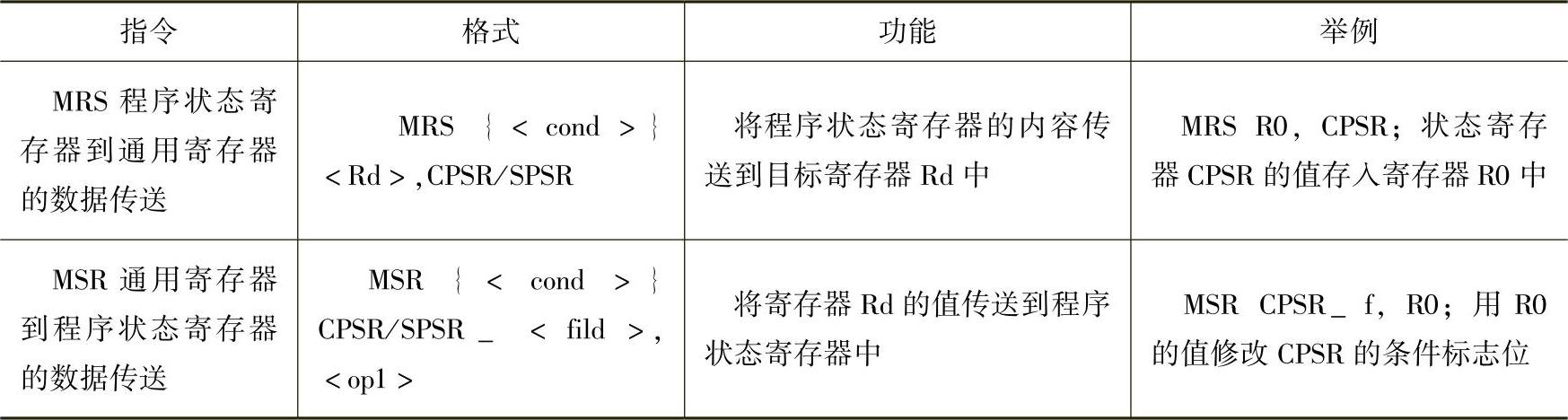

4)程序状态寄存器指令见表9-77。

表9-77 程序状态寄存器指令

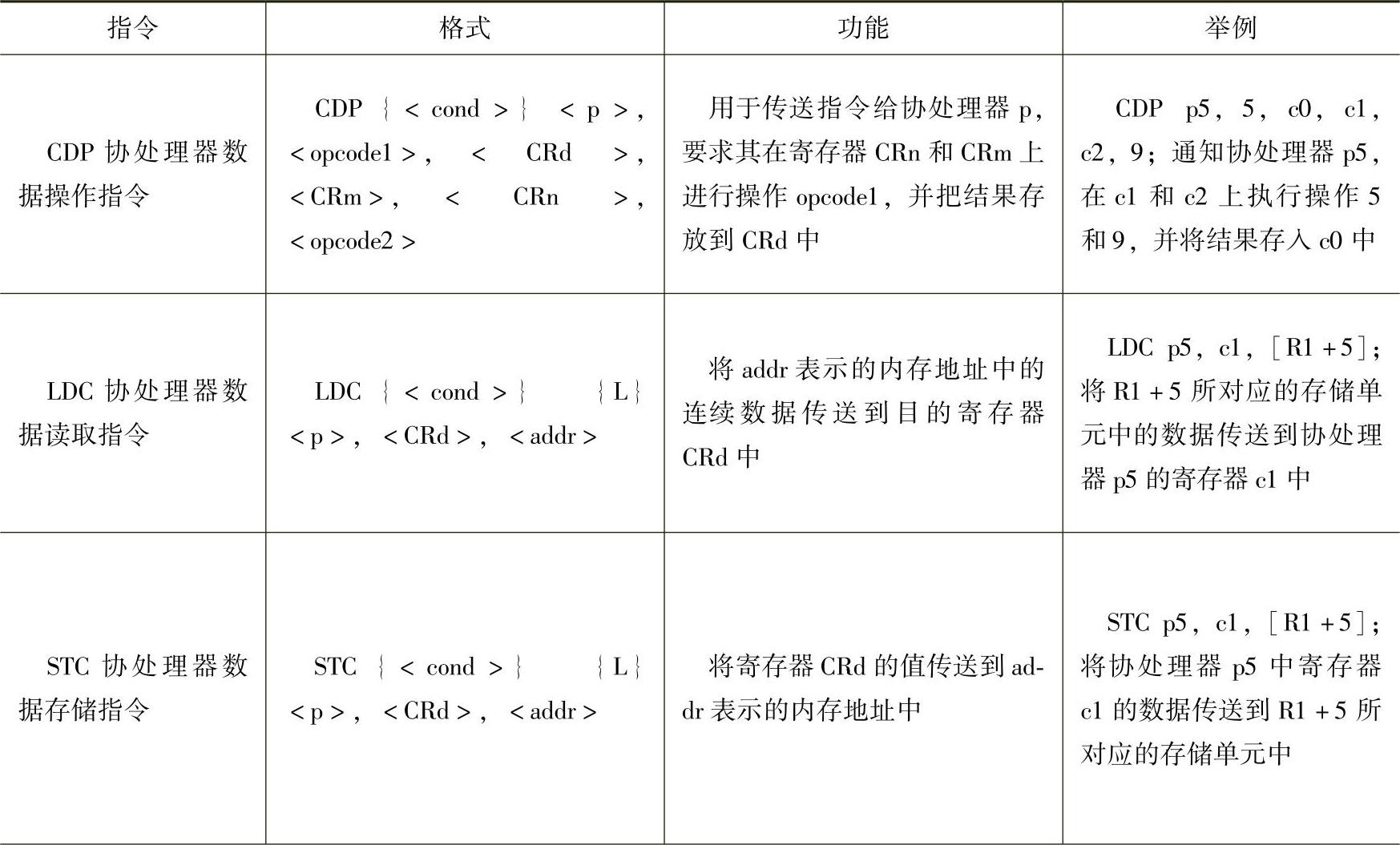

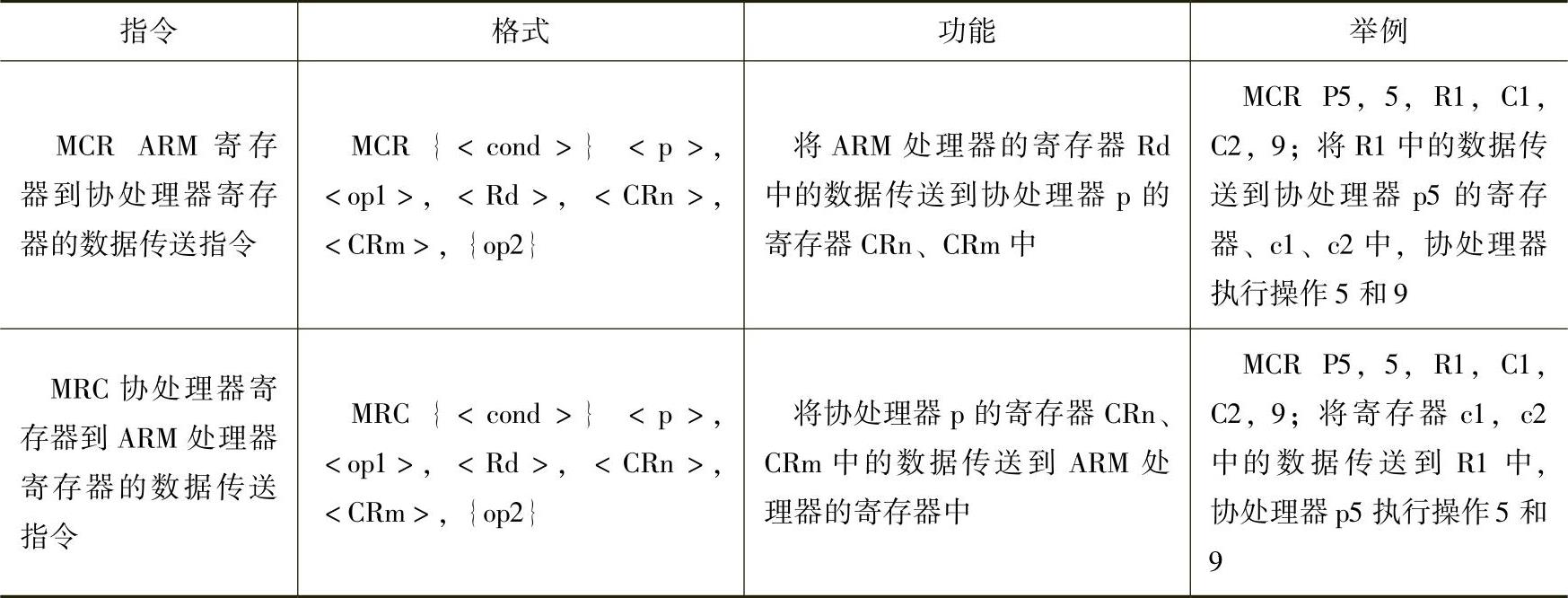

5)协处理器指令见表9-78。

表9-78 协处理器指令

(续)

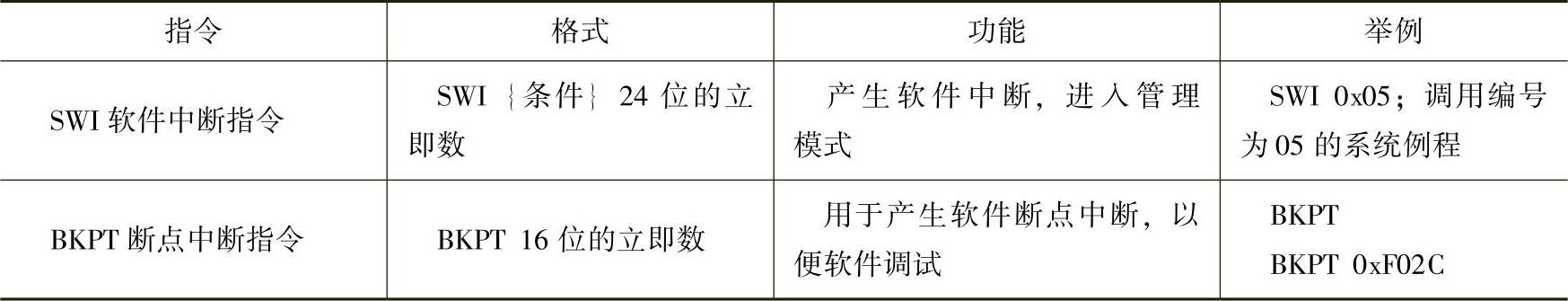

6)异常中断指令见表9-79。

表9-79 异常中断指令

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。