在对项目进行电路仿真之前,我们首先需要对FPGA项目的有关属性进行设置,然后进行编译。

1.属性设置

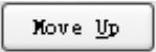

1)打开项目中的任意一个VHDL文件或电路原理图文件,选择菜单命令“工程”→“工程序列”,弹出项目顺序选择对话框,如图14-19所示。

在该对话框中列出了当前项目的所有源文件。由于系统的编译器是按照自下而上的顺序进行编译的,因此要把最早编译的文件放在最下面,把最晚编译的文件放在最上面。用户可以通过 和

和 两个按钮调换文件的位置。

两个按钮调换文件的位置。

若一个设计项目中包含大量的文件,手工调整起来比较麻烦,可以由系统在编译时自动调整。

图14-19 项目顺序选择对话框

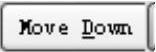

2)选择菜单命令“工具”→“FPGA参数”,弹出“参数选择”对话框,单击该对话框中的“Simulation Compiler”(仿真编译器)标签,打开“Simulation Compiler”(仿真编译器)选项卡,如图14-20所示。

图14-20 “Simulation Compiler”(仿真编译器)选项卡

在该选项卡中,选中 复选框,则系统在编译时会自动调整各个文件的编译顺序。

复选框,则系统在编译时会自动调整各个文件的编译顺序。

3)选择菜单命令“工程”→“工程参数”,在打开的对话框中单击“仿真”标签,打开“仿真”选项卡,如图14-21所示。

(https://www.xing528.com)

(https://www.xing528.com)

图14-21 “仿真”选项卡

在该选项卡中,可以设置电路仿真时的各种属性。本例中,在“Testbench文档”(测试台文件)下拉列表框中显示“Test_TBarLedWindow.VHDTST”项;在“顶层实体/模块/配置”栏中显示“TestTBarLedWindow”;在“结构体系”栏中显示“stimulus”;在“SDF优化”下拉列表框中选择“Avg”项。

2.编译项目

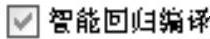

1)选择菜单命令“工程”→“Compile FPGA Project TBarLedWindow.PRJFPG”(编译工程文件),系统对该文件进行编译,结果如图14-22所示。

图14-22 编译生成层次电路

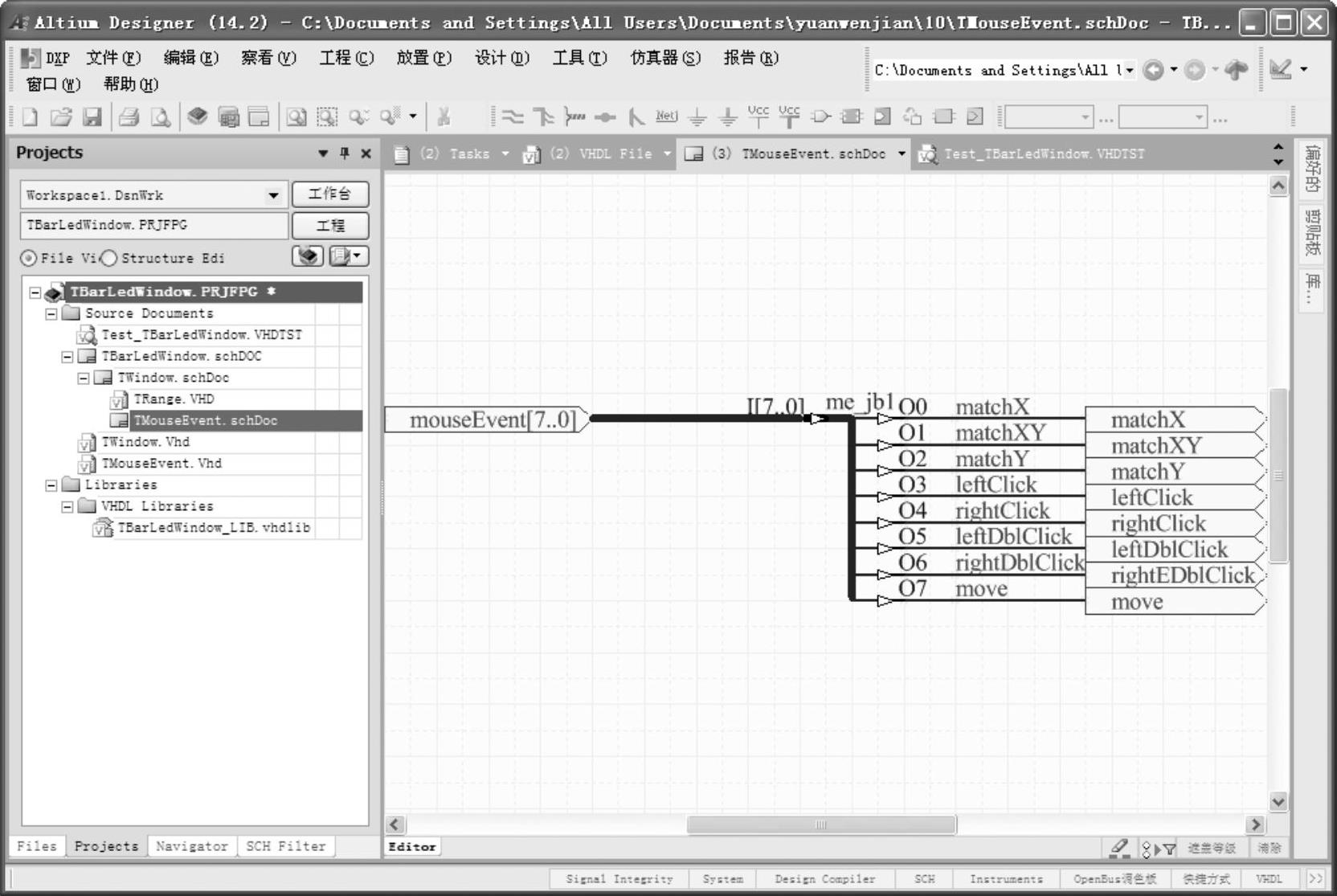

2)编译结束后,打开“Message(信息)”面板,查看编译的详细信息,如图14-23所示。

图14-23 文件的编译信息

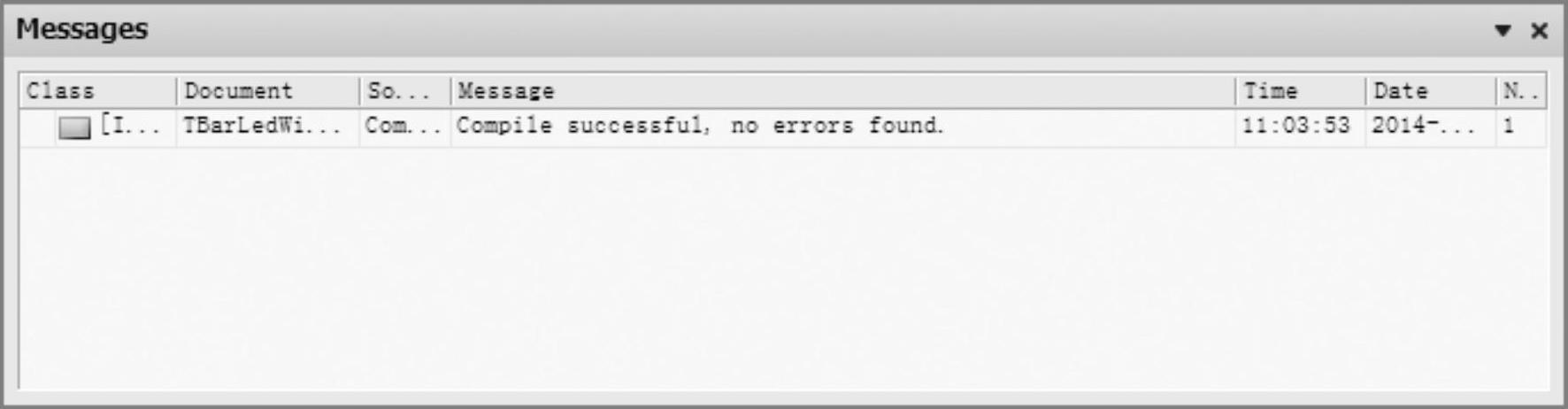

3)选择菜单命令“仿真器”→“创建VHDL测试平台”,系统对整个项目进行编译。编译完成后,系统自动生成一个VHDTST文件“Test_tmouseevent.VHDTST”,如图14-24所示。

图14-24 生成的“Test_tmouseevent.VHDTST”文件

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。