在对信号完整性分析的有关规则及元件的SI模型设定有了初步了解以后,下面来看一下如何进行基本的信号完整性分析。在这种分析中,所涉及到的一种重要工具就是信号完整性分析器。

信号完整性分析可以分为两步进行,第一步是对所有可能需要进行分析的网络进行一次初步的分析,从中可以了解到哪些网络的信号完整性最差;第二步是筛选出一些信号进行进一步的分析。这两步的具体实现都是在信号完整性分析器中进行的。

Altium Designer 14提供了一个高级的信号完整性分析器,能精确地模拟分析已布线的PCB,可以测试网络阻抗、反冲、过冲、信号斜率等。其设置方式与PCB设计规则一样,首先启动信号完整性分析器,再打开某一项目的某一PCB文件,选择菜单栏中的“工具”→“信号完整性”命令,系统开始运行信号完整性分析器。

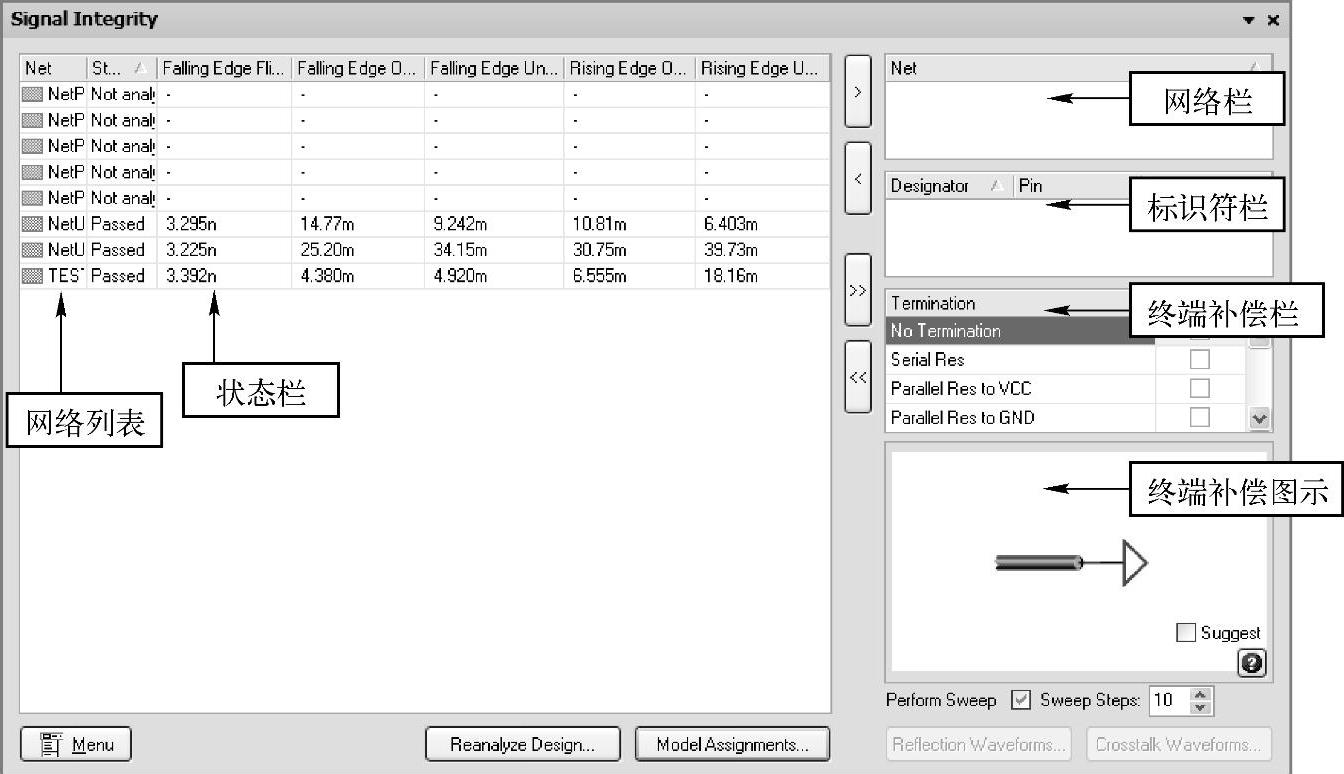

信号完整性分析器界面如图13-21所示,主要由以下几部分组成:

图13-21 信号完整性分析器界面

1.网络列表

网络列表中列出了PCB文件中所有可能需要进行分析的网络。在分析之前,可以选中需要进一步分析的网络,单击 按钮添加到右侧的“Net”(网络)栏中。

按钮添加到右侧的“Net”(网络)栏中。

2.状态栏

用于显示对某个网络进行信号完整性分析后的状态,包括以下3种状态:

●Passed(通过):表示通过,没有问题。

●Not analyzed(无法分析):表明由于某种原因导致对该信号的分析无法进行。

●Failed(失败):分析失败。

3.标识符栏

用于显示在“网络”栏中选定的网络所连接元件的引脚及信号的方向。

4.终端补偿栏

在Altium Designer 14中,对PCB进行信号完整性分析时,还需要对线路上的信号进行终端补偿的测试。其目的是测试传输线中信号的反射与串扰,以便使PCB中的线路信号达到最优。

在“终端补偿”栏中,系统提供了8种信号终端补偿方式,相应的图示显示在下面的图示栏中。

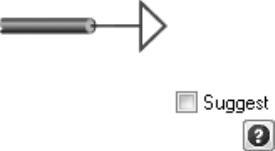

(1)No Termination(无终端补偿)

该补偿方式如图13-22所示,即直接进行信号传输,对终端不进行补偿,是系统的默认方式。

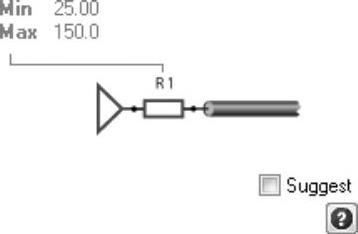

(2)Serial Res(串阻补偿)

该补偿方式如图13-23所示,即在点对点的连接方式中,直接串入一个电阻,以降低外部电压信号的幅值,合适的串阻补偿将使得信号正确传输到接收端,消除接收端的过冲现象。

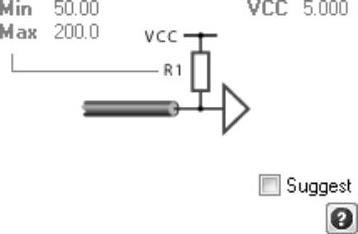

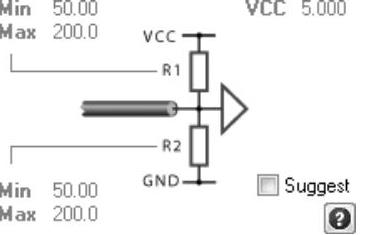

(3)Parallel Res to VCC(电源VCC端并阻补偿)

在电源VCC输出端并联的电阻是和传输线阻抗相匹配的,对于线路的信号反射,这是一种比较好的补偿方式,如图13-24所示。由于该电阻上会有电流通过,因此将增加电源的消耗,导致低电平阀值的升高。该阀值会根据电阻值的变化而变化,有可能会超出在数据区定义的操作条件。

(4)Parallel Res to GND(接地端并阻补偿)

该补偿方式如图13-25所示,在接地输入端并联的电阻是和传输线阻抗相匹配的,与电源VCC端并阻补偿方式类似,这也是一种比较好的补偿线路信号反射的方法。同样,由于有电流通过,会导致高电平阀值的降低。

图13-22 无终端补偿方式

图13-23 串阻补偿方式

图13-24 电源VCC端并阻补偿方式

图13-25 接地端并阻补偿方式

(5)Parallel Res to VCC&GND(电源端与接地端同时并阻补偿)

该补偿方式如图13-26所示,将电源端并阻补偿与接地端并阻补偿结合起来使用。适用于TTL总线系统,而对于CMOS总线系统则一般不建议使用。

由于该补偿方式相当于在电源与地之间直接接入了一个电阻,通过的电流将比较大,因此对于两电阻的阻值应折中分配,以防电流过大。

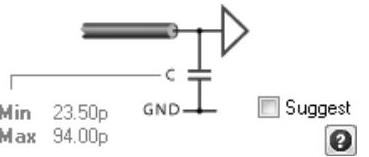

(6)Parallel Cap to GND(接地端并联电容补偿)(https://www.xing528.com)

该补偿方式如图13-27所示,即在信号接收端对地并联一个电容,可以降低信号噪声。该补偿方式是制作PCB印制板时最常用的方式,能够有效地消除铜膜导线在走线拐弯处所引起的波形畸变。最大的缺点是,波形的上升沿或下降沿会变得过于平坦,导致上升时间和下降时间增加。

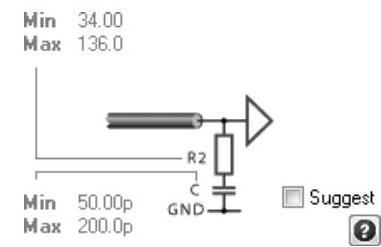

(7)Res and Cap to GND(接地端并阻、并容补偿)

该补偿方式如图13-28所示,即在接收输入端对地并联一个电容和一个电阻,与接地端仅仅并联电容的补偿效果基本一样,只不过在补偿网络中不再有直流电流通过。而且与地端仅仅并联电阻的补偿方式相比,能够使得线路信号的边沿比较平坦。

在大多数情况下,当时间常数RC大约为延迟时间的4倍时,这种补偿方式可以使传输线上的信号充分终止。

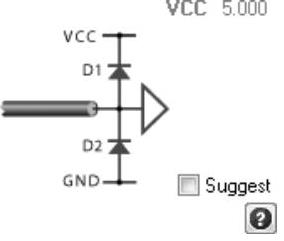

(8)Parallel Schottky Diode(并联肖特基二极管补偿)

该补偿方式如图13-29所示,在传输线补偿端的电源和地端并联肖特基二极管可以减小接收端信号的过冲和下冲值。大多数标准逻辑集成电路的输入电路都采用了这种补偿方式。

图13-26 电源端与接地端同时并阻补偿方

图13-27 接地端并联电容补偿方式

图13-28 接地端并阻、并容补偿方式

图13-29 并联肖特基二极管补偿方式

5.“执行扫描”复选框

若勾选该复选框,则信号分析时会按照用户所设置的参数范围,对整个系统的信号完整性进行扫描,类似于电路原理图仿真中的参数扫描方式。扫描步数可以在后面进行设置,一般应勾选该复选框,扫描步数采用系统默认值即可。

6.“菜单”按钮

图13-30 “菜单”菜单

单击该按钮,系统将弹出如图13-30所示的“菜单”菜单,其中各命令的功能如下:

●Select Net(选择网络):选择该命令,系统会将选中的网络添加到右侧的网络栏内。

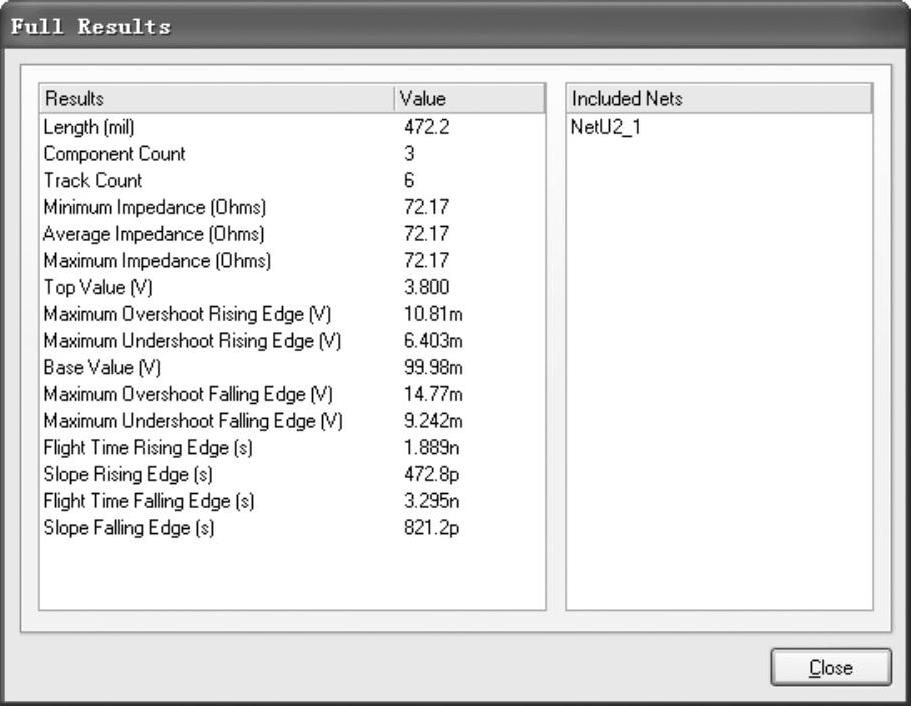

●Details(详细资料):选择该命令,系统将弹出如图13-31所示的“Full Results”(全部结果)对话框,显示在网络列表中所选的网络详细分析情况,包括元件个数、导线条数,以及根据所设定的分析规则得出的各项参数等。

●Find Coupled Nets(找到关联网络):选择该命令,可以查找所有与选中的网络有关联的网络,并高亮显示。

●Cross Probe(通过探查):包括“To Schematic”(到原理图)和“To PCB”(到PCB)两个子命令,分别用于在原理图中或者在PCB文件中查找所选中的网络。

●Copy(复制):复制所选中的网络,包括“Select”(选择)和“All”(所有)两个子命令,分别用于复制选中的网络和选中所有网络。

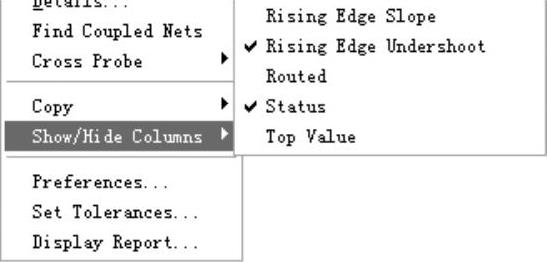

●Show/Hidd Columns(显示/隐藏纵队):该命令用于在网络列表栏中显示或者隐藏一些分析数据列。“Show/Hidd Columns”(显示/隐藏纵队)子菜单如图13-32所示。

图13-31 “Full Results”对话框

图13-32 “Show/Hidd Columns”子菜单

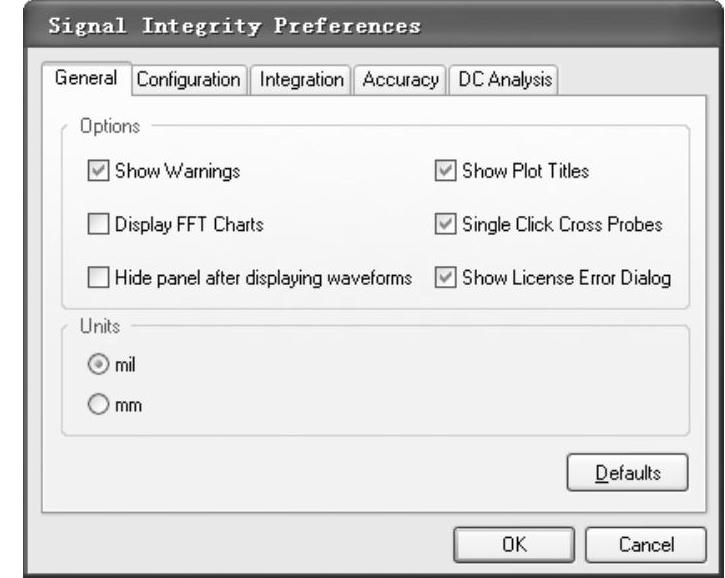

图13-33 “信号完整性参数选项”对话框

●Preferences(参数):选择该命令,用户可以在弹出的“Signal Integrity Preferences”(信号完整性首选项)对话框中设置信号完整性分析的相关选项,如图13-33所示。该对话框中包含若干选项卡,对应不同的设置内容。在信号完整性分析中,主要用到的是“Configuration”(配置)选项卡,用于设置信号完整性分析的时间及步长。

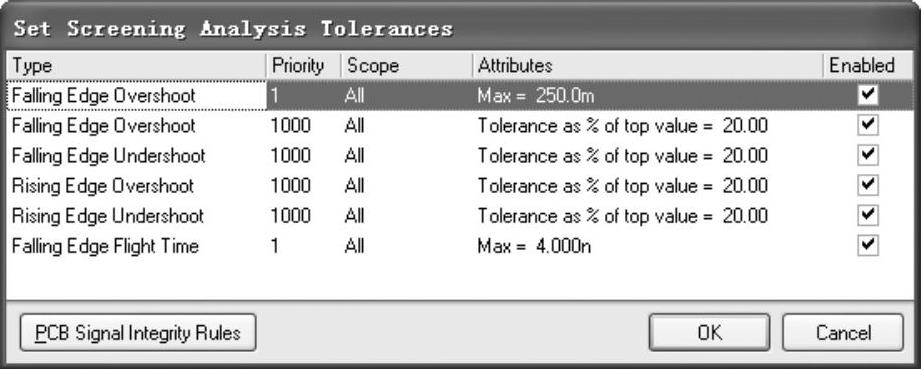

●Set Tolerances(设置公差):选择该命令后,系统将弹出如图13-34所示的“Set Screen-ing Analysis Tolerance”对话框。公差(Tol-erance)用于限定一个误差范围,代表了允许信号变形的最大值和最小值。将实际信号的误差值与这个范围相比较,就可以查看信号的误差是否合乎要求。对于显示状态为“Failed”(失败)的信号,其主要原因是信号超出了误差限定的范围。因此在进行进一步分析之前,应先检查公差限定是否太过严格。

图13-34 “设置扫描分析公差”对话框

●Display Report(显示报表):用于显示信号完整性分析报表。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。