Altium Designer 14中包含了许多信号完整性分析的规则,这些规则用于在PCB设计中检测一些潜在的信号完整性问题。

在Altium Designer 14的PCB编辑环境中,选择菜单栏中的“设计”→“规则”命令,系统将弹出“PCB规则及约束编辑器”对话框。在该对话框中单击“Design Rules”(设计规则)前面的 按钮,选择其中的“Signal Integrity”选项,即可看到如图13-1所示的各种信号完整性分析选项,可以根据设计工作的要求选择所需的规则进行设置。

按钮,选择其中的“Signal Integrity”选项,即可看到如图13-1所示的各种信号完整性分析选项,可以根据设计工作的要求选择所需的规则进行设置。

图13-1 “PCB规则及约束编辑器”对话框

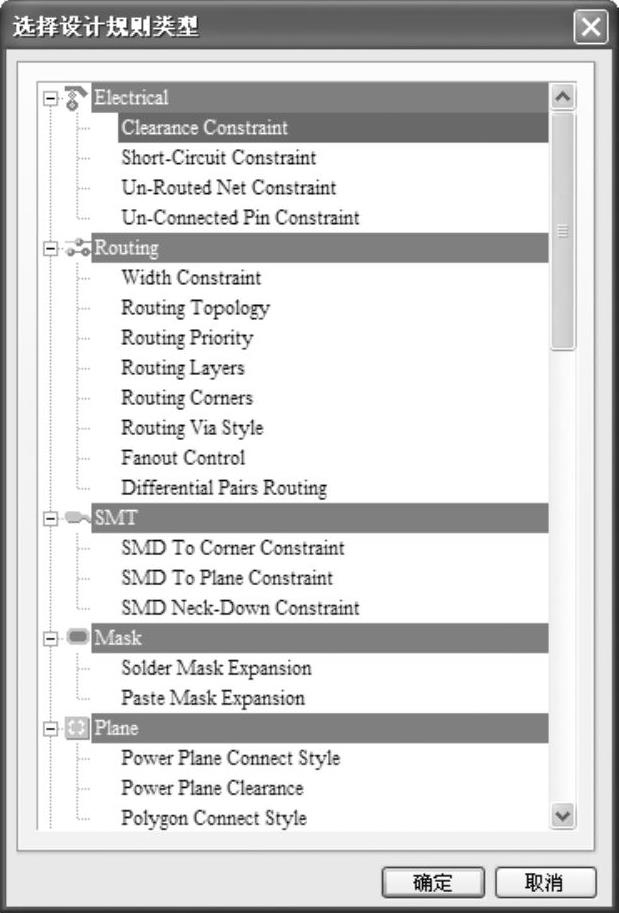

在“PCB规则及约束编辑器”对话框中列出了Altium Designer 14提供的所有设计规则,但仅列出了可以使用的规则,要想在DRC校验时真正使用这些规则,还需要在第一次使用时,把该规则作为新规则添加到实际使用的规则库中。在需要使用的规则上右键单击鼠标,在弹出的右键快捷菜单中选择“新规则”命令,即可把该规则添加到实际使用的规则库中。如果需要多次使用该规则,可以为其建立多个新的规则,并用不同的名称加以区别。要想在实际使用的规则库中删除某个规则,可以右键单击该规则,在弹出的右键快捷菜单中选择“删除规则”命令,即可从实际使用的规则库中删除该规则。在右键快捷菜单中选择“Export Rules”(输出规则)命令,可以把选中的规则从实际使用的规则库中导出。在右键快捷菜单中选择“Import Rules”(输入规则)命令,系统将弹出如图13-2所示的“选择设计规则类型”对话框,可以从设计规则库中导入所需的规则。在右键快捷菜单中选择“Report”(报表)命令,则为该规则建立相应的报表文件,并可以打印输出。

图13-2 “选择设计规则类型”对话框

在Altium Designer 14中包含13条信号完整性分析的规则,下面分别介绍。

(1)Signal Stimulus(激励信号)规则

在“Signal Integrity”选项上右键单击鼠标,在弹出的右键快捷菜单中选择“新规则”命令,生成“Signal Stimulus”(激励信号)规则选项,单击该规则,弹出如图13-3所示的“Signal Stimulus”(激励信号)规则的设置页面。在该页面中可以设置激励信号的各项参数。

图13-3 “Signal Stimulus”(激励信号)规则的设置页面

1)“名称”文本框:用于为该规则设立一个便于理解的名字,在DRC校验中,当电路板布线违反该规则时,就将以该参数名称显示此错误。

2)“注释”文本框:设置该规则的注释说明。

3)“唯一ID”文本框:为该参数提供一个随机的ID号。

4)“Where The First Object Matches(优先匹配对象的位置)”选项组:用于设置激励信号规则优先匹配对象的所属范围。共有6个选项,其含义如下:

●“所有”:整个PCB范围。

●“网络”:指定网络。

●“网络类”:指定网络类。

●“层”:指定工作层。

●“网络和层”:指定网络及工作层。

●“高级的”:高级设置选项。单击该单选钮后,可以单击其右侧的“查询构建器”按钮,通过查询条件确定应用范围。

5)“约束”选项组:用于设置激励信号的约束规则。共有5个选项,其含义如下:

●“激励类型”:用于设置激励信号的种类。包括3个选项,“Constant Level(固定电平)”表示激励信号为某个固定电平;“Single Pulse(单脉冲)”表示激励信号为单脉冲信号;“Periodic Pulse(周期脉冲)”表示激励信号为周期性脉冲信号。

●“开始级别”:用于设置激励信号的初始电平,仅对Single Pulse(单脉冲)和“Peri-odic Pulse”(周期脉冲)有效。设置初始电平为低电平时,选择Low Level(低电平);设置初始电平为高电平时,选择High Level(高电平)。

●“开始时间”:用于设置激励信号高电平脉宽的起始时间。

●“停止时间”:用于设置激励信号高电平脉宽的终止时间。

●“时间周期”:用于设置激励信号的周期。

在设置激励信号的时间参数时,要注意添加单位,以免设置出错。

(2)Overshoot-Falling Edge(信号下降沿的过冲)规则

图13-4 “Overshoot-Falling Edge”规则设置页面

信号下降沿的过冲定义了信号下降边沿允许的最大过冲量,即信号下降沿低于信号基准值的最大阻尼振荡,系统默认的单位是伏特(Volts)。“Overshoot-Falling Edge(信号下降沿的过冲)”规则的设置页面如图13-4所示。

(3)Overshoot-Rising Edge(信号上升沿的过冲)规则

信号上升沿的过冲与信号下降沿的过冲是相对应的,它定义了信号上升沿允许的最大过冲量,即信号上升沿高于信号高电平值的最大阻尼振荡,系统默认的单位是伏特(Volts)。“Overshoot-Rising Edge(信号上升沿的过冲)”规则设置页面如图13-5所示。

(4)Undershoot-Falling Edge(信号下降沿的反冲)规则

信号反冲与信号过冲略有区别。信号下降沿的反冲定义了信号下降边沿允许的最大反冲量,即信号下降沿高于信号基准值(低电平)的阻尼振荡,系统默认的单位是伏特(Volts)。“Undershoot-Falling Edge”(信号下降沿的反冲)规则设置页面如图13-6所示。

(https://www.xing528.com)

(https://www.xing528.com)

图13-5 “Overshoot-Rising Edge”规则设置页面

图13-6 “Undershoot-Falling Edge”规则设置页面

(5)Undershoot-Rising Edge(信号上升沿的反冲)规则信号上升沿的反冲与信号下降沿的反冲是相对应的,它定义了信号上升沿允许的最大反冲值,即信号上升沿低于信号高电平值的阻尼振荡,系统默认的单位是伏特(Volts)。“Undershoot-Rising Edge”(信号上升沿的反冲)规则设置页面如图13-7所示。

(6)Impedance(阻抗约束)规则

阻抗约束定义了电路板上所允许的电阻的最大和最小值,系统默认的单位是欧姆(Ω)。阻抗和导体的几何外观及电导率、导体外的绝缘层材料及电路板的几何物理分布,以及导体间在Z平面域的距离相关。其中绝缘层材料包括电路板的基本材料、工作层间的绝缘层及焊接材料等。

图13-7 “Undershoot-Rising Edge”规则设置页面

(7)Signal Top Value(信号高电平)规则

信号高电平定义了线路上信号在高电平状态下所允许的最低稳定电压值,即信号高电平的最低稳定电压,系统默认的单位是伏特(Volts)。“Signal Top Value”(信号高电平)规则设置页面如图13-8所示。

(8)Signal Base Value(信号基准值)规则

信号基准值与信号高电平是相对应的,它定义了线路上信号在低电平状态下所允许的最高稳定电压值,即信号低电平的最高稳定电压值,系统默认的单位是伏特(Volts)。“Signal Base Value”(信号基准值)规则设置页面如图13-9所示。

图13-8 “Signal Top Value”规则设置页面

图13-9 “Signal Base Value”规则设置页面

(9)Flight Time-Rising Edge(上升沿的上升时间)规则

上升沿的上升时间定义了信号上升沿允许的最大上升时间,即信号上升沿到达信号幅度值的50%时所需的时间,系统默认的单位是秒(seconds)。“Flight Time-Rising Edge”(上升沿的上升时间)规则设置页面如图13-10所示。

(10)Flight Time-Falling Edge(下降沿的下降时间)规则

下降沿的下降时间是由相互连接电路单元引起的时间延迟,它实际是信号电压降低到门限电压(由高电平变为低电平的过程中)所需要的时间。该时间远小于在该网络的输出端直接连接一个参考负载时信号电平降低到门限电压所需要的时间。

下降沿的下降时间与上升沿的上升时间是相对应的,它定义了信号下降边沿允许的最大下降时间,即信号下降边沿到达信号幅度值的50%时所需的时间,系统默认的单位是秒(seconds)。“Flight Time-Falling Edge”(下降沿的下降时间)规则设置页面如图13-11所示。

图13-10 “Flight Time-Rising Edge”规则设置页面

图13-11 “Flight Time-Falling Edge”规则设置页面

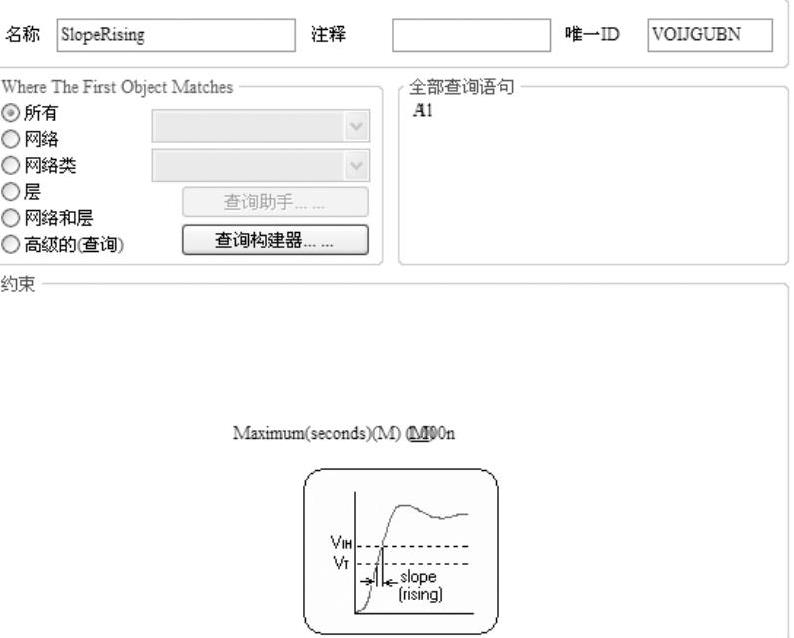

(11)Slope-Rising Edge(上升沿斜率)规则

上升沿斜率定义了信号从门限电压上升到一个有效的高电平时所允许的最大时间,系统默认的单位是秒(seconds)。“Slope-Rising Edge”(上升沿斜率)规则设置页面如图13-12所示。

(12)Slope-Falling Edge(下降沿斜率)规则

下降沿斜率与上升沿斜率是相对应的,它定义了信号从门限电压下降到一个有效的低电平时所允许的最大时间,系统默认的单位是秒(seconds)。“Slope-Falling Edge”(下降沿斜率)规则设置页面如图13-13所示。

图13-12 “Slope-Rising Edge”规则设置页面

图13-13 “Slope-Falling Edge”规则设置页面

(13)Supply Nets(电源网络)规则

电源网络定义了电路板上的电源网络标号。信号完整性分析器需要了解电源网络标号的名称和电压值。

在设置好完整性分析的各项规则后,在工程文件中,打开某个PCB设计文件,系统即可根据信号完整性的规则设置对印制电路板进行板级信号完整性分析。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。