对于一个功能明确、结构清晰的电路系统来说,采用层次电路设计方法,使用自上而下的设计流程,能够清晰地表达出设计者的设计理念。但在有些情况下,特别是在电路的模块化设计过程中,不同电路模块的不同组合,会形成功能完全不同的电路系统。用户可以根据自己的具体设计需要,选择若干个已有的电路模块,组合产生一个符合设计要求的完整电路系统。此时,该电路系统可以使用自下而上的层次电路设计流程来完成。

下面我们还是以“基于通用串行数据总线USB的数据采集系统”电路设计为例,介绍自下而上层次电路的具体设计过程。自下而上绘制层次原理图的操作步骤如下:

1)启动Altium Designer 14,新建项目文件。打开“Files”(文件)面板,在“新的”选项栏中单击“Blank Project(PCB)”(空白项目文件)选项,则在“Projects”(工程)面板中出现了新建的项目文件,另存为“USB采集系统.PrjPCB”。

2)新建原理图文件作为子原理图。在项目文件“USB采集系统.PrjPCB”上右键单击鼠标,在弹出的右键快捷菜单中选择“给工程添加新的”→“Schematic”(原理图)命令,在该项目文件中新建原理图文件,另存为“Cpu.SchDoc”,并完成图纸相关参数的设置。采用同样的方法建立原理图文件“Sensor1.SchDoc”、“Sensor2.SchDoc”和“Sensor3.SchDoc”。

3)绘制各个子原理图。即根据每一模块的具体功能要求,绘制电路原理图。例如,CPU模块主要完成主机与采集到的传感器信号之间的USB接口通信,这里使用带有USB接口的单片机“C8051F320”来完成。而三路传感器模块Sensor1、Sensor2、Sensor3则主要完成对三路传感器信号的放大和调制工作,具体绘制过程不再赘述。

4)放置各子原理图中的输入、输出端口。子原理图中的输入、输出端口是子原理图与顶层原理图之间进行电气连接的重要通道,应该根据具体设计要求进行放置。

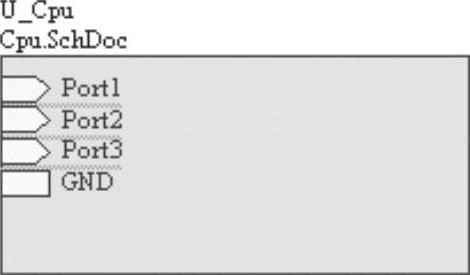

例如,在原理图“Cpu.SchDoc”中,三路传感器信号分别通过单片机P2口的3个引脚P2.1、P2.2、P2.3输入到单片机中,是原理图“Cpu.SchDoc”与其他3个原理图之间的信号传递通道,所以在这3个引脚处放置了3个输入端口,名称分别为“Port1”、“Port2”、“Port3”。除此之外,还放置了一个共同的接地端口“GND”。放置的输入、输出电路端口电路原理图“Cpu.SchDoc”与图5-10完全相同。

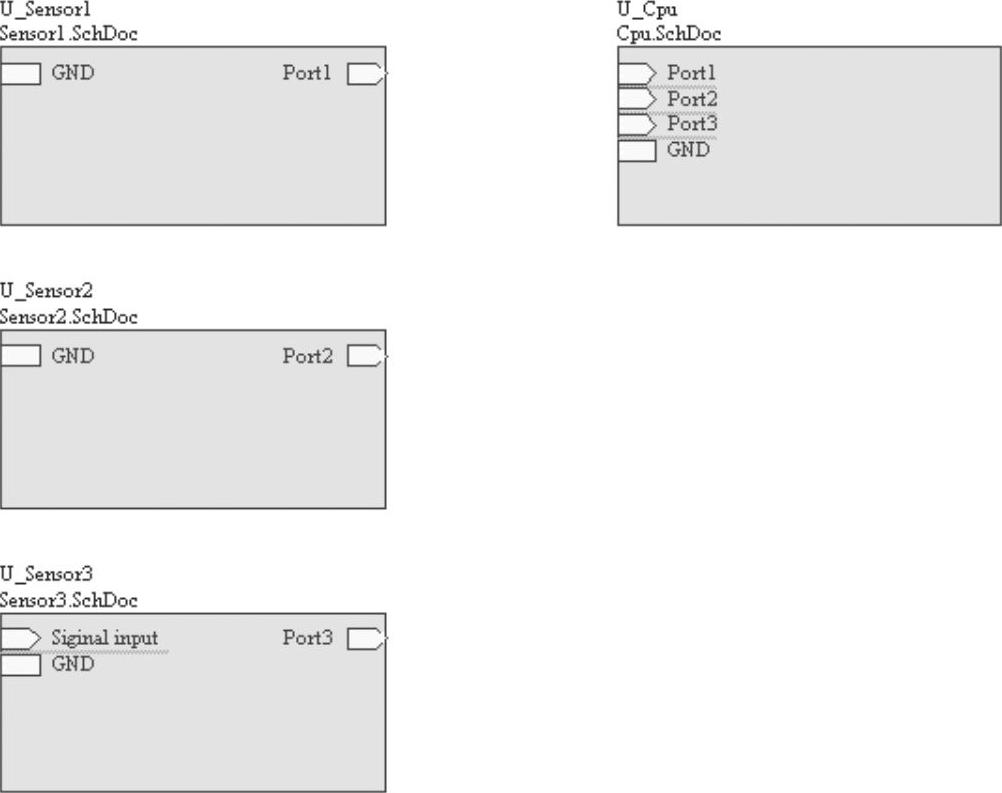

同样,在子原理图“Sensor1.SchDoc”的在信号输出端放置一个输出端口“Port1”,在子原理图“Sensor2.SchDoc”的信号输出放置一个输出端口“Port2”,在子原理图“Sensor3.SchDoc”的信号输出端放置一个输出端口“Port3”,分别与子原理图“Cpu.SchDoc”中的3个输入端口相对应,并且都放置了共同的接地端口。移动光标到需要放置原理图符号的地方,单击确定原理图符号的一个顶点,移动光标到合适的位置再一次单击鼠标确定其对角顶点,即可完成原理图符号的放置。

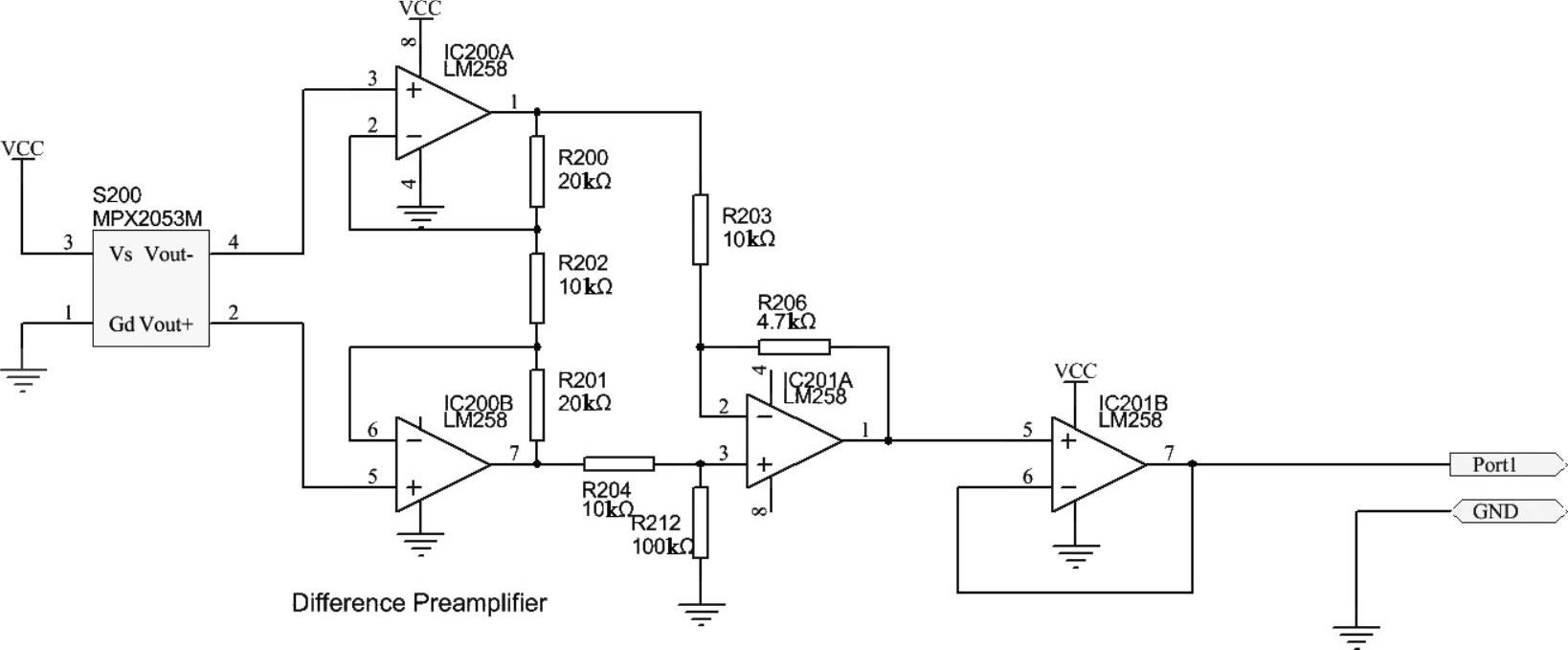

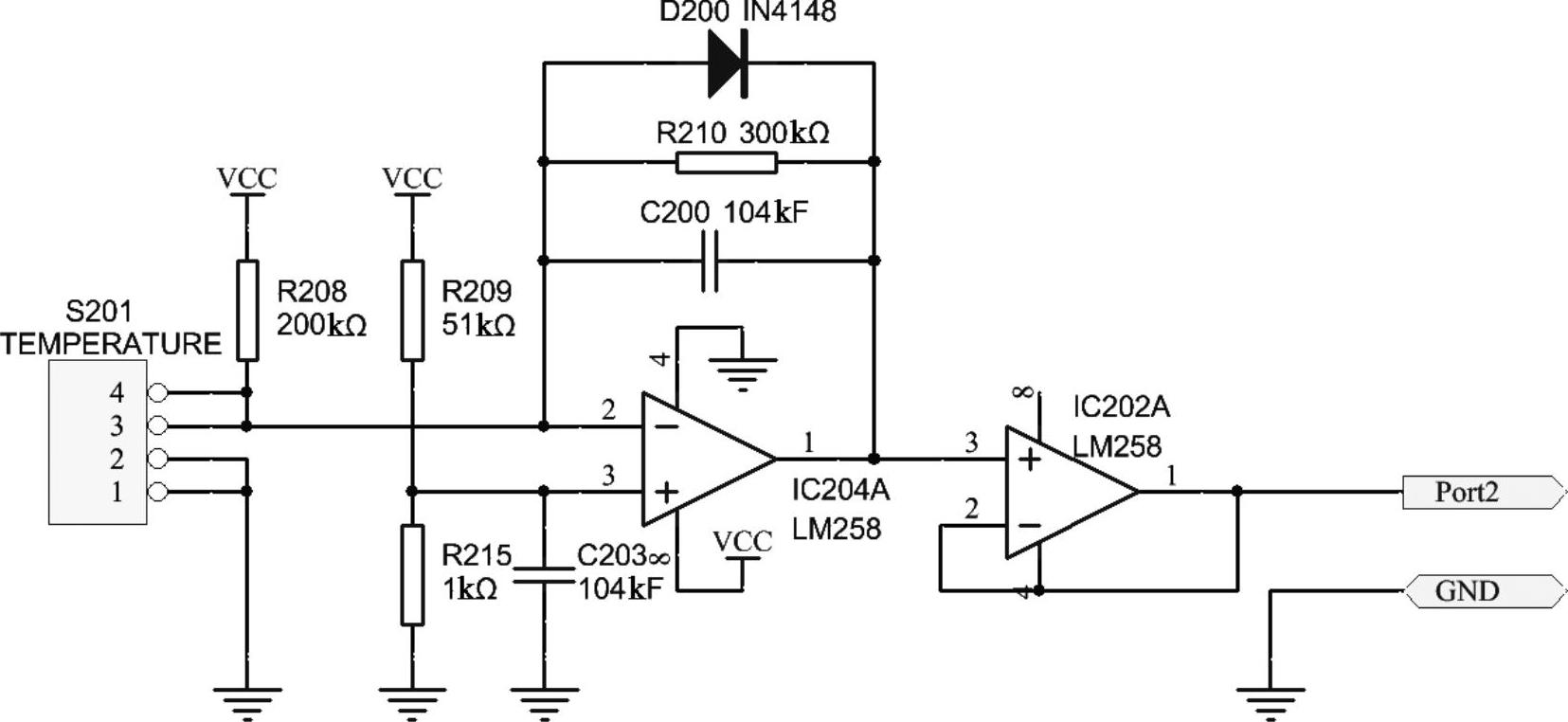

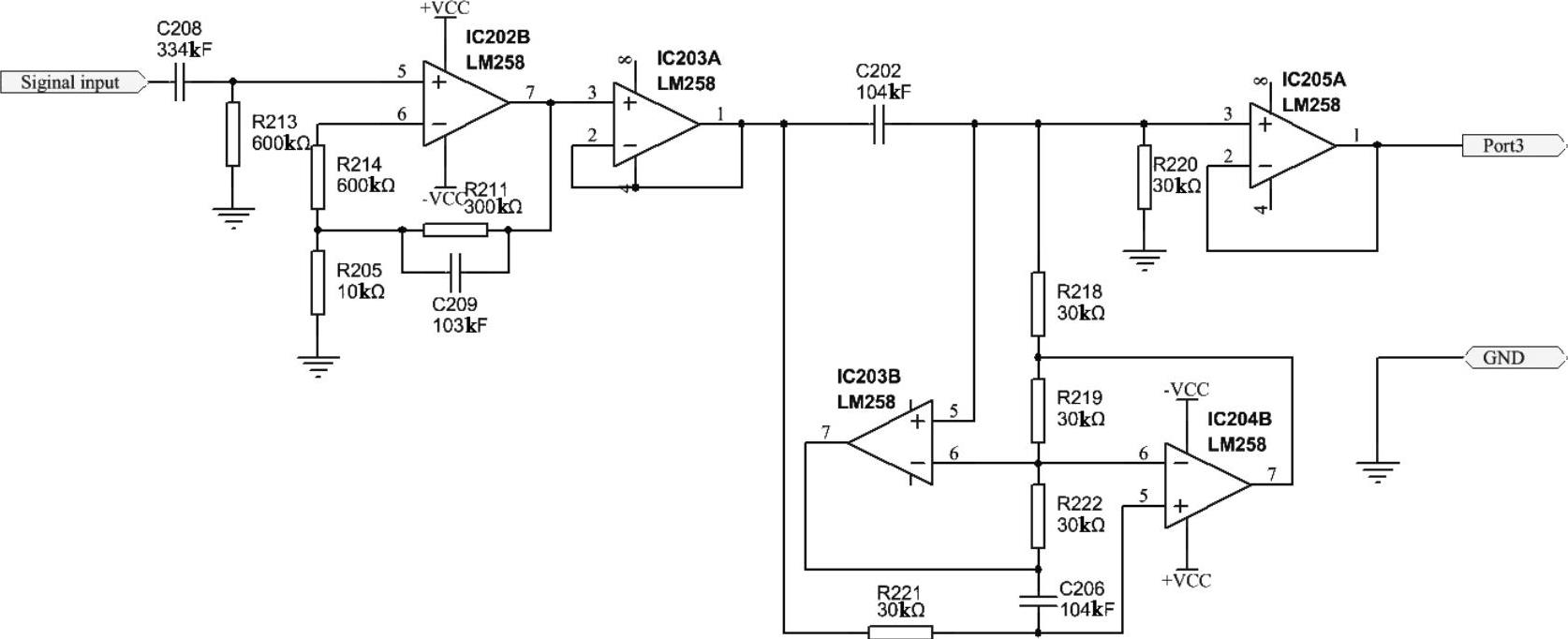

放置了输入、输出电路端口的3个子原理图“Sensor1.SchDoc”、“Sensor2.SchDoc”和“Sensor3.SchDoc”分别如图5-11、图5-12和图5-13所示。

图5-11 子原理图“Sensor1.SchDoc”

图5-12 子原理图“Sensor2.SchDoc”

图5-13 子原理图“Sensor3.SchDoc”(https://www.xing528.com)

5)在项目“USB采集系统.PrjPCB”中新建一个原理图文件“Mother1.PrjPCB”,以便进行顶层原理图的绘制。

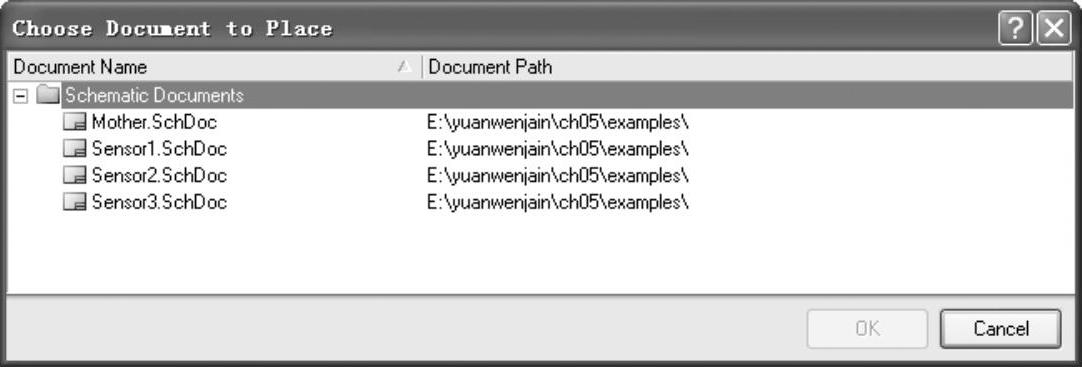

6)打开原理图文件“Mother1.PrjPCB”,单击菜单栏中的“设计”→“HDL文件或原理图生成图纸符”命令,系统将弹出如图5-14所示的“Choose Document to Place”(选择文件放置)对话框。

图5-14 “Choose Document to Place”对话框

在该对话框中,系统列出了同一项目中除当前原理图外的所有原理图文件,用户可以选择其中的任何一个原理图来建立原理图符号。例如,这里我们选中“Cpu.SchDoc”,单击“OK”(确定)按钮,关闭该对话框。

7)此时光标变成十字形状,并带有一个原理图符号的虚影。选择适当的位置,将该原理图符号放置在顶层原理图中,如图5-15所示。该原理图符号的标识符为“U-Cpu”,边缘已经放置了4个电路端口,方向与相应的子原理图中输入、输出端口一致。

8)按照同样的操作方法,由3个子原理图“Sensor1.SchDoc”、“Sensor2.SchDoc”和“Sensor3.SchDoc”可以在顶层原理图中分别建立3个原理图符号“U-Sensor1”、“U-Sensor2”和“U-Sensor3”,如图5-16所示。

图5-15 放置U_Cpu原理图符号

图5-16 建立顶层原理图符号

9)设置原理图符号和电路端口的属性。由系统自动生成的原理图符号不一定完全符合我们的设计要求,很多时候还需要进行编辑,如原理图符号的形状、大小、电路端口的位置要有利于布线连接,电路端口的属性需要重新设置等。

10)用导线或总线将原理图符号通过电路端口连接起来,并放置接地符号,完成顶层原理图的绘制,结果和图5-8完全一致。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。