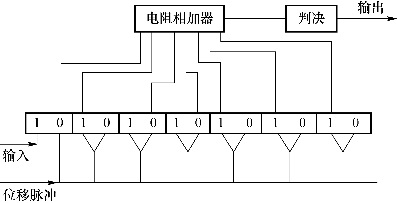

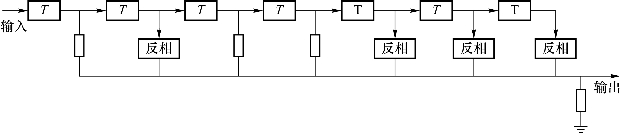

一般使用插入帧同步码组的方法来实现帧同步。对于数据传输的帧同步性能,一个主要要求是帧同步的捕捉时间要短。从失步重新进入同步状态这段时间是帧同步的捕捉时间,这时主要是设法尽快地从接收信号的脉冲序列中搜索到帧同步码组。也就是说,捕捉时间要尽量缩短,使接收端能够迅速达成同步状态。为此目的,选择帧同步码组要争取从接收脉冲序列中识别提取出来。这里介绍一种常用的方法——移位寄存器识别法。这种方法是将接收端恢复出来的数码输入到一列移位寄存器中去,移位寄存器的级数等于帧同步码组的位数,每一级移位寄存器的输出接帧同步码组结构连接电阻相加器,如图7.29所示。若输入到移位寄存器中的码组恰好是帧同步码组,则相加器输出电压应该是最大值;若输入到移位寄存器中的码组不是帧同步码组,则相加器输出电压低很多。这样,就可以利用最大输出电平来指示帧同步码组的起始相位,从而选出帧同步信号。

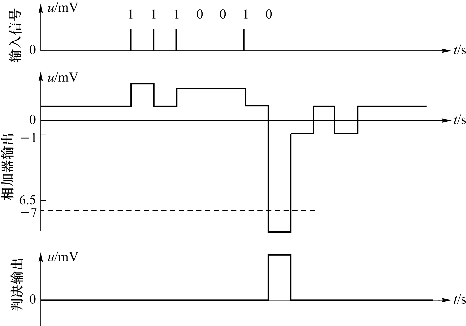

引用这种方法时常采用巴格码,7位巴格码是+++--+-,相当于二进制1110010序列。图7.29所示的是由7级移位寄存器组成的巴格码识别器,各级移位寄存器由右至左的顺序把序列1110010输出至电阻相加器进行相加。输出端连接至电阻相加器进行相加。当输入信号是这种7位巴格码序列时,输入有脉冲时表示1码,输入没有脉冲时表示0码。电阻相加器输出值最初变化较小,但在7位巴格码全部进入移位寄存器时,电阻相加器输出会呈现一个很大的峰负电压,其相对值为-7。在此以后,巴格码从移位寄存器移出,电阻相加器输出电压又回到较小值。图7.30所示的是相加器输出电压的变化情况,如判决器把判决电平定为-6.5,则当7位巴格码全部进入识别器,相加器输出电压呈现最大负值-7时,判决器就输出一个脉冲,作为帧同步的标志。

图7.29 由7级移位寄存器组成的巴格码识别器

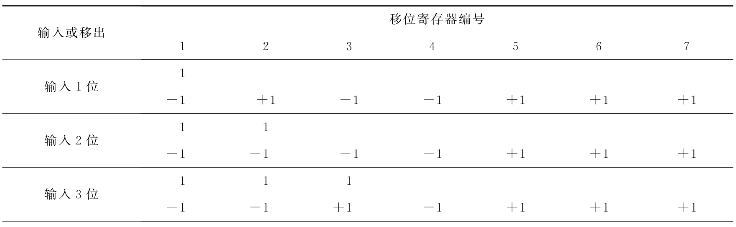

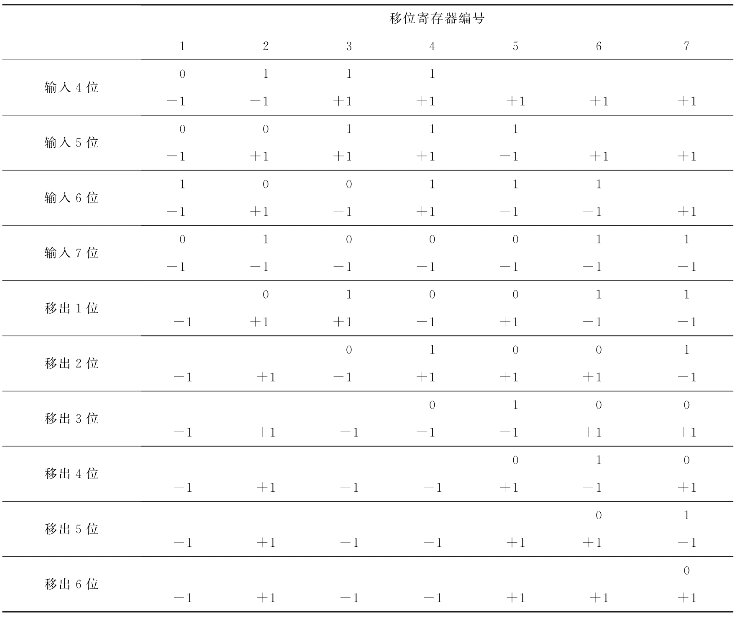

表7.1表示巴格码没有输入时及巴格码逐位移出时各级移位寄存器的状态,它们可以用来表明巴格码识别器如何获得图7.30所示的电阻相加器输出电压的变化。每级移位寄存器0态输出-1,1态输出+1。当1码进入移位寄存器时,它的状态翻转,即原来输出-1的变为输出+1,原来输出+1的变为输出-1。当0码进入移位寄存器时,它的状态不变,即原来输出-1或+1的仍是输出-1或+1。

图7.30 电阻相加器输出电压的变化情况

表7.1 巴格码逐位移出时各级移位寄存器的状态

续表

(https://www.xing528.com)

(https://www.xing528.com)

下面介绍信息码进入这种巴格码识别器时发生的情况。假设在巴格码没有输入之前,或巴格码若干位进入前或若干位移出后,信息码占满移位寄存器,没有进入的巴格码位数就是进入的信息码位数m。进入的m位信息码有2m种不同的码组,其中有一种可能使相加器出现最大输出。例如,当巴格码全部没有进入或全部已移出,而信息码占满7位(即|m|=7)时,有一种7位的信息码组可能使电阻相加器输出出现最大值-7,由于7位的信息码组有27=128种,所以出现这种最大输出的概率只有1/128。当巴格码进入1位或移出6位,信息码占6位,即|m|=6时,这1位巴格码的移位寄存器输出为+1,必有一种6位信息码组可能使电阻相加器输出出现最大值-5,由于6位信息码组有26=64种,所以这种最大输出的出现概率只有1/64。依此类推,当巴格码7位全部进入,没有信息码,即|m|=0时,电阻相加器输出最大值为-7,其概率为1。表7.2就是进入移位寄存器的巴格码位数,即信息码进入位数|m|可能使相加器输出出现的最大值A及最大值出现的概率值P。图7.31画出了|m|、P、A的关系。

表7.2 未进入移位寄存器的巴格码位数

图7.31 信息码位数|m|与电阻相加器输出最大值A及最大值出现的概率P的关系

上述7位巴格码识别器可以不用移位寄存器,而代之以模拟延迟线T,如图7.32所示。它提供同样的输出电压变化,因延迟线不需要移位脉冲,所以它的使用不要求预先建立同步。

图7.32 用模拟延迟线替代移位寄存器的7位巴格码识别器

除了7位巴格码以外,还有更长的巴格码序列,11位巴格码是11100010010,13位巴格码是1111100110101。随着码组位数的增加,有可能从接收的数据信息码序列中迅速识别出帧同步码组,捕捉时间短,丢失的信息少。

由于数据信息码序列具有随机性,所以可能出现象巴格码一样的序列,造成假同步,但这种假同步的概率很小。例如,7位巴格码序列的假同步概率为 13位巴格码序列的假同步概率降至

13位巴格码序列的假同步概率降至![]() 同时,也要考虑到,巴格码作为帧同步码组随同信息码一起传输,在受到信道干扰时会发生差错。例如,若7位巴格码有一位出现差错,则在它全部进入识别器后,相加器输出电压只有-6,如判决电平仍定为-6.5,势必造成漏同步。巴格码的位数增多时,漏同步的概率将加大。例如,若巴格码有13位,则漏同步的概率近于

同时,也要考虑到,巴格码作为帧同步码组随同信息码一起传输,在受到信道干扰时会发生差错。例如,若7位巴格码有一位出现差错,则在它全部进入识别器后,相加器输出电压只有-6,如判决电平仍定为-6.5,势必造成漏同步。巴格码的位数增多时,漏同步的概率将加大。例如,若巴格码有13位,则漏同步的概率近于![]() 如把判决电平改为容许出现一位差错的电平(即-5.5),则漏同步概率减小了,但假同步概率加大了。由此,选择判决电平时须对漏同步和假同步一同考虑。

如把判决电平改为容许出现一位差错的电平(即-5.5),则漏同步概率减小了,但假同步概率加大了。由此,选择判决电平时须对漏同步和假同步一同考虑。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。