可编程逻辑器件(Programmable Logic Device,简称PLD)是一种超大规模集成电路,它不仅具有集成度高,处理速度快和可靠性高的优点,而且它的逻辑功能是由用户自己通过对器件编程来设定的。

1.PLD的基本结构

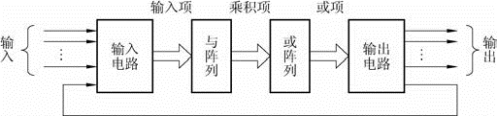

PLD的基本结构框图如图10-48所示,PLD电路的主体是由门构成的“与阵列”和“或阵列”,可以用来实现组合逻辑函数。输入电路由缓冲器组成,可以使输入信号具有足够的驱动能力,并产生互补输入信号。输出电路可以提供不同的输出结构,如直接输出(组合方式),或通过寄存器输出(时序方式)。此外输出端口通常有三态门,可通过三态门控制数据直接输出或反馈到输入端。

图10-48 PLD基本结构框图

通常PLD电路中只有部分电路可以编程或组态,PROM、PLA.PAL和GAL四种PLD由于编程情况和输出结构不同,因而电路结构也不相同,表10-17列出了四种PLD电路结构特点。其中GAL结构与PAL相同,由可编程的与阵列去驱动一个固定的或整列。

表10-17 PLD的四种结构

2.PLD的分类

1)按集成度分类

(1)低密度PLD(LDPLD),主要产品有PROM、现场可编程逻辑阵列(FPLA-field programmable logic array)、可编程阵列逻辑(PAL-programmable array logic)和通用阵列逻辑(GAL-generic array logic),其规模较小(通常每片只有数百门),难于实现复杂的逻辑。

(2)高密度PLD(HDPLD),它包括可擦除、可编程逻辑器件(EPLD-erasable programmable logic device)、复杂可编程逻辑器件(CPLD-complex programmable logic device)和现场可编程门阵列(FPGA-field programmable gate array)三种类型。EPLD和CPLD基本结构由与或阵列组成,因此通常称为阵列型PLD,而FPGA具有门阵列的结构形式,通常称为单元型PLD。

2)按制造工艺分类

(1)一次性编程的PLD,紫外线可擦除的可编程逻辑器件EPLD(Erasable PLD)。

(2)电可擦除的可编程逻辑器件EEPLD(Electrically Erasable PLD)。

1.三人表决器的制作

1)任务要求

制作一个三人表决器,每人有一个按钮开关,同意则按动按钮,表示为“1”。不同意则为“0”。最终结果由指示灯显示,两人或两人以上赞成,则指示灯亮,表示为“1”,否则指示灯不亮,表示为“0”。

2)设备要求

(1)数字电路实验箱一台(YZ11101C)。

(2)万用表若干。

(3)元器件:74LS00,74LS10每组各一只。

(4)实验连接导线若干。

3)制作过程

(1)三人表决器的逻辑状态分析。

设表决三人为变量A、B、C,“1”表示同意,“0”表示不同意。表决器结果为变量Y,表决通过表示为“1”,指示灯亮,表决不通过表示为“0”,指示灯不亮,如表10-18所示。

表10-18 三人表决器真值表

①由真值表写出逻辑式:

![]()

②用公式法或卡诺图化简逻辑表达式:

③变换成与非-与非表达式,用与非门实现。

④Y=![]()

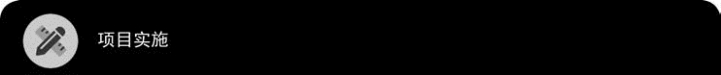

(2)由逻辑表达式画出逻辑图,如图10-49所示。

图10-49 三人表决器逻辑图

(3)三人表决器接线图。

按图10-50所示在逻辑实验箱上进行连线,其中A、B、C分别与三只按钮连接,Y端连接指示灯。

(4)安装与检测。

①在逻辑实验箱上找到两个14P插座安装74LS00和74LS10芯片。

②连接电源线和接地线。

图10-50 三人表决器接线图

③按照图10-50所示接线,接入输入信号A、B、C(8位逻辑电平输入端),接入输出信号Y(8位逻辑电平显示段)。

④接通+5 V电源。

⑤改变输入信号,观测输出信号的状态并记录。

⑥检测:测试结果,验证是否与真值表吻合。

4)总结

完成实验后进行总结。

2.JK触发器逻辑功能测试

1)任务要求

任务要求:按照测试程序要求完成所有测试内容。

(1)会测试JK触发器的逻辑功能。

(2)能描述用JK触发器构成计数器的原理。

(3)能用集成JK触发器制作计数器。

2)设备要求

(1)数字电路实验箱(YZ11101C)一台。

(2)数字式函数信号发生器1台(YB3050DDS)。

(3)万用表每组一块。

(4)元器件:74LS112,1块;10 K电阻5只;5.1 K电阻l只;按钮开关5只;LED发光二极管IN4007,1只。

(5)实验连接导线若干。

3)制作过程

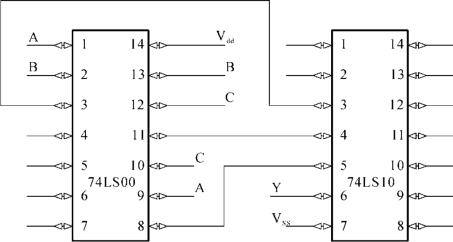

(1)引脚说明。如图10-51所示,CLK1、CLK2:时钟输入端(下降沿有效),J1、J2、K1、K2:数据输入端,Q1、Q2、/Q1、/Q2:输出端,CLR1、CLR2:直接复位端(低电平有效),PR1、PR2:直接置位端(低电平有效)。

(2)如图10-52所示连接,进行74LS112逻辑功能测试。

(3)安装与测试。

①在实验箱上安装好芯片、电阻、LED及开关(注意布局)。

②连接电源线和接地线,并按照上图完成电路的连接。

图10-51 74LS112芯片引脚图

图10-52 74LS112逻辑功能测试电路图

③接通电源,完成电路测试。

表10-19所示为74lS112逻辑功能表。

表10-19 74lS112逻辑功能表

续表

④按照表10-20所示,改变输入JK的状态以及CP脉冲的状态,记录相对应的输出Qn+1的状态,完成测试。

表10-20 74LS112触发器逻辑功能测试表

4)总结与思考

(1)当RD=0,SD=1时,输出Qn+1=?并思考CP脉冲状态对输出Qn+1的影响。

(2)当RD=1,SD=0时,输出Qn+1=?并思考CP脉冲状态对输出Qn+1的影响。

5)完成实验报告(https://www.xing528.com)

分析总结项目实施过程,完成实验报告。

3.用CC4518实现六十进制计数器

1)任务要求

按测试程序要求完成“CC4518实现六十进制计数器”测试内容;能描述集成计数器的功能并会使用;能用计数器CC4518芯片构成60进制计数器;能用复位法构成任意进制计数器。

2)设备要求

数字电路实验箱(YZ11101C)一台;万用表若干;数字式函数信号发生器(YB3050DDS)1台;元器件:CC4518、CC4011各l块,500Ω电阻8只,发光二极管8只,导线若干;实验连接导线若干。

3)制作过程

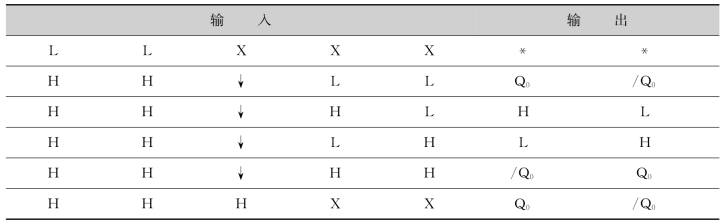

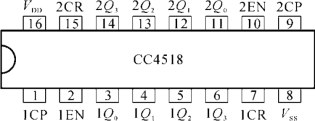

CC4518芯片引脚图如图10-53所示。CC4518逻辑功能表如表10-21所示。

图10-53 CC4518芯片引脚图

表10-21 CC4518逻辑功能表

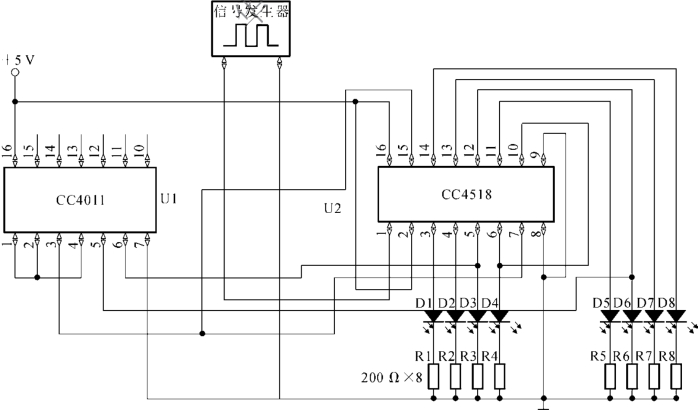

测试电路:用CC4518构成的六十进制计数器测试接线图,如图10-54所示。

图10-54 六十进制计数器的电路图

根据下图所示的用CC4518构成的六十进制计数器,测试程序如下。

(1)工作原理:如图10-54所示,为CC4518构成的60进制计数器的逻辑图,其技术原理是:计数脉冲输入到各片位的CP端,个位片本来就是十进制计数器,当每输入10个技术脉冲的上升沿到来时,1Q3由1变为0作为下降沿送到2EN,使十位片计数一次,当60个计数脉冲上升沿到来时,2Q2、2Q1同为1,经与非门送到1CR、2CR,使十位片、个位片同时复位,即使个位片和十位片的输出全部为0,完成一个计数循环。

计数脉冲由信号发生器提供,稳定电源提供+5 V电压,计数器的输入状态用8个发光二极管表示。调整信号发生器,使其输出频率为1 Hz的方波,观察发光二极管的工作情况是否符合60进制的计数规律。

(2)安装步骤。

①在试验箱上安装好芯片、电阻、发光二极管等。

②连接电源线和接地线。

③如图10-54所示连接好导线,并由函数信号发生器接入脉冲信号。

④接通电源,脉冲信号调为1 Hz的方波信号,观察LED灯的变化并做好记录。

(3)用CC4518实现六十进制计数器的逻辑图。

根据前面所学知识,画出图10-55所示的用CC4518构成的六十进制计数器的逻辑图。

(4)完成实验报告。

分析总结项目实施过程,完成实验报告。

图10-55 六十进制计数器的逻辑图

1.N进制需要用到N个数码,基数是N;运算规律为逢N进一。

2.逻辑函数的三种表示方法:真值表、表达式和逻辑符号图。

3.逻辑函数利用卡诺图规则和步骤进行化简。

4.组合逻辑电路的分析步骤:(1)写函数表达式;(2)逻辑化简;(3)列出真值表;(4)依据真值表或最简函数式确定电路的功能。

5.组合逻辑电路的设计步骤:(1)进行逻辑抽象;(2)写出逻辑函数式;(3)化简或变换;(4)画出连接图。

6.常见的触发器有R-S触发器、D触发器、J-K触发器、T触发器和T′触发器。

7.基本RS触发器、同步RS触发器、主从RS触发器都具有置位、复位和保持(记忆)功能。

8.利用已有触发器和待求触发器特性方程相等的原则,可求出触发器转换逻辑。

(1)写出已有触发器和待求触发器的特性方程。

(2)变换待求触发器的特性方程,使之形式与已有触发器的特性方程一致。

(3)比较已有和待求触发器的特性方程,根据两个方程相等的原则求出转换逻辑。

(4)根据转换逻辑画出逻辑电路图。

9.时序逻辑电路分析步骤

(1)根据给定的逻辑电路图分别写出方程组;(2)求状态方程组;(3)列状态转换表,画状态转换图。

10.D/A转换器把数字量转换为模拟量的过程称为数/模转换,完成这种转换的电路称为数模转换器。A/D是把模拟量转换为数字量的过程称为模/数转换,完成这种转换的电路叫模/数转换器。

11.随机存取存储器简称RAM,又称读/写存储器,既能方便地读出所存数据,又能随时写入新的数据,而ROM存储的数据不会因断电而消失,即具有非易失性。

一、填空题

1.逻辑代数的三种基本运算是________、或运算和________。

2.研究组合逻辑电路任务有________、________、________等方面。

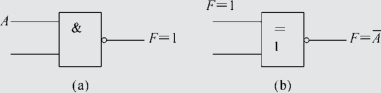

3.要实现图10-56所示电路输出端的逻辑关系,在图上标明空端应接逻辑1还是0?

图10-56 填空题3

4.对于触发器,当Q=1,Q=0时称触发器处于________状态;当Q=0,Q=1时称触发器处于________状态。

二、数制转换

1.将下列二进制数转化成十进制数。

(1)1010;(2)10101;(3)11001.01101;(4)10010111.011

2.将下列十进制数转化成二进制数。

(1)35;(2)84;(3)138;(4)15.25

3.将下列8421BCD码转化成十进制数。

(1)1001;(2)1010101;(3)110011.0111;(4)1000111.0110

4.将下列十进制数转化成8421BCD码。

(1)45;(2)58;(3)18.35;(4)13.25

三、化简题

1.Y=![]() +ABC+

+ABC+![]() +CD

+CD

2.Y=A+![]()

3.Y(A,B,C,D)=∑(m0,m1,m2,m4,m7,m9,m10,m11,m12,m13,m14,m15)

4.Y(A,B,C,D)=∑m(5,6,7,8,9)+∑d(10,11,12,13,14,15)

四、画图题

1.将下列函数用二端与非门实现,画出电路图。

(1)Z=ABD+ABC+ACD

(2)Z=![]() +ABD+

+ABD+![]()

2.边沿JK触发器的初始状态为0,CP、J、K信号如图10-57所示,试画出触发器Q端的波形。

图10-57 画图题2

五、问答题

1.组合逻辑电路有什么特点?组合逻辑电路分析的方法是什么?

2.组合逻辑电路的设计步骤有哪些?

3.时序逻辑电路分析步骤有哪些?

4.根据逻辑图10-58写出输出逻辑表达式,并用化简至最简与或式。

图10-58 问答题4

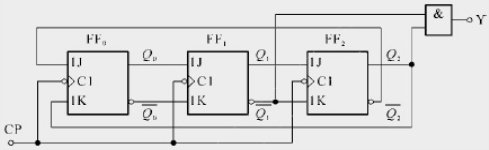

5.分析如图10-59所示时序逻辑电路的逻辑功能,并检查电路是否具有自启动功能。

图10-59 问答题5

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。