1.R-S触发器

触发器是组成时序逻辑电路的基本单元。常见的触发器有R-S触发器、D触发器、J-K触发器、T触发器和T'触发器等,它的显著特点是具有记忆功能,一个触发器能记住1位二进制值(0或1),n个触发器组成在一起,就能记忆n位二进制值信号。

触发器具有两个稳定状态,分别称之为0状态和1状态。且在外部信号作用下,触发器能从原来所处的一个稳态翻转到另一个稳态,当外部信号消失后,它仍能维持这一状态,即记忆住这一状态。

1)基本R-S触发器

基本R-S触发器是构成其他功能触发器必不可少的组成部分。它具有置位(置1)、复位(置0)、保持(记忆)三种功能,可用作数码寄存器、消抖动开关、单次脉冲发生器等,基本RS触发器属于无时钟触发器。

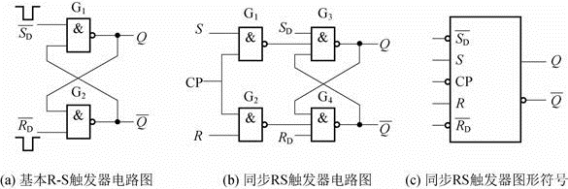

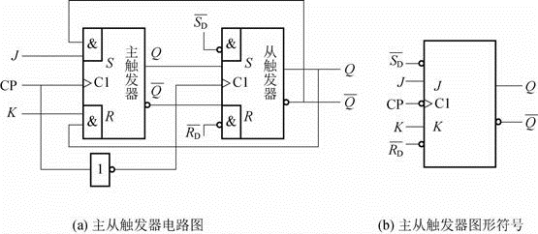

由与非门组成的基本R-S触发器电路结构,如图10-21(a)所示,它由与非门G1、G2组成,两个输入端为复位端和置位端,决定了其输出状态,图10-21(b)为同步RS触发器电路图,图10-21(c)为图形符号图,CP为时钟输入端,两个输出端分别为Q及![]() 。

。

图10-21 与非门组成的基本RS触发器

(1)逻辑功能分析。

![]() =1,

=1,![]() =0时,则

=0时,则![]() =0,Q=1,触发器置1。

=0,Q=1,触发器置1。

![]() =0,

=0,![]() =1时,则

=1时,则![]() =1,Q=0,触发器置0。

=1,Q=0,触发器置0。

![]() =1时,触发器状态保持不变。

=1时,触发器状态保持不变。

![]() =0时,触发器状态不确定。

=0时,触发器状态不确定。

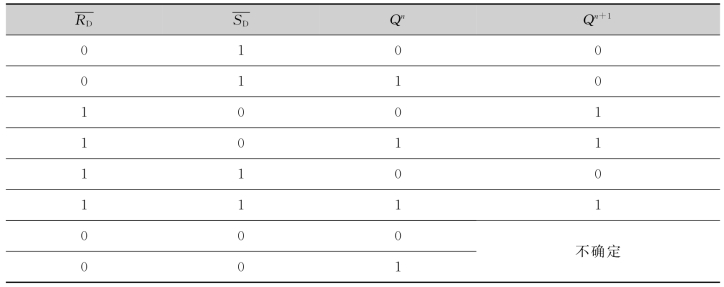

(2)根据逻辑功能,基本RS触发器的真值表如表10-11所示。

表10-11 基本RS触发器的真值表

(3)特征方程:

思考题:基本RS触发器为什么要有约束条件?

2)与非门构成的同步RS触发器

如图10-21(b),![]() 分别为直接复位端和直接置位端,使触发器直接置0和置1,它们不受CP时钟脉冲控制。

分别为直接复位端和直接置位端,使触发器直接置0和置1,它们不受CP时钟脉冲控制。

同步RS触发器工作原理为:在时钟电平CP=1期间,触发器工作;CP=0时触发器保持。在CP=1期间,若R=0,S=1则G1输出变为0,将向G3输出一个置1的负脉冲,不管触发器原状态如何,触发器Qn+1=1(置1);若R=1,S=0,同理得知,则G2输出变为0,将向G4输出一个置1的负脉冲,不管触发器原状态如何,触发器Qn+1=0(置0);在CP=1期间,若R=S=0,则触发器状态Qn+1=Qn;若R=S=1,则因G1和G2均送出一个负脉冲,触发器输出端会出现Q和![]() 均为1的逻辑不正常状态。

均为1的逻辑不正常状态。

其特性方程为:

![]()

如图10-21(c)所示为同步RS触发器图形符号图。

2.J-K触发器

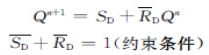

1)主从J-K触发器

主从J-K触发器由主触发器和从触发器构成,它属于脉冲触发方式,触发翻转只在时钟脉冲负跳变沿发生。主从J-K触发器具有置位、复位、保持(记忆)和计数功能,它不存在约束条件,在CP=1期间,J、K输入信号存入主触发器,从触发器状态不变;当CP下降到低电平时,主触发器信息传送到从触发器,控制从触发器翻转,此时主触发器保持状态不变,不受J、K端输入信号改变的影响,CP对主、从触发器进行隔离,因此主从触发器翻转可靠,可防止多次翻转的空翻现象。

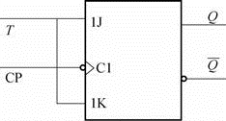

如图10-22所示,主触发器中:

![]()

图10-22 主从JK触发器

根据同步RS触发器特性方程:

Qn+1=S+RQn

得到J-K触发器特性方程:

Qn+1=JQn++KQn

表10-12所示为主从JK触发器的真值表。

表10-12 主从JK触发器的真值表

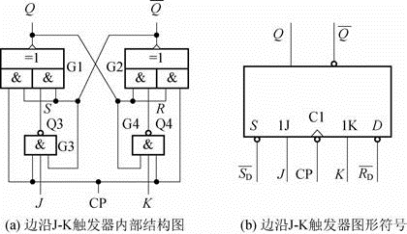

2)边沿JK触发器

边沿JK触发器的逻辑功能与主从JK触发器的逻辑功能是一致的,当CP的上升沿或下降沿来临时,触发器状态会根据输入信号发生变化,而CP其他持续期间,触发器状态不变。图10-23所示边沿JK触发器由两个与非门和两个与或非门组成,CP为时钟脉冲。

图10-23 边沿JK触发器

(1)CP=0时,触发器处于一个稳态。

(2)CP由0变1时,触发器不翻转,为接收输入信号作准备。

(3)CP由1变0时触发器翻转。

JK触发器特性方程:

Qn+1=JQn+KQn

总之,该触发器在CP下降沿前接受信息,在下降沿触发翻转,在下降沿后触发器被封锁。

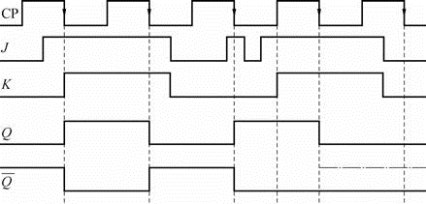

例10-8

在边沿JK触发器电路中,若CP下降沿时刻有效、J、K的波形已知,试画出Q、![]() 的波形,假设SD=RD=0,初始状态为Qn=0。

的波形,假设SD=RD=0,初始状态为Qn=0。

解

由JK触发器的逻辑功能表达式有:

![]()

由J-K触发器翻转规律,从Q=0初始态开始,逐周期画出Q、![]() 波形,如图10-24所示。

波形,如图10-24所示。

图10-24 例10-8波形图

3.D触发器

凡是在时钟信号作用下,输出状态始终保持与输入状态相同的触发器称为D触发器。

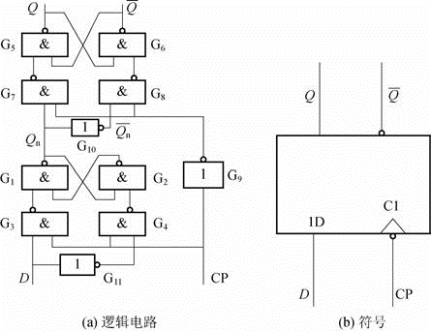

1)边沿D触发器

其电路结构如图10-25(a)所示,信号输入端为D,CP为时钟脉冲信号,逻辑符号图10-25(b)中CP端“∧”号表示CP边沿有效,小圆圈表示CP下降沿有效。

图10-25 边沿D触发器(https://www.xing528.com)

工作原理为:CP=0时。与非门G3、G4被封锁,输入信号D被阻断。G7、G8打开,从触发器的状态决定于主触发器,即Qn+1=Qn,![]() ;CP=1时。与非门G3、G4打开,G7、G8被封锁,从触发器保持原状态不变,D信号进入主触发器,Qn+1=D;CP下降边沿时。与非门G3、G4被封锁,G7、G8打开,主触发器锁存,CP下降沿瞬间的Qn+1=D,随后将该值送入从触发器,使Qn+1=D,

;CP=1时。与非门G3、G4打开,G7、G8被封锁,从触发器保持原状态不变,D信号进入主触发器,Qn+1=D;CP下降边沿时。与非门G3、G4被封锁,G7、G8打开,主触发器锁存,CP下降沿瞬间的Qn+1=D,随后将该值送入从触发器,使Qn+1=D,![]() 。

。

可得边沿D触发器的特性方程:

Qn+1=D(CP边沿时刻有效)

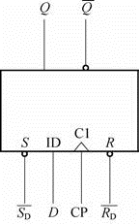

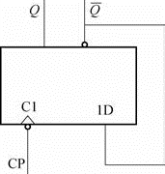

2)维持-阻塞D触发器

维持-阻塞D触发器,只有CP(↑)上升沿边沿瞬间接收D输入端的信号,在CP其他持续时间,触发器因维持-阻塞功能,使状态不变,它可克服空翻现象,如图10-26所示为维持-阻塞D触发器逻辑符号图,![]() 为直接置0端及置1端,低电平有效。维持-阻塞D触发器的特性方程为Qn+1=D(CP上升沿有效)

为直接置0端及置1端,低电平有效。维持-阻塞D触发器的特性方程为Qn+1=D(CP上升沿有效)

图10-26 维持-阻塞D触发器

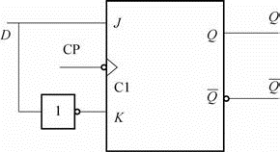

4.T(T′)触发器

1)T触发器

当控制信号T=1时,每来一个CP信号,它的状态就翻转一次,而当T=0时,其状态保持不变,具备这种逻辑功能的触发器叫作T触发器。如图10-27所示,为J-K触发器构成的T触发器。

若令J=K=T,则得出T触发器特性方程:

![]()

2)T′触发器

当T触发器控制端接至固定的高电平“1”时,可由T触发器得到T′触发器,即每次CP信号作用后,触发器状态必然翻转为与初态相反的状态,我们称这种触发器为T′触发器。

T′触发器特性方程为:

![]()

如图10-28所示,可由D触发器得到T′触发器,即将![]() 端与D端相连构成即可。

端与D端相连构成即可。

图10-27 JK触发器构成的T触发器

图10-28 由D触发器构成的T′触发器

根据D触发器的特性方程Qn+1=D,得出T′触发器的特性方程为:

![]()

5.触发器相互转换

1)JK触发器转换至D触发器

JK触发器的特性方程为:

Qn+1=JQn+KQn

D触发器的特性方程为:

Qn+1=D

即:

Qn+1=D=JQn+KQn

令:

![]()

![]()

画出逻辑电路图,如图10-29所示。

2)JK触发器转换至T触发器

T触发器的特性方程为:

![]()

令:J=T,K=T,画出逻辑电路图,如图10-30所示。

图10-29 JK→D触发器转换图

图10-30 JK→T触发器转换图

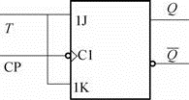

3)JK触发器转换至T′触发器

T′触发器的特性方程为:

![]()

即只需令J=K=1即可。

4)JK触发器转换至RS触发器

因为RS触发器的特性方程为:

![]()

变换公式如下:

![]()

由上式与J-K触发器特性方程对比,可令J=S,K=![]() 即可。

即可。

5)D触发器到其他触发器的转换

(1)D触发器转换至JK触发器。

令:D=![]() 即可。

即可。

(2)D触发器转换到T触发器。

令:D=T⊕Qn即可。

(3)D触发器转换到T′触发器。

令:D=![]() 即可。

即可。

(4)D触发器转换到RS触发器。

令:D=S+![]() 即可。

即可。

思考题:JK触发器如何转换成D触发器?

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。