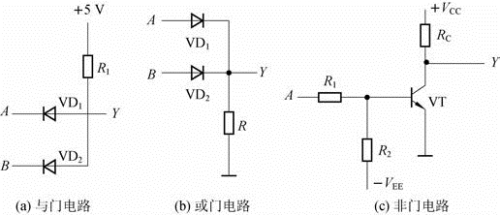

1.分立元件门电路

在数字电路中,“门”电路就是实现一些基本逻辑功能的电路。基本逻辑运算可归纳为“与”、“或”、“非”,其基本逻辑电路即为与门、或门和非门。逻辑门电路由电阻、电容、晶体管等分立元件构成的,称为分立元件门电路,如图10-11所示。

1)二极管与门

A、B输入均为高电平时,即VD1和VD2都截止,则输出Y为高电平;而A,B输入中只要有一个为低电平,输出Y均为低电平。

图10-11 分立元件门电路

2)二极管或门

A、B输入只要有一个高电平时,VD1、VD2有一只导通,输出Y为高电平,仅当A、B两端都为低电平时,两个都截止,故输出Y为低电平。

3)非门

A输入为高电平时,三极管VT导通,则输出Y为低电平;A输入为低电平时,三极管VT截止,故输出Y为高电平。

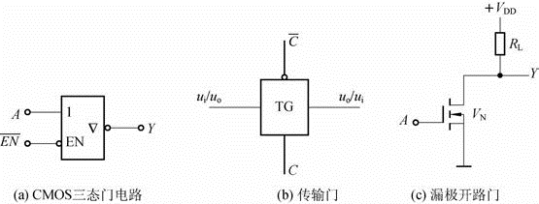

2.CMOS门电路

目前使用较多的集成逻辑门电路有两大类:CMOS和TTL器件组成的逻辑门电路。CMOS集成门电路具有制造工艺简单、输入阻抗高、功耗小、电源电压范围宽(3~18 V)等优点,使用较为广泛。CMOS集成门电路系列较多,有4000、HC、HCT、AC、ACT等系列,型号构成如CC54/74 HC04器件,代表54/74系列,HC表示高速CMOS电路,04表示型号。CMOS三态门、传输门和漏极开路门介绍分别如下。

1)CMOS三态门

如图10-12(a)所示是CMOS三态门的逻辑符号图。信号输入端为A,输出端为Y,![]() 是控制信号端,也称为使能端。EN处小圆圈(正逻辑时)表示控制信号低电平有效。

是控制信号端,也称为使能端。EN处小圆圈(正逻辑时)表示控制信号低电平有效。

图10-12 CMOS门电路逻辑符号图

2)CMOS传输门

图10-12(b)所示是其逻辑符号图,![]() 为控制端信号,可以双向传输。当C=

为控制端信号,可以双向传输。当C=![]() =0,传输门导通,uo=ui,当C=

=0,传输门导通,uo=ui,当C=![]() =1,传输门截止。

=1,传输门截止。

3)漏极开路门(OD门)

CMOS漏极开路门(OD门)漏极开路,工作时须加上拉电阻R,电路才能工作。如图10-12(c)所示,因输出漏极开路,可方便地把几个输出端并接起来,实现线与功能。

思考题:如何理解三态门电路的三种状态?

3.TTL门电路

TTL(transistor-transistor logic晶体管-晶体管逻辑门)有74(标准)系列、74H(高速)系列、74S(肖特基)、74LS(低功耗肖特基)、74AS(改进型)系列、74ALS(改进型)系列等门电路。TTL集成门电路的工作电压范围为4.5~5.5 V。(https://www.xing528.com)

1)特性和参数

(1)标准输出高电平VoH≥2.4 V(VoH=2.4 V为输出高电平的下限值)。

(2)标准输出低电平VoL≤0.4 V(VoL=0.4 V为输出低电平的上限值)。

(3)阈值电压Vth=1.2~1.4 V,电压传输特性转折区中点对应的输入电压值。

(4)输入端噪声容限:输入低电平噪声容限VNL=0.3 V。

(5)输入高电平噪声容限VNH=-0.3~0.9 V。

(6)扇出系数No:不影响输出状态,带同类门的个数,No一般为8~10个。

(7)动态特性:tpd:54/74 H系列一般为6~10 ns。

2)TTL门电路使用要求

(1)工作电压范围:4.5~5.5 V。

(2)除OC门和三态门外,输出端不允许并联使用。

(3)不能在通电情况下带电插拔集成电路。

(4)不使用的与非门输入端接高电平或电源、或非门输入端接地,以降低功耗。

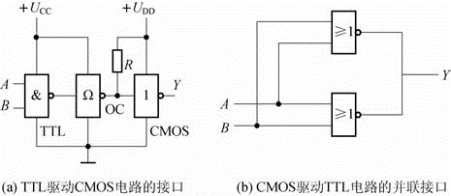

4.CMOS和TTL门电路驱动

1)TTL驱动CMOS门电路

TTL工作电压范围为4.5~5.5 V,CMOS电路工作电压为3~18 V,所以TTL电路输出的高电平不能达到CMOS输入高电平要求,需要使用集电极开路门(OC门),同时需加上拉电阻保护TTL门电路,完成TTL电路与CMOS电路的接口。

2)CMOS驱动TTL门电路

CMOS器件为电压控制型器件,TTL器件是电流控制器件,CMOS驱动TTL门电路时,需扩大CMOS电路驱动负载的能力。

(1)如图10-13(a)、(b)所示,并联加大驱动,可提高驱动能力。

(2)输出加三极管或加专用芯片(如40107)提升输出电流,以驱动TTL门电路。

图10-13 TTL和CMOS驱动电路

思考题:为什么集电极开路门(OC门),输出与电源之间需外接电阻?

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。