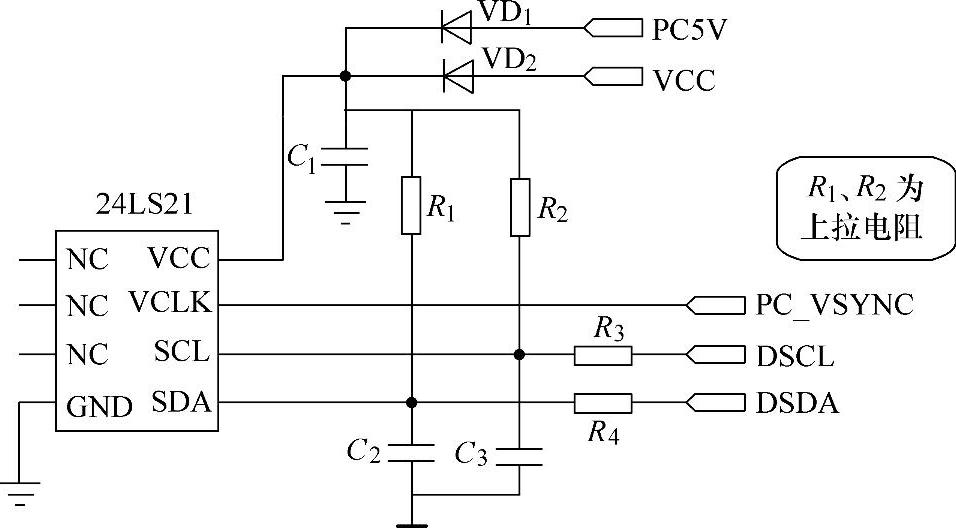

【摘要】:但由于其时钟线SCL、数据线SDA均采用开漏结构,在电路中设置上拉或下拉电阻器可避免I/O端口出现漂移状态,也可提高电路负载能力。图2-4中,芯片24LS21端口SCL、SDA分别为I2 C总线时钟线和数据线,外接贴片电阻器R1、R2实现上拉功能。图2-4 利用贴片电阻器实现上拉功能4)在COMS芯片上,为了防止静电造成损坏,不用的引脚不能悬空,一般接上拉电阻降低输入阻抗,提供泄荷通路。

在工程技术中,I2 C总线控制技术应用日益广泛。但由于其时钟线SCL、数据线SDA均采用开漏结构,在电路中设置上拉或下拉电阻器可避免I/O端口出现漂移状态,也可提高电路负载能力。利用贴片电阻器实现上拉功能如图2-4所示。

图2-4中,芯片24LS21端口SCL、SDA分别为I2 C总线时钟线和数据线,外接贴片电阻器R1、R2实现上拉功能。实际应用时,上拉和下拉贴片电阻器使用应遵循如下原则:

1)当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平。

2)OC门电路必须加上拉电阻,以提高输出的高电平值。

3)为加大输出引脚的驱动能力,有的单片机引脚上也常使用上拉电阻。

(https://www.xing528.com)

(https://www.xing528.com)

图2-4 利用贴片电阻器实现上拉功能

4)在COMS芯片上,为了防止静电造成损坏,不用的引脚不能悬空,一般接上拉电阻降低输入阻抗,提供泄荷通路。

5)芯片的引脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6)提高总线的抗电磁干扰能力。引脚悬空就比较容易受外界的电磁干扰。

7)长线传输中电阻不匹配容易引起反射波干扰,加上、下拉电阻可有效抑制反射波干扰。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。