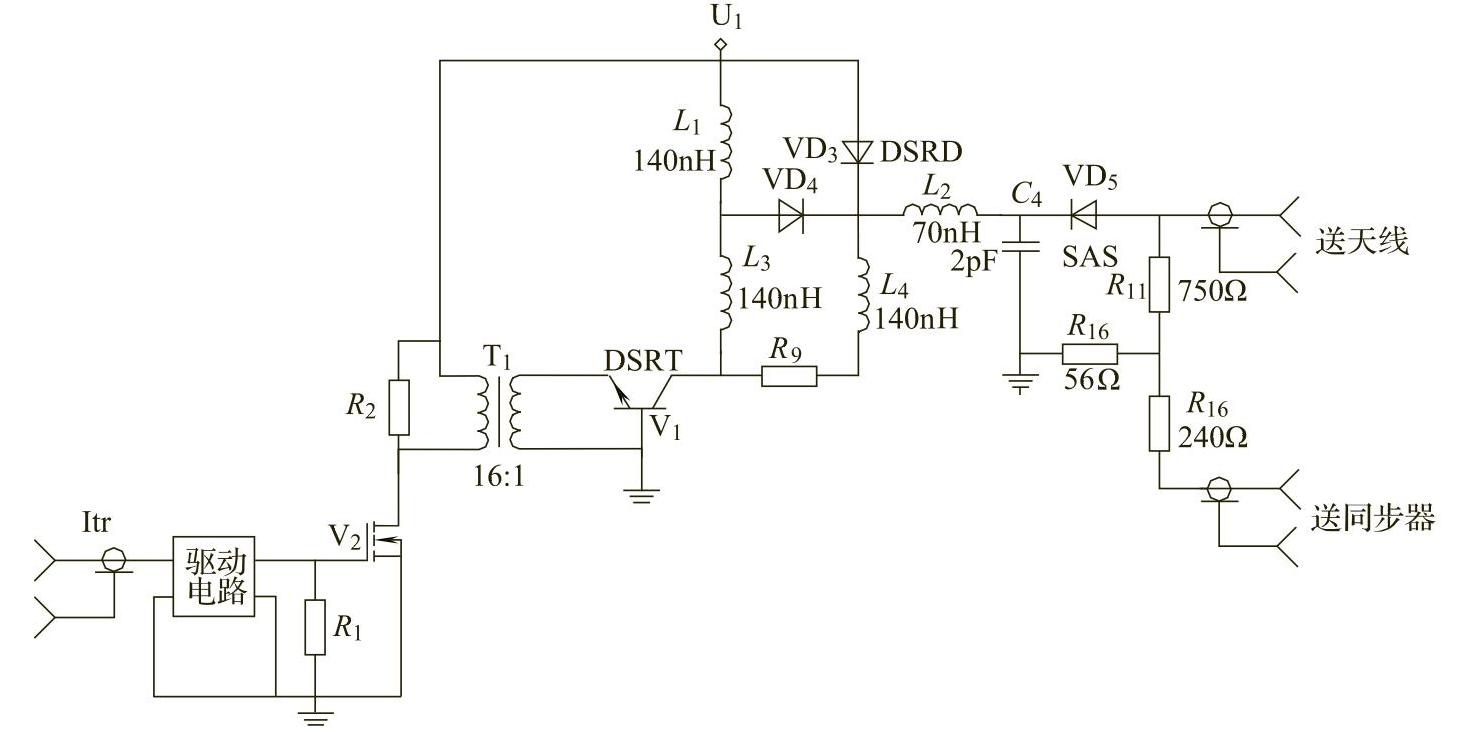

【摘要】:脉冲产生器电路如图4-95所示,这是一个脉冲产生单元。在V1导通期间,VD3通过L4和R9被激励。当V1内激励的等离子体泄放时,其集电极迅速截止。电感L1中的电流分别流过VD4和VD3,而VD3由于以前的激励,仍处于导通状态。在振荡的后半周期L1和L3中的电流方向相同,随后VD3截止L1和L3中的电流通过L2给C4充电。

脉冲产生器电路如图4-95所示,这是一个脉冲产生单元。开始时DSRT截止,驱动脉冲(宽度约为100ns)通过T1加到V1,激励了集电极电子—空穴等离子体。电感L1、L3中的电流按照di/dt=U1/(L1+L3)线性上升。驱动脉冲结束后,由于等离子体的激励作用,V1仍能导通一段时间。在V1导通期间,VD3通过L4和R9被激励。当V1内激励的等离子体泄放时,其集电极迅速截止。电感L1中的电流分别流过VD4和VD3,而VD3由于以前的激励,仍处于导通状态。电感L3中的电流在V1的集电极电容、L3、VD4、VD3所构成的电路中谐振。在振荡的后半周期L1和L3中的电流方向相同,随后VD3截止L1和L3中的电流通过L2给C4充电。当C4电压达到VD5门限电压时,VD5导通将C4上的能量泄放至负载。

图4-95 脉冲产生器电路

输出脉冲如图4-96所示,输出电平为1.1kV(50Ω负载),上升时间小于70ps,脉宽为200ps,中心频率为5GHz,最大重频为12kHz。若进行良好的热设计,重频可以做到50kHz,效率将超过15%。(https://www.xing528.com)

图4-96 脉冲产生器单元输出波形

图4-95给出的是一个脉冲产生器单元的设计方案,如果配以精准的同步器,可以将多个脉冲产生器单元组合,进行功率合成。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。