1.实验引言

纳秒、微秒和毫秒级的高电压脉冲发生器广泛使用于细胞电穿孔疗法(EPT)、基因治疗和研究等领域,此外还有超声波清洗、化学无细菌净化和医学成像。在过去,这些低阻抗负载要求使用昂贵的组件或是有复杂、混合型拓扑结构的设计电路。最近在半导体掺杂技术和沉积技术中的进步使MOSFET得以大批量生产,这些MOSFET具备纳秒级的转换率,在数十安培额定电流和低漏源电阻的情况下仍能对数百伏的电压进行开关。由于MOSFET简单的驱动条件、较快的转换速率以及高功率容量等特点,可以降低电路的复杂性。设计的重点在于电路的简单性、布局、适当的无功补偿和最优结构。应该注意设计适当的电路结构,以使得脉冲失真达到最小。上升和下降时间、瞬时振荡和过冲都会导致单个脉冲传到负载和脉冲序列或周期信号传到电源的能量降低。在纳秒级的脉宽中,频谱超过了千赫兹的频率。负载不匹配将会扭曲信号,研究人员的任何比较结果都只能在偶然的情况下比较,而不能分析。由仪表发生器向无偿放大器传递的脉冲将会被扭曲而失真。

本例的目的在于建立一个低成本的纳秒到微秒级脉冲发生器,用于电穿孔的基因治疗和加强药物输送运用。这是利用了电穿孔技术的简单、容易控制和有效等优点。通常情况下,电场强度在1300V/cm和100μs的脉冲常用于EPT和低电压基因治疗,但需要更长的脉冲,如200V/cm和20~50ms。电穿孔后的可行性或细胞存活率仍待优化,此技术的有效性依赖于脉冲持续时间和其他参数。可以设想,使用更高强度的短脉冲可以大大改善各种哺乳动物细胞的存活率。

2.简单的纳秒级脉冲发生器的设计

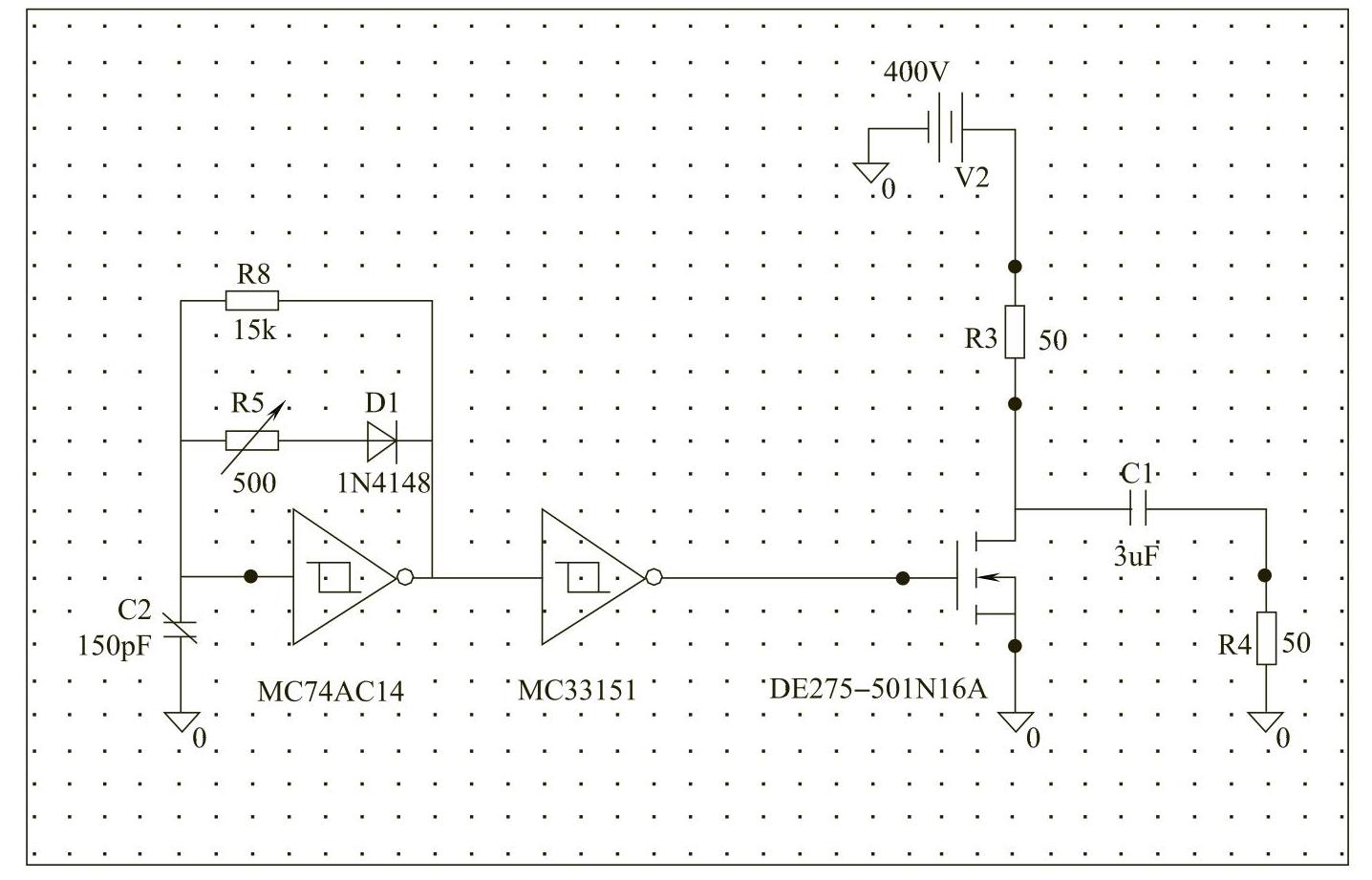

设计中的电路是利用1400V/75ns脉冲来驱动一个50Ω电阻负载。电路包括3个环节:一个集成可变频率和可变脉宽的信号发生源、一个逆变器/驱动器模块和包含被动负载单电源MOSFET的电源缓冲区。对电路结构进行物理特性优化来减少信号失真和保持信号完整性,同时尽量减小电路和负载中的反射功率。选择的驱动器是集成半导体器件MC33151,上升时间是15ns,将施密特触发输入信号转换为图腾柱输出。缓冲区是IXYSDE275-501N16A射频MOSFET,Udss为500V,Id为16A,上升时间为6ns。MOSFET加偏压至截止关断,同时设计的电路使得上升时间最大化且共源极工作,以得到最佳效率。MOSFET工作应对一个由3个并联高功率150Ω电阻组成的被动负载。电压源的设计是线性的,信号源和驱动电源的设计比较规范。

设计此电路的目的是探讨在一个简单、低造价的电路中大规模使用于标准消费领域的产品的可行性,此电路用于研究应用于EPT和基因治疗等领域的高电压纳秒级脉冲发生器。电路的实现完全使用的是现有的元器件,由商业射频平面微波元组件构成。首先,由于250V的桥式整流器和高质量的250V电容很便宜,使用比较普遍,于是输出级采用的是200V的电压源。然而,如果把分接头接到隔离变压器的120:240V交流设定档,可以使得输出电压增加到400V,由0~140V的交流调压器驱动,把电容串联起来,可以使得其额定电压增加一倍。这种装置能够允许电路测试和故障排除在连续可变电压0~400V内完成。线性电源专门用于降低电路的噪声,18V的驱动源是由34V线性电压源调小而成。5V的逻辑源在电路板上,是由18V的电压源调节而成,使得纹波抑制加倍。

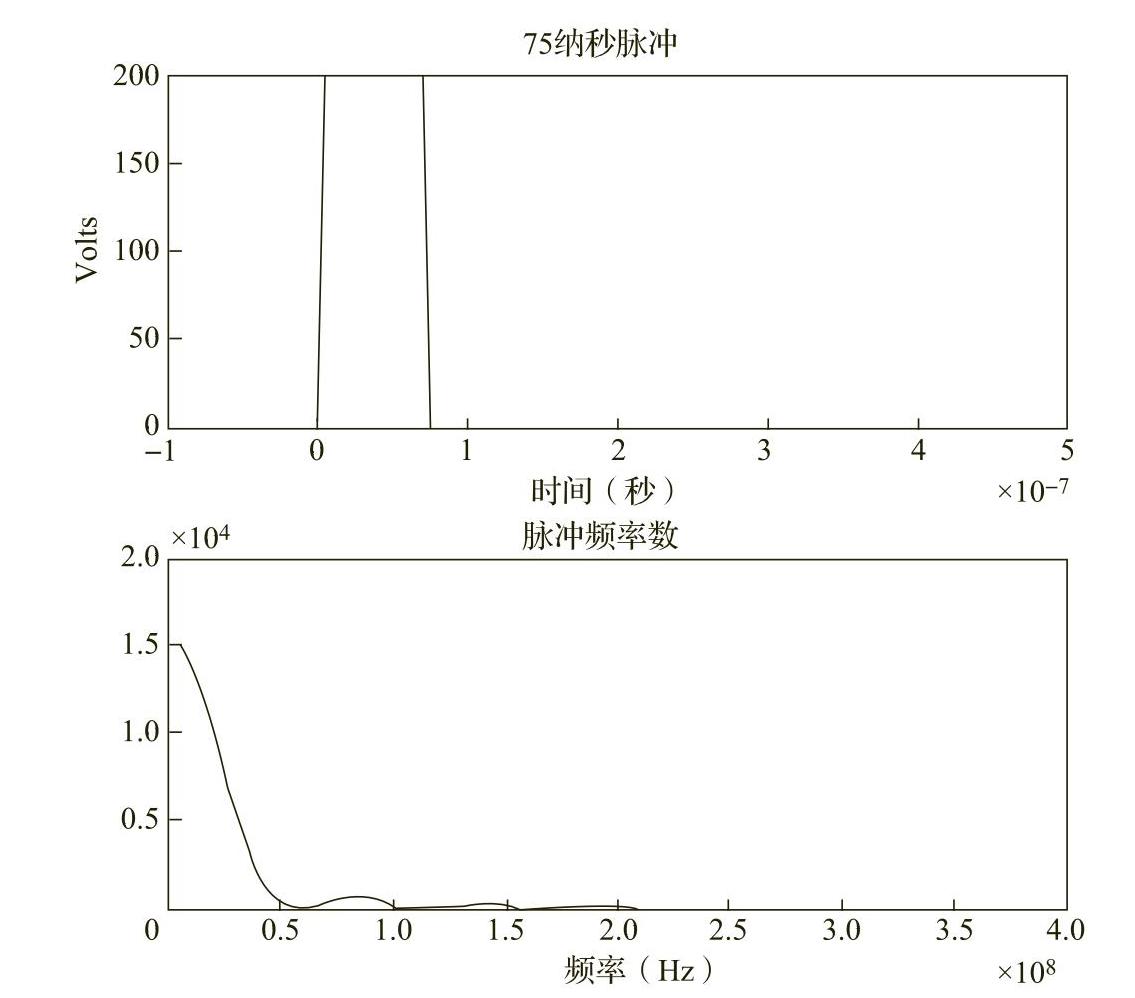

通过MATLAB软件对200V纳秒脉冲的快速傅里叶变换进行分析,如图3-45所示可以看出电路需要兆赫兹频率带宽的结构考虑。高频电路要求微带零电位平面结构来减少寄生阻抗和诱导振荡或无功反映。一项对可行性样机系统的调查指出商用无线电频率和表面贴装开发电路板规格在设计参数范围内有所下降。

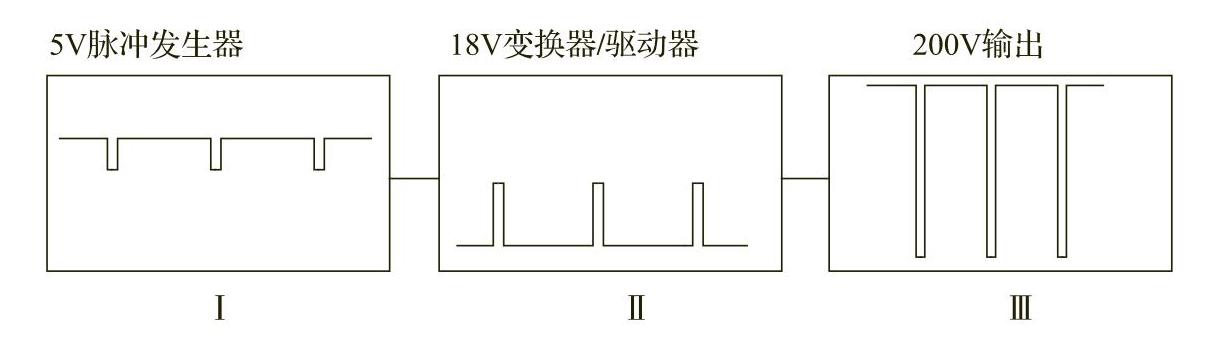

为了减少设计的复杂性,设计中采用了3个环节的拓扑结构,设计过的两环节电路被证实不稳定不可靠。电路可以连续几分钟内产生脉冲,直到MC33151失效,输入到输出短路。目前的电路包括一个可变脉宽的脉冲发生器、一个集成驱动器/转换器和一个电源输出环节(见图3-46)。3个环节的设计被证实是简单可靠的。

图3-45 利用MATLAB软件对200ns脉冲的FFT分析

图3-46 减小复杂性的简单3个环节,分别为纳秒级脉冲、输出级驱动器和输出级

3.单电源、驱动器和输出电路

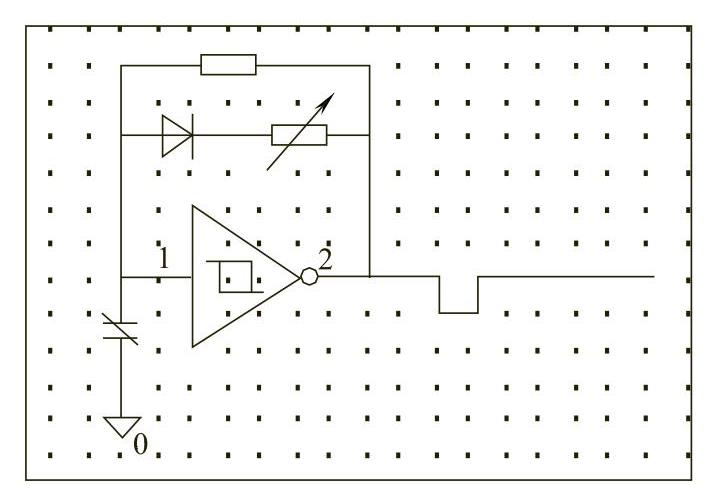

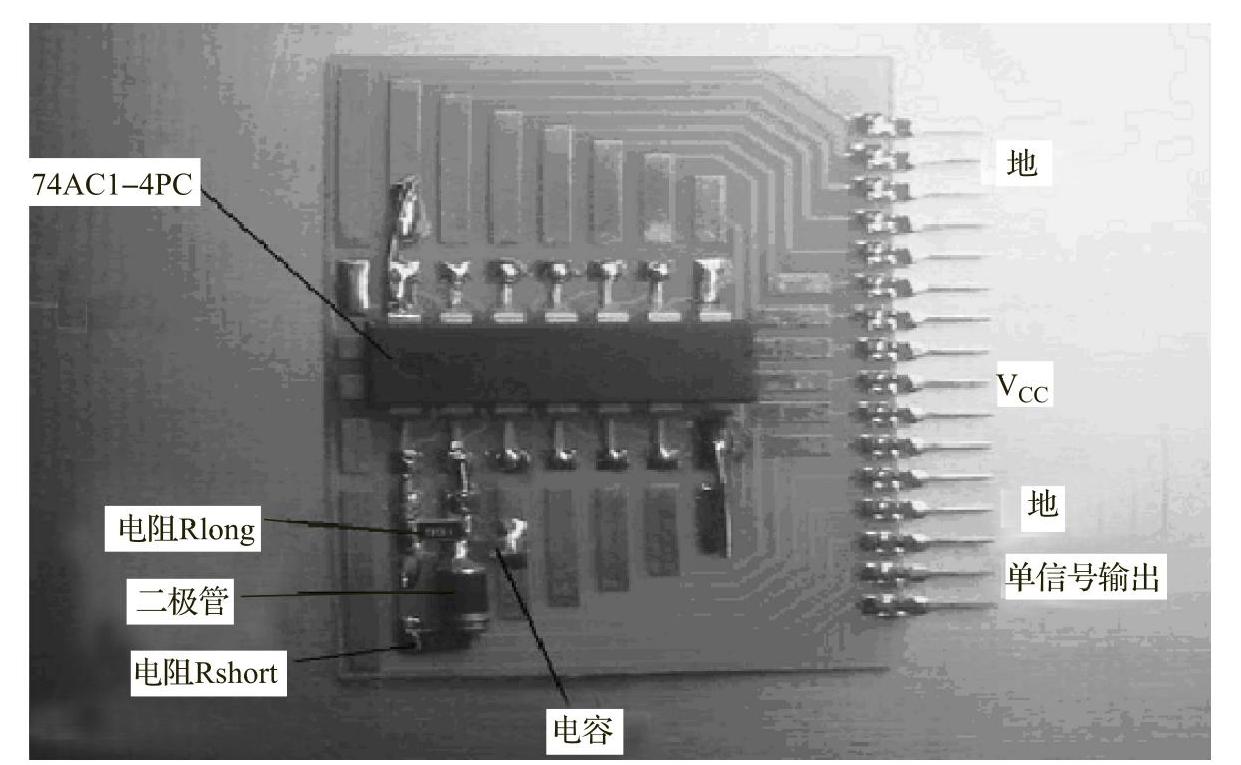

第一个环节包括一个逻辑级75ns脉冲发生电路。该电路基于时域反射法原理,使用基于施密特触发器的弛豫振荡器,用作稳态触发器。这个设计的有效性在于其低脉宽和高脉宽是可变的,从性能上讲,采用MC74AC14的半导体集成电路是最佳的。无源可变器件的使用允许内置电路的优化。可变电阻是300Ω,固定电阻是15kΩ。可变电容是150pF,二极管是1N4148,图3-47给出了图解说明。信号源电路可置于不同的物理形式中,测得脉宽均为3ms。

图3-47 单电源电路:可变电阻300Ω,其他阻抗15kΩ,电容150pF和二极管1N4148

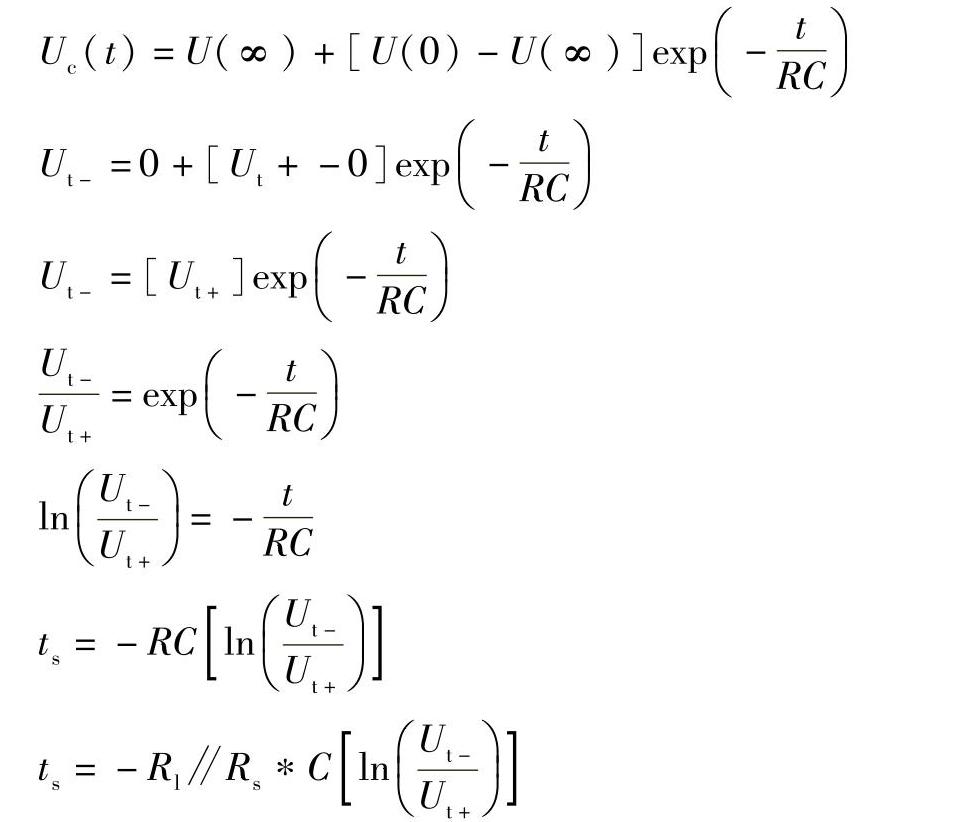

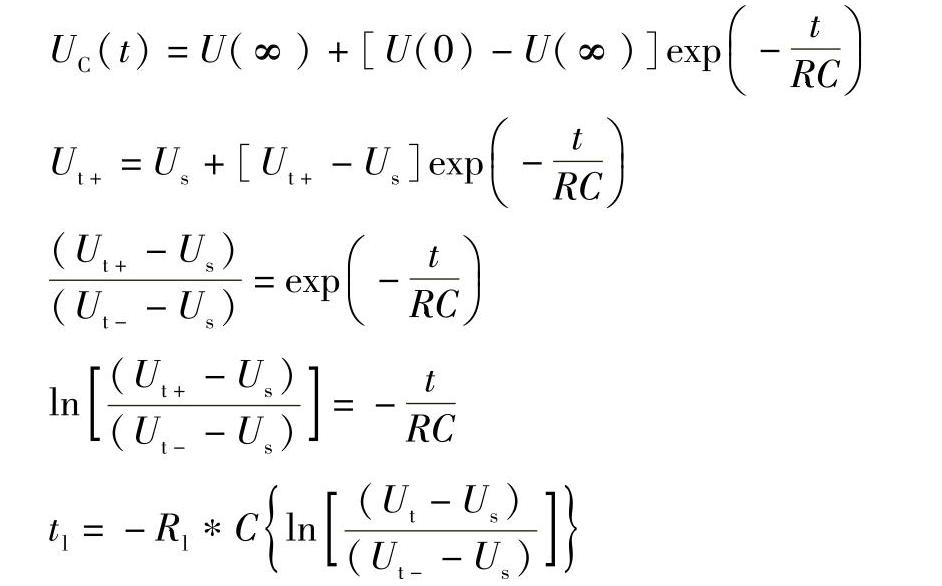

单电源脉冲发生器的分析(见图3-47)给出了负脉冲中短时ts和较长的tl由无源器件的时间常数RC决定。C是电容,长R(Rl)决定了长的脉冲间隔时间,短R(Rs)与Rl并联,比Rl阻值小,决定了短脉冲时间。MC74AC14施密特触发器设计有在正阈值电压Ut+和负阈值电压Ut-之间的磁滞现象。通常情况下,Ut+=3.5V,Ut-=1.0V。这两个参数在实际电路中需要准确的测量以得到脉冲时间。ts是电容通过两个电阻放电的时间,电容电压Uc放电至Ut-。R是并联电阻Rl//Rs。U(∞)是0V,如果施密特触发器不工作,电容就会放电。

tl是电容通过Rl从Ut-充电至Ut+的时间;U(∞)=Us是电压源。

重复频率为1/(ts+tl)

通过集成逆变器/驱动器,将5V信号源脉冲放大到18V。MC34151设计用于驱动MOSFET栅极,采用的转换器件用于减少过冲和信号源脉冲的振荡。转换的时候,低于驱动器门极阈值电压的噪声可以被消除。在转换之后,1.5μs脉冲变成用于驱动输出环节75ns脉冲间的延时。(https://www.xing528.com)

输出环节包括一个单管N沟道增强型功率MOSFET,IXYSRF DE275-501N16A具备500V的Uds,16A的Id和6ns的上升时间。输出环节被3个并联150Ω电阻加载,以得到接近50Ω的源极阻抗。MOSFET的漏极与一个50Ω的微带传输线相连,通过同轴电缆和RG-58电缆与50Ω等效负载交流耦合连接在一起。

4.结果讨论

图3-48 电路设计图

图3-49 电路设计结构图

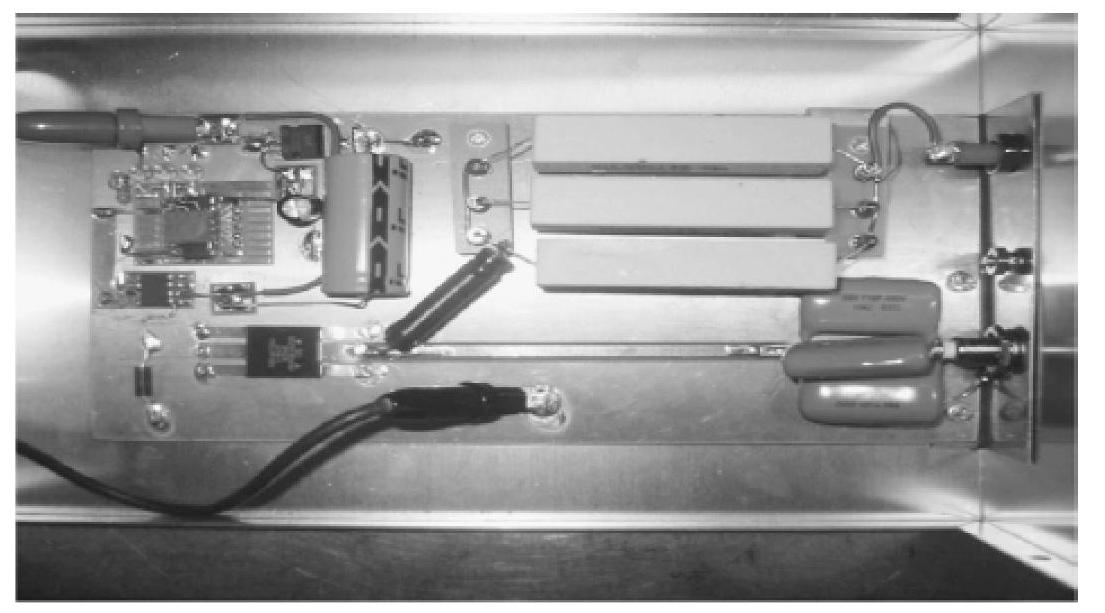

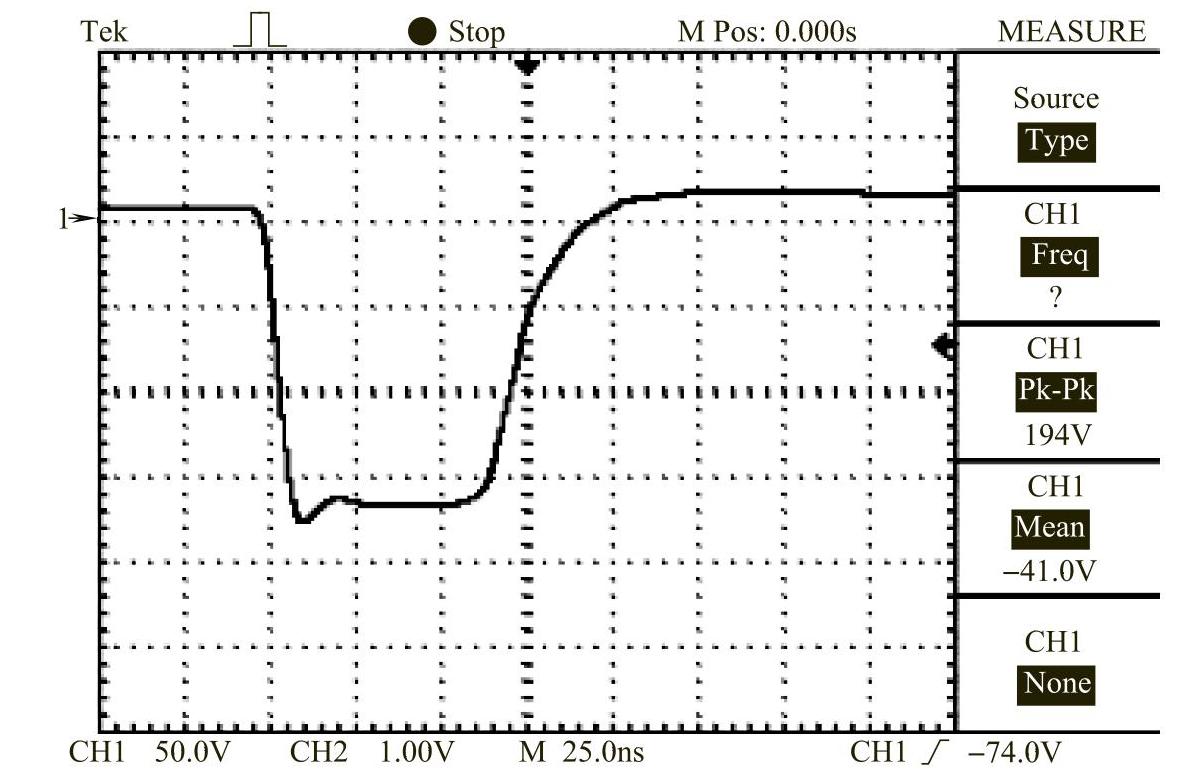

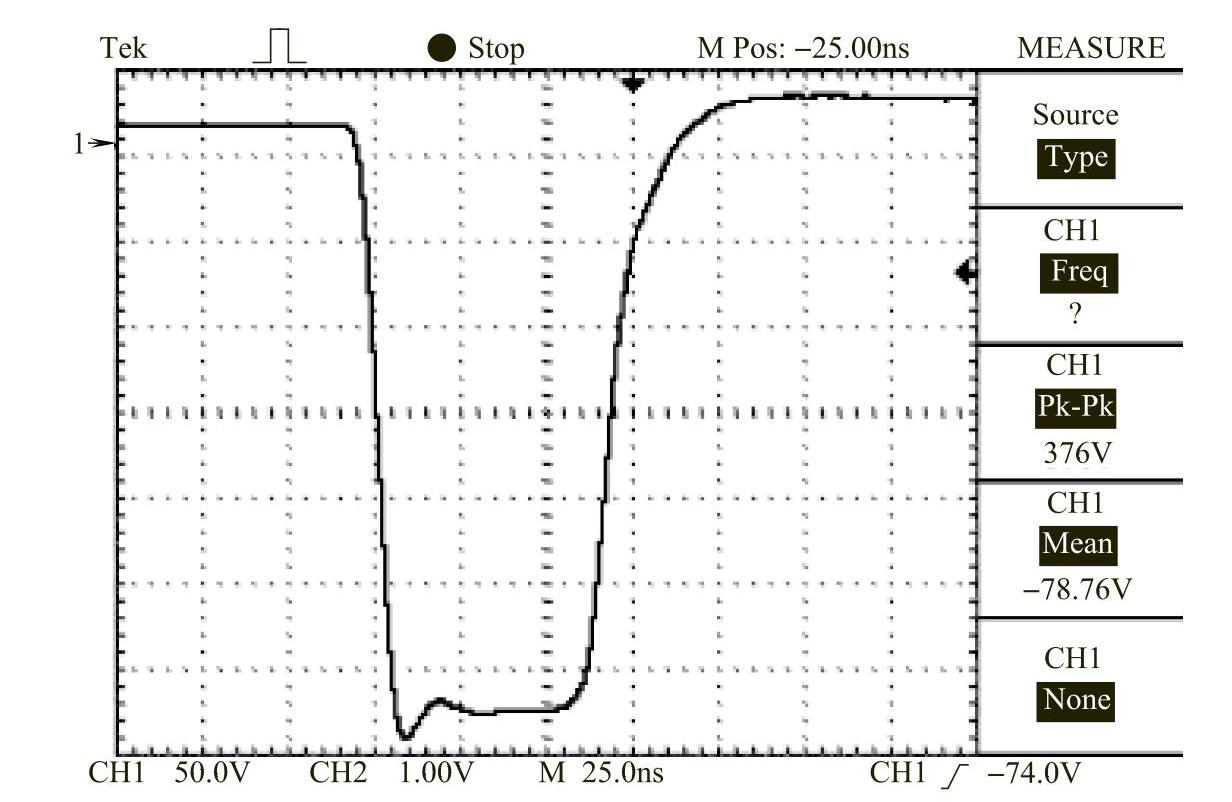

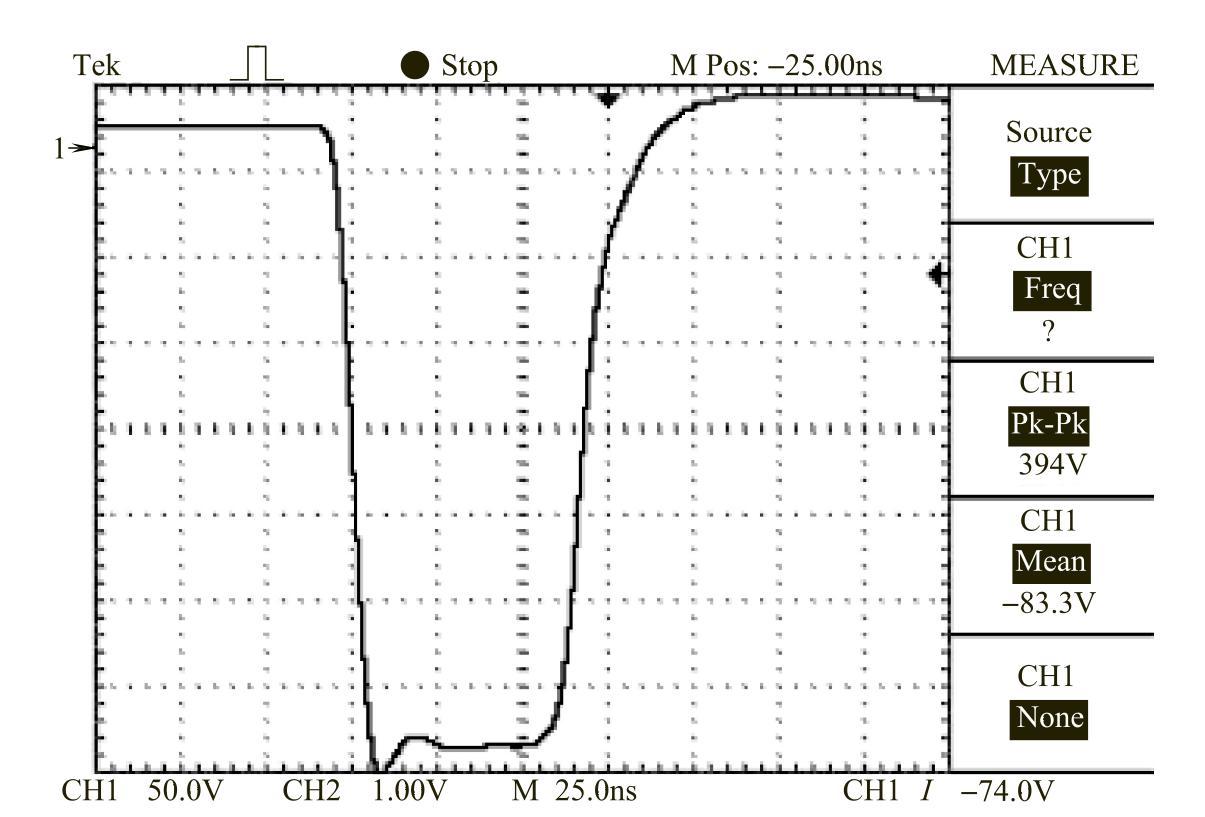

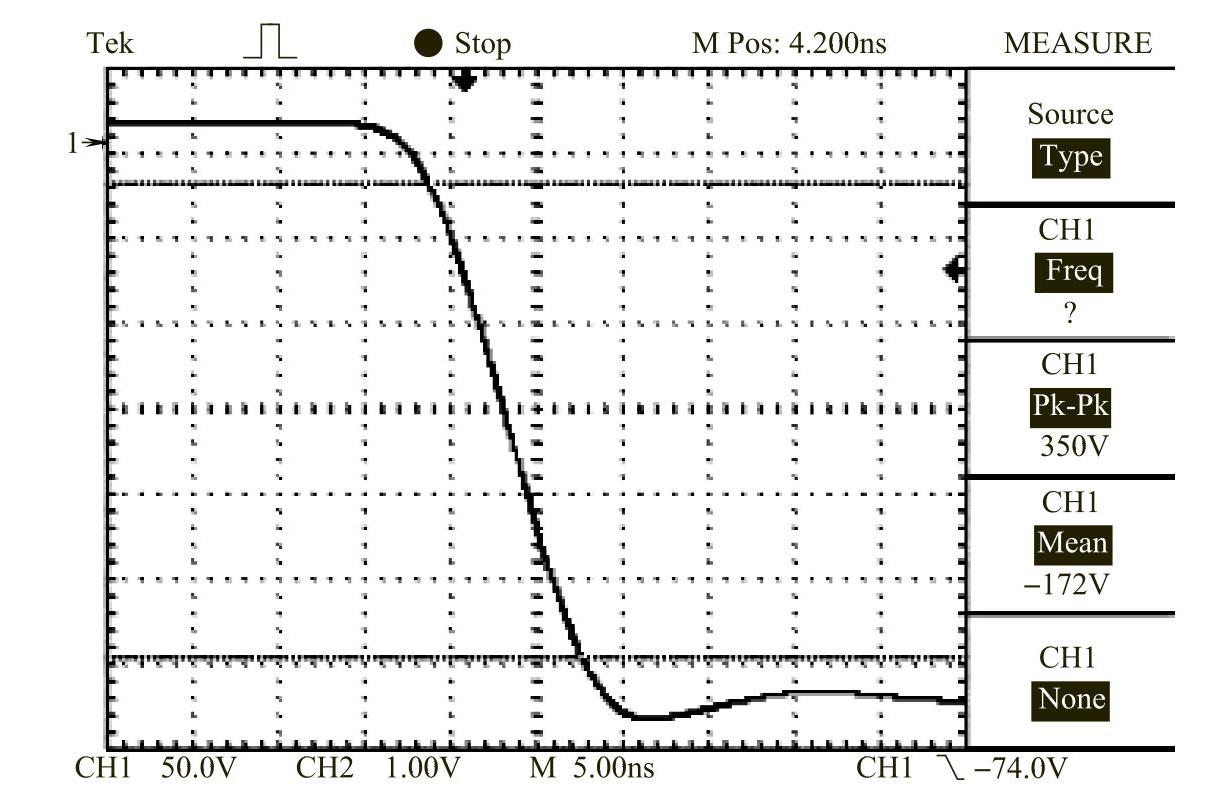

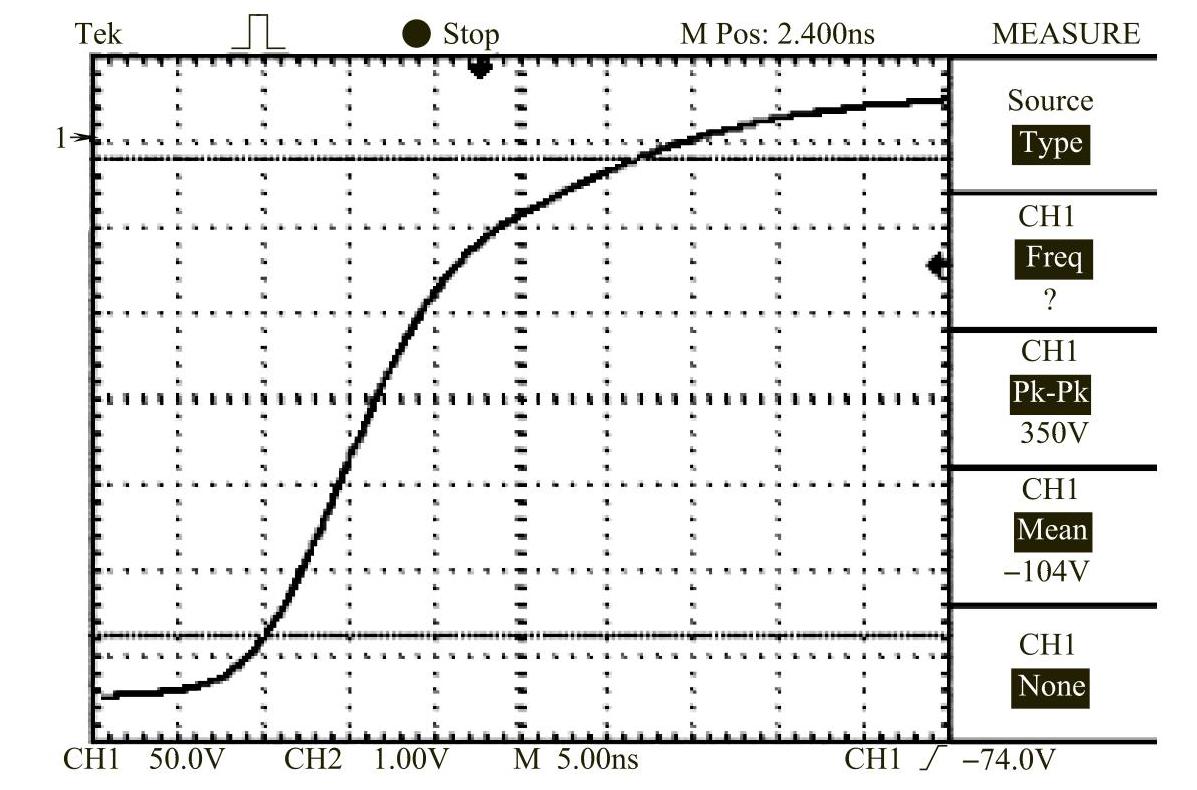

图3-48~图3-50分别对应了设计的电路原理图、MOSFET脉冲发生器和脉冲发生电路细节。电路元器件中的接地电阻由地阻抗的焊盘产生,带装线、配线和由此产生的电感在图中没有给出。MC74AC14由5V电源供电,MC33151由18V的电源供应。对脉冲发生器电路中的可变元器件最优化,以得到开关稳定性,最小脉宽和与50Ω负载匹配的速度。图3-51~图3-53给出了分别对应电压在200V、350V、400V的典型输出脉冲。图3-51中输出电压为194V,横轴为25ns/div,纵轴为50V/div,脉宽大约75ns,下降时间大约为10ns。图3-52中输出电压为376V,横轴为25ns/div,纵轴为50V/div,脉宽大约70ns,下降时间大约为10ns。图3-53中输出电压为394V,横轴为25ns/div,纵轴为50V/div,脉宽大约70ns,下降时间大约10ns峰值栅压为18V,可以看出50Ω匹配电路产生的脉冲有个很近似的矩形,而且没有振荡和过冲。在测试中,横轴从5ns/div增加到10ns/div、25ns/div和50ns/div。由于负载、输入阻抗等都与50Ω相匹配,当时间尺度被设定为以上的各种情况时,可以发现脉冲都没有脉冲反射现象。图3-54和图3-55分别给出了在输出350V、横轴为5ns/div的下降和上升时间细节图。10%~90%的下降时间是9ns,上升时间是22ns。

图3-50 有表面贴装无源器件的脉冲发生器电路细节

图3-51 输入电压为202V,负载为50Ω的输出电压响应波形

图3-52 输入电压为385V,负载为50Ω的输出电压响应波形

图3-53 输入电压为408V,负载为50Ω的输出电压响应波形

作出的所有的努力都是为了确保与建立的电波传输和工业标准化相兼容。任何无源负载都能很容易的补偿,与电路中50Ω源极阻抗相匹配。电路测试的结果表明它的表现和设计初衷一致,电路建立使用了宽带电路原型技术。50Ω的微带传输线用于减小电路电感和减小由于阻抗不匹配导致的信号失真。虽然电路拓扑保持不变,无源器件的值是不相同的,这样是为了建立限制值以保证在50Ω负载上有比较满意的波形。

图3-54 350V,50Ω负载的输出电压脉冲的下降时间图

图3-55 350V,50Ω负载的输出电压脉冲的上升时间图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。