根据前文分析,驱动信号分为4 组:垂直驱动信号、水平驱动信号、复位栅信号和电子快门信号。时序驱动信号使用FPGA 芯片实现各电路的同步时序控制,可以利用FPGA 上CCD 驱动程序的信号仿真结果与示波器采集的4 组驱动信号的波形特性进行对比分析,实现测试与实验。FPGA 上的CCD 驱动程序仿真结果如图16-22 所示。

图16-22 FPGA 上的CCD 驱动程序仿真结果

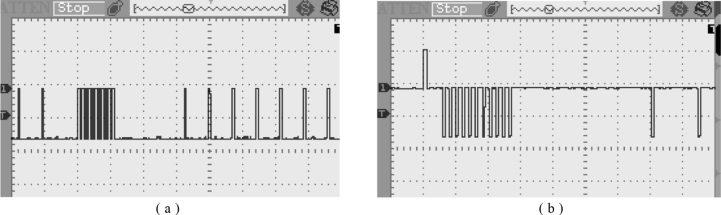

利用ATTEN 公司的ADS1102C 型示波器采集垂直驱动信号VΦ1 与VΦ2 的输出。如图16-23(a)、(b)所示中的左半部分属于启动周期,右半部分属于转移周期。对比FPGA 程序的仿真结果,在FPGA 中,VΦ1 的时序由XV2 控制,根据真值表,XV2 为高电平时VΦ1 为低电平,XV2 为低电平时VΦ1 为高电平,因此图16-23 所示示波器采集到的VΦ1 信号符合软件仿真结果。VΦ2 的时序由XV1 和XSG1 控制,当XV1 和XSG1 同时为低电平时,XΦ2 信号为12 V 高电平;当XSG1 为高电平、XV1 为低电平时,XΦ2 信号为0 V中电平;当XSG1 和XV1 均为高电平时,XΦ2 信号为-7 V 低电平。示波器采集到XΦ2 信号仿真结果。由于VΦ3、VΦ4 与VΦ1、VΦ2 相比仅在时钟上略有滞后,示波器采集到的输出图像基本相同。

图16-23 垂直驱动信号测试

(a)VΦ1;(b)VΦ2

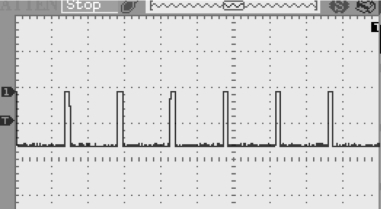

电子快门驱动信号SHT 的时序由XSHT 控制,当XSHT 为高电平时SHT 为低电平,XSHT 为低电平时SHT 为高电平。利用示波器采集电子快门驱动信号如图16-24 所示,对比仿真结果,电子快门驱动信号工作正常。

图16-24 电子快门驱动信号测试

由于水平驱动信号的频率远高于垂直驱动信号和电子快门信号,ATTEN 示波器无法采集到良好的信号波形,因此改用Agilent 示波器进行信号采集,水平驱动信号的采集结果如图16-25 所示。图16-25 中HΦ1 信号其消隐区极性为低电平,HΦ2 信号消隐区极性为高电平,与本设计在AD9979 芯片中的寄存器配置相符。将HΦ2 信号由消隐区向有效区转换的部分在时间轴放大,观察到其高电平约为3.5 V、有效区驱动信号周期约为18.6 ns,符合CCD 芯片所需的水平驱动信号的时序和电压要求。(https://www.xing528.com)

图16-25 水平驱动信号测试

(a)HΦ1;(b)HΦ2

图16-25 水平驱动信号测试(续)

(c)HΦ2 从消隐区到有效区特征

在有效区复位栅驱动信号RG 的频率与水平驱动信号相同,最高均可达到54 MHz,因此同样利用Agilent 示波器采集复位栅驱动信号,如图16-26 所示。复位栅驱动信号由AD9979 芯片产生,本设计根据CCD 图像传感器的需求,在AD9979 芯片的寄存器配置中将复位栅信号的占空比设置为1/4。根据图16-26 中采集到的RG 信号特性,可以发现复位栅信号的周期为18.4 ns,占空比约为1/4,符合复位栅驱动信号要求。

图16-26 复位栅驱动信号测试

根据以上驱动时序信号的测试结果,可以得出结论:驱动时序信号输出与预期相符,能够满足CCD 传感器的驱动需求。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。