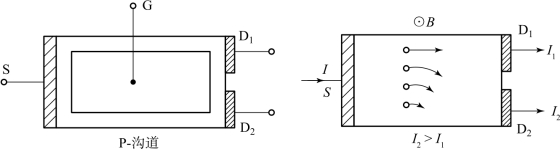

CMOS 磁敏器件是指具有两个漏极的MOS 管,称为分漏MOS 管,图8-7 所示为分漏磁敏MOS 晶体管工作原理。无磁场时两个对称分布的漏极流过相等的漏电流,垂直于器件表面的磁场不为零时,沟道中的载流子在洛伦兹力作用下,向其中一个漏极偏转,导致一个漏极电流增大,另一个漏极电流减小,两个漏极电流差与磁感应强度大小和方向有关,这种分漏MOS 管的乘积灵敏度可达104 V/(A·T),缺点是需要104 Ω 数量级负载电阻且稳定性较差。

图8-7 分漏磁敏MOS 晶体管工作原理图

CMOS 磁敏器件是由两个互补的分漏MOS 晶体管组成,用标准的硅栅工艺制备,克服了单个分漏MOS 管的缺点。在100 μA 电流下磁灵敏度可达1.2 V/T,相应于1.2 ×104 V/(A·T)乘积灵敏度,比一般霍尔器件高2 个数量级。

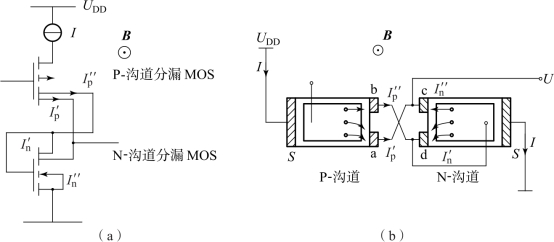

CMOS 分漏磁敏器件中,一个管为P -沟道增强型分漏MOS 管,另一个为N -沟道增强型分漏MOS 管,两个管子分漏电极互相交叉耦合连接,如图8-8(a)所示。有磁场垂直于器件表面指向纸外,N -沟道MOS 管的载流子空穴和N -沟道MOS 管的载流子电子,在洛伦兹力作用下的偏转方向如图8-8(b)所示。交叉耦合就是一个管子中电流增加的漏极与另一个管子中电流减少的漏极相连。

无外磁场作用时两个管子各自两个漏极的电流分别相等,输出电压为Uo 。当B 垂直于图面向外,漏极a 电流增大,a 与其源极之间电阻减小,电压降相应减小,使a 点电位升高,因而使输出端电位升高;同理,漏极c 电流减小,c 极与其源极间电压降增大,使输出端电位升高;此外,因b 极电位降低(因IP 变小,IN 变大),使N -沟道MOS 栅压降低,导致其两个漏极的电流都相应变小,进一步提高了输出端电位。CMOS 磁敏器件的输出电压对磁场敏感。(https://www.xing528.com)

图8-8 CMOS 磁敏晶体管工作原理图

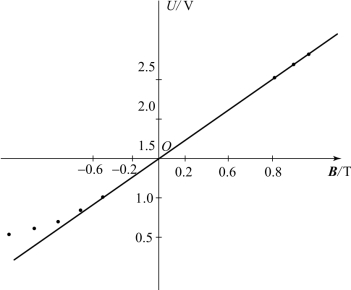

CMOS 磁敏管输出电压与磁感应强度的关系如图8-9 所示,在-0.3 ~+0.7 T 范围内有较好的线性。当电源电压由10 V 变为20 V 时,电流I 从0.1 mA 变为1 mA,磁灵敏度由1.2 V/T 变为1.4 V/T,说明电源电压对器件性能影响不大。

图8-9 CMOS 磁敏晶体管电压与磁感应强度关系

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。